Purpose

Use FPGA to realize the function of signal generator and generate a sine wave signal of a certain frequency

Master the principles of DDS

Learn to generate ROM IPCORE

Learn to emulate ROM IPCORE

experiment platform

Elf development board (DA module is connected to J4 port of the development board)

Black Gold DA Module (AN108)

QuartusII 11.0 (comprehensive compilation software)

Modelsim 10.1a (simulation software)

Debussy (waveform viewing software)

Waveform data generation software

Principle Analysis

First, we use the waveform data generation software to generate the waveform data of the sine wave. The FPGA can save the waveform data in the ROM, and then read it out from the ROM at a certain rate and send it to the DA interface. Through the digital-to-analog conversion of the DA module, the digital signal can be converted into an analog signal. Then the sine wave can be observed through the oscilloscope. The width of the waveform data is related to the data bit width of the DA module. The wider the bit width, the smoother the waveform, but the required storage space is also increased accordingly. The bit width of the DA module we selected is 8 bits, so the waveform data should also be 8 bits wide. The depth of the waveform data is 512. If we want to generate a 1Khz sine wave, the clock frequency of the ROM we read should be 512*1Khz. In this way, the data read from the ROM is sent to the DA module, and we can see a 1Khz sine wave signal on the oscilloscope. In our newly created routine, the clock for reading ROM is 50M, and the ROM depth is 512, so what is the frequency of the sine wave signal generated in the end?

Source code display

`timescale 1ns / 1ps

module dds(

input clk ,//fpga clock

output daclk ,

output [7:0] dadata //DA data

);

reg [8:0] rom_addr = 0;

wire [7:0] rom_data ;

assign dadata=rom_data; //DA outputs the data from ROM

assign daclk=clk;

//DA output sin waveform

always @(negedge clk)

begin

rom_addr <= rom_addr + 1'b1;

end

rom Urom (

.clock (clk ), // input clka

.address (rom_addr ), // input [8 : 0] addra

.q (rom_data ) // output [7 : 0] double

);

endmodule

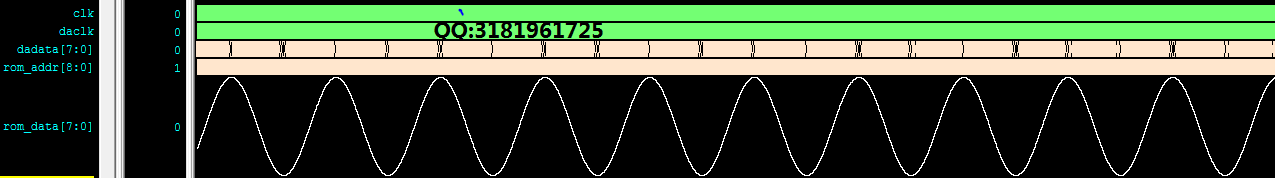

Simulation waveform

Experimental phenomena

Engineering Structure

Project (Quartusii project)

Source (Verilog source code)

Sim (Simulation Engineering)

Doc (Related Documentation)

doubt

Many friends may ask, why no waveform comes out when I simulate this project directly? If the source code is provided by me, and the simulation test stimulus file is also provided by me, then theoretically it is completely possible to simulate the waveform, but there is no waveform. The problem lies in the ROM IPCORE. If we want to use Modelsim to simulate a project with IPCORE, then we first need to compile the device library we use with Modelsim once to generate a library file that Modelsim can recognize. This is the first step to use Modelsim to simulate a project with IPCORE. If you use Quartusii to simulate IPCORE, you do not need to compile it again (but versions after QuartusII 9.0 no longer have simulation functions, and they are all simulated with third-party software). Similarly, if you are using Xilinx chips, then you do not need to compile the device library when using ISE or Vivado to simulate a project with IPCORE. I will write a blog specifically for the simulation steps of ROM IPCORE. You can read the next blog with this question, and I believe you will definitely gain something.

Conclusion

Through today's study, we should master the principles of DDS and how to call ROM IPCORE. Due to space limitations, the specific engineering details will not be described here. If you have any questions, you can contact me to request a video tutorial for the course. Thank you!

Video tutorial link: https://pan.baidu.com/s/1LRPfsNM0fr9wf48C5yHUBg

Extraction code: 18ua

Previous article:[Operational Amplifier] Franco Notes - Signal Generator - Triangle Wave Generator

Next article:How to understand the sampling rate of an oscilloscope (ADC)?

- Popular Resources

- Popular amplifiers

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- In what situations are non-contact temperature sensors widely used?

- How non-contact temperature sensors measure internal temperature

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

- CGD and Qorvo to jointly revolutionize motor control solutions

- CGD and Qorvo to jointly revolutionize motor control solutions

- Keysight Technologies FieldFox handheld analyzer with VDI spread spectrum module to achieve millimeter wave analysis function

- Infineon's PASCO2V15 XENSIV PAS CO2 5V Sensor Now Available at Mouser for Accurate CO2 Level Measurement

- Advanced gameplay, Harting takes your PCB board connection to a new level!

- Advanced gameplay, Harting takes your PCB board connection to a new level!

- A new chapter in Great Wall Motors R&D: solid-state battery technology leads the future

- Naxin Micro provides full-scenario GaN driver IC solutions

- Interpreting Huawei’s new solid-state battery patent, will it challenge CATL in 2030?

- Are pure electric/plug-in hybrid vehicles going crazy? A Chinese company has launched the world's first -40℃ dischargeable hybrid battery that is not afraid of cold

- What is the architecture diagram of Narrowband Internet of Things (NB-IoT) technology?

- My Electronic Games Sharing "Three Wars Electronic Games"

- Interaction issues between STM32F429 and AD7606

- TMS320VC33 FLASH online programming method

- Allwinner V853 heterogeneous AI intelligent vision development board evaluation - libgpg-error error solution

- Will Ultra-Wideband (UWB) really be popular in the future?

- 【Perf-V Evaluation】+ Construction and basic use of development environment (2)

- Understanding Metastability

- Has anyone tried the GD32E230 board?

- Very detailed introductory article FPGA_SOPC_starter.pdf

EL2411CN

EL2411CN

京公网安备 11010802033920号

京公网安备 11010802033920号