AD9959 application control circuit

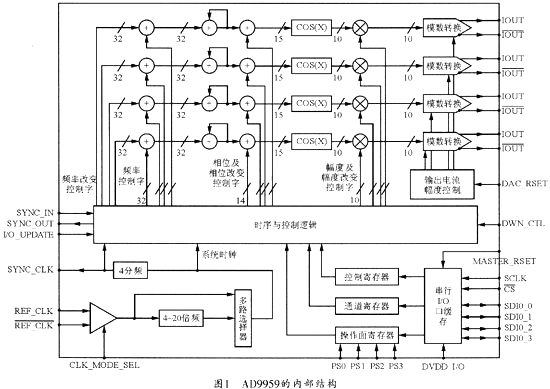

AD9959 can achieve up to 16 levels of frequency, phase and amplitude modulation, and can also work in linear frequency modulation, phase modulation or amplitude modulation mode. The application range of AD9959 includes phased array radar/Luna system, instrumentation, synchronous clock and RF signal source. The internal structure of AD9959 is shown in Figure 1. The main features are as follows:

◇There are 4 DDS channels with 10-bit DAC, and the maximum sampling frequency is 500 MSPS;

◇Channel isolation greater than 65 dB;

◇32-bit frequency resolution;

◇14-bit phase offset resolution;

◇10-bit output amplitude scalable resolution;

◇Serial I/O port (SPI) with enhanced data throughput;

◇ Software/hardware control can be used to reduce power consumption;

◇Dual power supply (DDS core 1.8 V, serial I/O 3.3 V);

◇Built-in multi-device synchronization function;

◇Built-in clock frequency multiplication phase-locked loop (4 to 20 times frequency multiplication).

2 AD9959 Pin Functions

AD9959 adopts 56-pin LFCSP package, and the function definition of each pin is as follows:

SYNC_IN: Input pin, which can synchronize multiple AD9959s. It should be connected to the SYNC_OUT of the main AD9959 when in use;

SYNC_OUT: Output pin, which can synchronize multiple AD9959s. When used, it should be connected to the SYNC_IN of the slave AD9959.

MASTER_RESET: reset input pin, high effective;

PWR_DWN_CTL: external power supply power-down control pin;

AGND: analog ground;

DVDD: digital power supply (1.8 V);

DGND: digital ground;

DAC_RSET: Input pin, which can set the reference current for DAC. When used, it should be grounded through a 1.91 kΩ resistor;

REF_CLK and REF_CLK: reference clock or oscillation input (complementary input). If single-ended input is used, a 0.1μF decoupling capacitor should be connected from the REF_CLK pin to AVDD or AGND.

CLK_MODE_SEL: Oscillator control pin. When connected to a high level, the voltage should not exceed 1.8 V. When connected to a low level, the oscillator is bypassed.

LOOP_FILTER: Input terminal. When used, a zero resistor and a 680 pF capacitor should be connected in series to the nearest AVDD pin (Pin28).

I/O_UPDATE: Input pin. The rising edge of this pin can send the data content of the serial port buffer to the activated register. The I/O_UPDATE signal should be synchronized with the SYNC_CLK signal and must meet the requirements of setup time and hold time.

CS: chip select serial port enable signal terminal, low effective;

DVDD_I/O: 3.3 V digital power supply;

SYNC_CLK: clock output, 1/4 of the internal clock, used to synchronize I/O_UPDATE signals;

SCLK: I/O serial operation clock input terminal, data is written on the rising edge of this terminal and data is read on the falling edge;

SDIO_0: bidirectional pin, used for data input and output of serial operation;

SDIO_1:3: Bidirectional pins, used for serial operation data input and output, and can also be used to control the slope of the DAC output amplitude;

P0~P3: Input pins, these four pins are used to control the selection of modulation mode, the switch of the scanning accumulator or the rise and fall slope of the output amplitude. The change of any one of the four pins is equivalent to the rising edge of an I/O_UPDATE signal. This end must be synchronized with the SYNC_CLK signal and must meet the requirements of setup time and hold time;

CH0_IOUT ~CH3_IOUT, CH0_IOUT ~CH3_IOUT: output pins, complementary output ends of the four channels. When in use, a pull-up resistor must be connected to AVDD.

3 Working mode combinations

The four channels of AD9959 can realize multiple working modes at the same time. However, in some modes, several data pins are needed to realize special functions, which limits the combination. According to the resources of AD9959 chip, the working mode combinations that can be realized at the same time are as follows:

(1) The four channels can realize any combination of single frequency mode, 2-level modulation mode and linear scanning mode. Each channel can work in one of these three modes.

(2) One or two channels can work in 4-level modulation mode at the same time, and the remaining channels can work in single-frequency mode;

(3) One channel can work in 8-level modulation mode, and the remaining channels can work in single-frequency mode;

(4) One channel can work in 16-level modulation mode, and the remaining channels can work in single-frequency mode;

(5) In single frequency mode, the output amplitude slope of each channel can be controlled;

(6) When the P2 and P3 pins are used to control the output amplitude slope, any two channels can work in 2-level modulation mode or linear frequency modulation or phase modulation mode at the same time;

(7) When the P3 pin is used to control the output amplitude slope, one channel can work in 8-level modulation mode and the remaining channels can work in single-frequency mode;

(8) When the SDIO_1 to SDIO_3 pins are used to control the output amplitude slope, the four channels can realize various combinations of 2-level modulation modes, while the channels not used for 2-level modulation mode can operate in single-frequency mode;

(9) When the SDIO_1 to SDIO_3 pins are used to control the output amplitude slope, one or two channels can work in 4-level modulation mode at the same time, and the remaining channels can work in single-frequency mode;

(10) When the SDIO_1 to SDIO_3 pins are used to control the output amplitude slope, one channel can operate in 16-level modulation mode and the remaining channels can operate in single-frequency mode;

(11) Amplitude modulation, linear amplitude sweep and output amplitude slope control functions cannot be implemented simultaneously, but frequency and phase modulation can be implemented simultaneously with the output amplitude slope control function.

4 Serial Operation

The four channels of AD9959 can share a set of register addresses. This address sharing mechanism allows the same data to be written to the configuration registers of the four channels at the same time. When different settings are required for the four channels, the data set for each channel can be written independently by setting the channel enable bit.

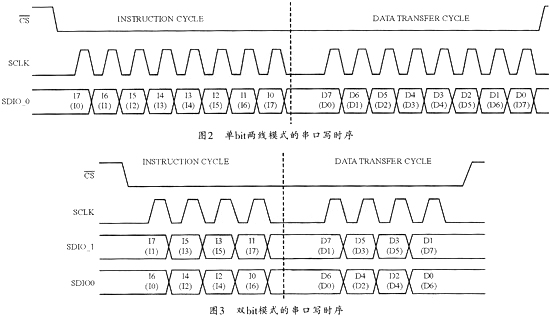

A serial communication cycle is divided into two stages: the instruction cycle and the data read and write cycle. First, the 8-bit instruction word of the instruction stage is transmitted, corresponding to the 8 rising edges of SCLK, and then the 1 to 4 bytes of data set by the instruction are read and written, and then the next instruction cycle is waited for.

The serial port operation of AD9959 is basically the same as the DDS chip previously launched by ADI. However, since AD9959 has four serial data pins (SDIO_0:3), its programming has greater flexibility. By configuring the corresponding registers, there are four programming modes for serial I/O operation, namely single-bit two-wire mode, single-bit three-wire mode, double-bit mode and four-bit mode.

When set to single-bit two-wire mode, SDIO_0 is a bidirectional data pin. When set to single-bit three-wire mode, SDIO_0 is a data input pin and SDIO_2 is a data output pin. In both modes, SDIO_3 is used as a serial port synchronization recovery signal pin, and a positive pulse is used to restore the serial port to the initial waiting instruction state. Figure 2 shows the serial port write timing in single-bit two-wire mode.

When set to dual-bit mode, SDIO_0 and SDIO_1 are used as bidirectional data pins at the same time, and two bits of data are transmitted in each SCLK cycle. In this way, only four SCLK cycles are needed to transmit an eight-bit data message, and SDIO_3 is still used as the serial port synchronization recovery signal. Figure 3 shows the serial port write timing in dual-bit mode.

When set to four-bit mode, SDIO_0:3 can be used as a bidirectional data pin at the same time, transmitting four bits of data per SCLK cycle, so only two SCLK cycles are required to transmit an eight-bit data message.

5 Application in radar intermediate frequency signal simulator

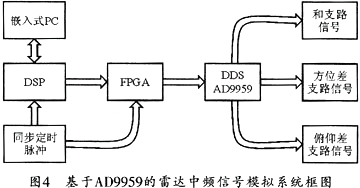

The design of modern radar signal simulators focuses on the use of digital methods. In fact, with the development of real-time digital signal processing technology, the PC+DSP+DDS architecture has become the main way to implement radar signal simulators. Since AD9959 integrates four DDS channels on one chip, the use of AD9959 can greatly facilitate the design of multi-channel radar signal simulators. Because it can make the system that originally required multiple single-channel DDS chips now only need one AD9959 to complete the system function.

Figure 4 shows a three-channel design structure block diagram of a radar intermediate frequency signal simulation system based on the AD9959 chip. The signal simulation process is as follows: the embedded PC first models and calculates the target and environment to generate a radar signal simulation database, and then the DSP calculates the corresponding signal frequency, phase and amplitude data that the DDS needs to generate at different times based on the target information transmitted by the embedded PC. The data is then transmitted to the FPGA, which then performs parallel-to-serial conversion on the data and writes the data serially to the DDS at a specific time under the triggering of the synchronous timing pulse, thereby completing the setting of the DDS. Finally, the DDS generates three intermediate frequency analog signals at the same time.

6 Conclusion

Since AD9959 has multiple DDS channels integrated inside, it does not need multiple single-channel DDS chips and their external circuits, which helps to simplify the system design process and reduce the PCB area. Actual test results prove that AD9959 has high performance and can be widely used in radar and communication systems. This site also has AD9959 configuration program and application circuit, please search.

Previous article:AD590 temperature measurement circuit

Next article:ADC0809 Application

- Popular Resources

- Popular amplifiers

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

- CGD and Qorvo to jointly revolutionize motor control solutions

- CGD and Qorvo to jointly revolutionize motor control solutions

- Keysight Technologies FieldFox handheld analyzer with VDI spread spectrum module to achieve millimeter wave analysis function

- Infineon's PASCO2V15 XENSIV PAS CO2 5V Sensor Now Available at Mouser for Accurate CO2 Level Measurement

- Advanced gameplay, Harting takes your PCB board connection to a new level!

- Advanced gameplay, Harting takes your PCB board connection to a new level!

- A new chapter in Great Wall Motors R&D: solid-state battery technology leads the future

- Naxin Micro provides full-scenario GaN driver IC solutions

- Interpreting Huawei’s new solid-state battery patent, will it challenge CATL in 2030?

- Are pure electric/plug-in hybrid vehicles going crazy? A Chinese company has launched the world's first -40℃ dischargeable hybrid battery that is not afraid of cold

- How to obtain high-frequency equivalent models of devices such as varistors and TVS transient diodes

- MicroPython uses the new neopixel driver

- Review Weekly Report 20220509: Saifang RISC-V Linux Starlight Board is coming, how is the Xianji 800MHz HPM6750 tested?

- How to set default rules for Altium drawing?

- Matlab and Modelsim co-simulation error

- Recruitment of assistant engineers

- ST NUCLEO-G071RB evaluation application - Come and experience the new generation of entry-level 32-bit STM32, giving you the best cost-effective experience

- Security innovation, a new verification method. Download Fujitsu's "Spectrum Verification Solution" white paper and get a gift!

- Which forum member has a deeper understanding of MOS tubes? I usually overlook some parameters when reading the specification, and I want to understand them all today. Know...

- How to configure the SSH service of Win10 Linux subsystem

ALS1704ASA

ALS1704ASA

京公网安备 11010802033920号

京公网安备 11010802033920号