In recent years, the market demand for mobile communications has grown rapidly, and current mobile communication systems can already use mature signal processing technology to obtain higher information transmission rates. The design difficulty of the next generation of wireless systems will increase, mainly in terms of support for multiple standards and reconfigurability. Different communication standards vary greatly in terms of center frequency, signal bandwidth, signal-to-noise ratio, and linearity. This has a significant impact on the design of all radio frequency (RF) front-end building blocks, and a comprehensive trade-off analysis must be performed to select the best architecture and choose appropriate design specifications for individual circuit modules.

RFIC Design Challenges

The complexity of digital signal processing is steadily increasing. Digital blocks are able to partially compensate for signal impairments introduced by analog front-end blocks. To fully verify the complex digital compensation algorithms and the effects of analog non-idealities such as phase noise, nonlinearity, and mismatch, digital and analog blocks must be co-verified. The bottleneck for achieving RF/baseband co-design is the high-GHz RF carrier signal present at the RF front end. In order to simulate the bit error rate (BER) and packet error rate (PER) of a complete communication link at the transistor level, the modulated signal must be run for thousands of cycles, which is very expensive or even impossible.

In addition to performance verification of the actual design to confirm the design specifications, another key requirement is functional verification of the entire chip. Implementation errors in the interface between the digital control circuit (responsible for enabling various operating modes such as power-on, power-off, reception, transmission, and band selection) and the analog front end are a major cause of design rework.

IC design engineers usually adhere to the budget requirements set by system designers. They may be able to prove that looser IC design specifications can also meet system-level design requirements, but in the absence of theoretical verification, it is unnecessary to spend a lot of time optimizing circuits. Because different expertise and tools are required, baseband and analog/RF are usually designed, simulated, and verified separately. The main goal of system-level design is to find a suitable algorithm and architecture to achieve the required functions and performance at the lowest cost.

However, in the actual physical implementation stage, RFIC design engineers still face many severe challenges. Take wireless transceivers as an example. The high signal transmission rate makes the circuit very sensitive to parasitic effects (including parasitic inductance and noise). Therefore, the essence of the RFIC design process is to manage, replicate and control post-layout simulation and its effects, and use this information efficiently throughout the design process.

RFIC design also requires design engineers to have professional and unique analysis techniques in the RF field. The selection of these analysis methods across frequency domain and time domain depends on the circuit type, the technical level of the design engineer, the circuit size or the design style. In order to facilitate the selection, it is necessary to use simulation methods to provide a seamless integrated environment.

In the field of RFIC design, integration is also a general trend. In the past, RFIC was regarded as a relatively independent design field. Now, many RFICs include ADC, DAC and PLL functions, as well as digital synthesizers created in a digital design environment and integrated into the chip. On the other hand, RF modules are also being added to large SoCs to achieve single-chip solutions. The use of system-level packaging (SiP) can also integrate other functions. Like RFIC and SoC design methods, the use of SiP technology will also face similar verification issues.

A comprehensive design solution must be able to address these challenges, including:

1. Provide a comprehensive link between system-level design and IC implementation;

2. Perform IC verification in a system-level environment to fully leverage existing wireless cell libraries, models, and test benches;

3. Support full-chip mixed-level simulation at different abstraction levels;

4. Perform detailed analysis at chip and module levels within optimized simulation time;

5. All parasitic effects can be managed and simulated;

6. Provide layout automation at appropriate design points;

7. Supports passive device modeling at multiple levels throughout the design process.

All of the above requirements must be met in a single design environment, which not only facilitates RFIC design work, but also facilitates integration with analog/AMS and digital design. At multiple levels of abstraction (including chip level and module level), the design can be iterated back and forth to facilitate verification/implementation independently of the physical implementation strategy. [page]

Wireless RFIC Design Flow

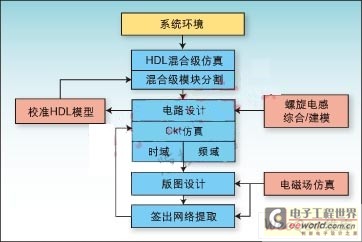

The wireless RFIC design process is shown in Figure 1. This process covers the entire process from system design to physical implementation, which is consistent with the "from both ends to the middle" design method mentioned earlier.

Figure 1: Wireless RFIC design flow

1. Use system-level resources

The assurance from the system design process is the first and highest level of abstraction. The system-level design description can be used as an executable test environment for the top-level chip. The model of the peripheral system can be combined with the high-level model of the chip to generate an executable design specification. The system design requirements can be used as the earliest design specifications to drive the chip-level design requirements, and eventually become reusable test benchmarks and regression simulation models. Some system-level IP resources can also be used to determine the performance parameters of the system (such as EVM, BER, and PER).

Mixed-level simulation helps to share information between system and module design engineers. In order to ensure the interface between the system environment and the IC environment, the multi-mode simulation solution must be suitable for any language (including C/C++, SystemC, SystemVerilog, digital/mixed signal/analog behavioral HDL language and SPICE), and can provide different dedicated engines and algorithms for cross-multi-mode circuit design.

2. Design planning and simulation strategy

The success of a complex design depends largely on the thoroughness of pre-planning. If there is a clear plan for the top-level requirements, module-level requirements, and hybrid-level strategies of the design at the beginning of the design, the "from both ends to the middle" design approach can ensure that all modules can meet the main design specification requirements and allow for more flexible scheduling. Therefore, a comprehensive simulation strategy and modeling planning are critical. After successfully achieving high-level executable specifications, the design process will go deep into certain specific areas of interest in the design and develop verification plans for the areas of interest. The verification plan will specify how the test is performed and determine which modules are at the transistor level in the test. Engineers should be careful not to over-complicate when setting up and writing model code. Only simple models and necessary model features are required at the beginning.

A formal planning process is a prerequisite for efficient and comprehensive verification, which helps to catch more design errors in the early stages of design and reduce the number of design iterations. Simulation and test plans can be used for high-level system descriptions at the beginning, which can quickly achieve debugging. After verification, they will be used for mixed-level simulation of modules to reduce the risk of errors in the later stages of the design cycle.

3. Multi-mode simulation environment

The top-down design process begins with HDL modeling of the RFIC with a system-level testbench. This includes all RF blocks, as well as any analog and/or digital blocks. The first step is to perform behavioral modeling of the full chip in a top-level testbench and perform some system tests (such as EVM and BER). This verifies the block partitioning of the IC design, the block functionality, and the desired performance characteristics. This behavioral model serves as the basis for mixed-level simulation, where any block can be inserted at the transistor level and verified in the top-level environment. In addition, the full-chip and system-level settings can be used as a regression template and continuously verified as the blocks mature, providing an evolving design approach to the entire design process. With this approach, a large number of problems can be discovered early in the design process and sufficient time can be guaranteed to resolve them. At the same time, different blocks can be developed in parallel at their own pace.

Throughout the simulation environment, the same circuit has different analysis views, which may include behavioral level views, pre-layout transistor level views, and multiple views of parasitic effects. As the module matures, more transistor-level information needs to be added to test RF/analog interfaces and RF/digital interfaces. At the same time, a mixed-signal simulator is needed to handle analog, digital, and RF descriptions, and to mix behavioral and transistor-level abstractions. Selecting the appropriate view for each module or submodule, managing runtime and accuracy, and making trade-offs between the two can be achieved through simulation options, such as importing transistors into a fast Spice simulator or keeping transistors in full Spice mode. This configuration is highly dependent on the sensitivity of the circuit and interface. Since these configurations need to be reused, it is important to manage them efficiently. This also provides a very effective mechanism to establish continuous regression verification that supports ACD. [page]

4. Module circuit design

Next, we start the preliminary design of the circuit, starting with a circuit study and understanding the performance specifications. This early study helps form the top-level layout plan, which is very sensitive to noise and module-level interconnects for RFICs. At this stage, we can try to synthesize passive components such as spiral inductors to meet the specifications and make the initial layout on the chip. Two important tasks can be performed at this stage: create early models for spiral inductors and use them for simulation before the module-level layout is completed; and perform initial analysis of the mutual inductance between spiral inductors. Device models can be created for all inductors at this stage for simulation.

Simulation can be performed in the method preferred by the designer, either frequency domain or time domain simulation, and the designer should consider the circuit characteristics, simulation type and simulation amount before making a decision. A single process design kit and supporting design environment can help designers choose the appropriate simulation algorithm. Results can be displayed in an appropriate manner based on the simulation type. When the block-level circuits are completed, designers can use behavioral incentives and descriptions of peripheral chips in a top-level environment to verify these circuits.

5. Physical Implementation

Layout design automation functions (automatic routing, connectivity-driven and design rule-driven layout design and placement, etc.) are very efficient. Due to the close integration of schematics and design constraint rules, layout design automation can greatly improve work efficiency. The router can solve the routing problems of differential pairs and shielded lines, and supports manual setting of routing constraints for each trace. This makes the physical design process as repeatable as the front-end design process. Although it takes some time to set up these tools in the early stages, they are reusable in subsequent design processes.

6. Parasitic Parameter Extraction

After the layout is completed, electromagnetic field simulation (EM) can generate high-precision models for passive components. For example, several spiral inductors can be selected as key objects for EM simulation by replacing some models that have been created during the design process with spiral inductors, mixing and matching existing models. Design engineers need to fully monitor the modeling process of spiral inductors and weigh the run time and accuracy.

Net-based parasitic extraction is the most important part of the design process after the layout appears. RF design is very sensitive to parasitic effects. Since the designer can have relevant parasitic information about any area, trace or module, it becomes more important to manage the information of different levels of parasitic parameters. Insensitive traces only need RC parameters, while sensitive traces need RLC parameters. Traces with spiral inductors can be extracted in the form of RLC and inductance parameters, and even substrate effects can be added to the most sensitive traces. At the same time, these traces can be mixed and matched with device models of passive components.

When the top-level layout is implemented, noise analysis (especially substrate noise analysis) can ensure that noisy circuits (such as digital logic and PLL) do not affect highly sensitive RF circuits. Designers can check this, and if the circuit area of concern is affected, the designer can modify the layout plan or add protection bands around the noisy circuit. However, it is often unrealistic to simulate the entire circuit at the transistor level or include all parasitic information. One solution is to extract the behavioral model, but this will ignore the parasitic effects of the connections between different modules, so it is necessary to support hierarchical extraction capabilities and parasitic parameter extraction of the connections between design modules.

7. Calibrating the HDL Model

After the module is developed, the initial behavioral model can be back-annotated according to key circuit performance parameters, which can achieve more accurate HDL-level simulation. Although not applicable to all effects, this method can obtain more accurate performance information at a lower runtime cost, and can speed up verification and reduce the workload of full transistor-level verification.

There are three steps to verifying a module using mixed-level simulation. First, include an idealized module model in the system-level simulation when verifying the module's functionality. Then, replace the idealized model with the module's netlist to verify the module's functionality. This will detect the impact of module defects on system performance.

Finally, the module netlist is replaced with an extracted model. By comparing the simulation results of the netlist and the extracted model, the functionality and accuracy of the extracted model can be verified. Using the verified extracted model instead of the ideal model in the subsequent mixed-level simulation of other modules can effectively improve its effectiveness.

If done properly, bottom-up verification can achieve more detailed verification of large systems. Because the details of the physical implementation are removed and only the behavioral details are retained, behavioral simulation is very fast. As the module matures, the behavioral model generated by the bottom-up verification process becomes more and more useful and can be used for third-party IP verification and reuse.

For wireless systems including RF front-ends, the bottom-up verification process is an inevitable method to verify the performance of large systems. As mentioned earlier, transistor-level RF system verification requires running the modulated signal for thousands of cycles, which is often unrealistic. Replacing traditional transient simulation with advanced envelope analysis technology can only increase the simulation speed by 10 to 20 times. Even if traditional passband models are used for bottom-up extraction technology, the simulation speed cannot be increased to a satisfactory level because the RF carrier frequency still exists. Only by combining bottom-up model extraction technology with complex baseband or low-pass equivalent models can the carrier signal be effectively suppressed and the simulation time is sufficient to achieve full chip-level packet error rate analysis.

Generating behavioral models for all modules is a time-consuming and laborious task, and only a few design engineers have this expertise. Automated tools and methodologies can generate detailed behavioral models based on specific application and technical needs, with proven accuracy and open APIs to modify existing templates.

Previous article:Reducing CPLD Power Consumption in Embedded Design

Next article:How to Build a Doppler Measurement System Using DSP and FPGA

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Help! UC2842 flyback power supply output problem

- Vicor engineers invite you to talk about efficient power supply

- What material is the magnetic ring made of? Just look at the color!

- Sinlinx A33 development board boa and CGI transplantation

- Making a CPU out of a bunch of switches?

- [TI recommended course] #Amplifier design in test and measurement#

- Problems with using printf to print floating point numbers in a single chip microcomputer

- It is easy to travel around the world on your own, travel around the world, live in Korea, live in Korea, travel to the world, travel to the world, move to the top 2.4mm + reach the destination...

- To: Test Engineers! More than 2000 connectors, download a complete 96-page catalog at once!

- Let’s take a look at the performance of this RISC-V MCU with a main frequency of 648M.

A Practical Tutorial on ASIC Design (Compiled by Yu Xiqing)

A Practical Tutorial on ASIC Design (Compiled by Yu Xiqing)

京公网安备 11010802033920号

京公网安备 11010802033920号