The digital message stream in digital communication always uses several code elements to form a "word", and several "words" to form a "sentence". Therefore, when receiving these digital streams, it is also necessary to know the start and end times of these "words" and "sentences", and generate a timing pulse sequence consistent with the start and end times of the "words" and "sentences" at the receiving end, which is collectively called group synchronization or frame synchronization. The detection of frame synchronization can generally be completed using correlation detection technology. In the past, the rate in data communication was not very high, and the problem of correlation detection was easy to solve, but the trend of increasingly high-speed digital communication has posed new challenges to correlation detection in real-time. In fact, many high-speed data transmission systems, such as relay satellite communication systems, require higher and higher transmission data rates between user satellites and ground stations, reaching hundreds of megabits or even gigabits. It is even more difficult to process data in real time under such a high-speed environment.

PSK modulation has been widely used in the field of communications, but there is a phase ambiguity problem, which can generally be solved by differential coding. Although this method is simple, it requires adding an independent differential coding circuit at the transmitting end and a differential detection circuit at the receiving end. There are also some methods that do not require adding a differential coding circuit separately, such as combining the Viterbi decoding process at the receiving end to complete the estimation of the phase ambiguity value and then perform phase recovery. However, this process has a complex algorithm and is relatively time-consuming.

This paper not only studies the frame synchronization problem of 8PSK signal under high-speed conditions, but also estimates its phase ambiguity value. Mainly relying on the parallel structure, the traditional frame synchronization method is simplified and improved, so as to complete the above two tasks at the same time. And the algorithm is implemented on FPGA to verify the effectiveness of the algorithm.

1 Traditional frame synchronizer structure and synchronization detection algorithm

In the past, there have been many studies on frame synchronization technology. The most common frame synchronization method is to periodically insert a fixed-length frame synchronization code at the beginning of a frame. This structure usually uses the method of calculating the correlation between the received symbol sequence and the local synchronization code sequence to detect frame synchronization.

For one-dimensional signals, such as BPSK modulated signals, the correlation operation can usually be implemented with a simple XNOR gate. The bit stream to be detected is XNORed with the corresponding bit of the local synchronization code sequence, and then added bit by bit. The frame synchronization and phase ambiguity value can be detected based on the size and sign of the sum. Although this method is simple, it cannot adapt to the frame synchronization detection and phase ambiguity value estimation of two-dimensional signals such as MPSK, so its application range is relatively narrow.

2 Implementation of Phase ambiguity estimation Frame synchronization detection algorithm

The frame synchronization detection algorithm that can achieve phase ambiguity estimation consists of two parts:

(1) Correlation operation is performed between the data to be detected and the local synchronization code;

(2) The correlation value is compared with the threshold, and the corresponding peak pulse and phase ambiguity value are given according to the comparison structure.

The following takes 8PSK signal as an example to introduce in detail the relevant algorithms and decision methods that can simultaneously achieve two-dimensional signal frame synchronization and phase ambiguity estimation.

2.1 Related Algorithms

Since the 8PSK signal is a two-dimensional signal, the symbol sequence to be detected can be represented by aiejφi-Ii+jQi,i=0,1,2,…,N-1. Where ai is the amplitude of the i-th data; φi is its phase; N is the length of the frame header code element; Ii, Qi represent its real part and imaginary part respectively. The local synchronization code sequence can be represented by miejθi=i0i+jQ0i,i=0,1,2,…,N-1, where: mi is the amplitude of the i-th synchronization code; θi is its phase; I0i, Q0i represent its real part and imaginary part respectively. This paper selects the M sequence as the synchronization code, and maps 0 and 1 to the relative 0 phase and 4 phase in 8PSK respectively; then 8PSK modulation is performed. If the code element in the frame header is wrong (from 0 to 1, or vice versa), its phase will deviate by 180°, that is, from aiejφi to aiej(φi+π).

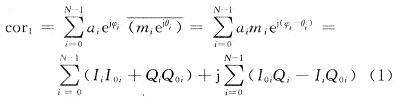

The correlation value between the symbol sequence to be detected and the local synchronization code sequence should be:

After obtaining the correlation value of formula (1), a relatively direct method is to first calculate the modulus of the correlation value, and then compare it with the threshold to detect whether the peak exists. If the peak is detected, the phase ambiguity value is estimated by the relationship between the real and imaginary parts of the correlation value (arctan(*)).

However, the above method is quite complex to calculate, consumes a lot of FPGA resources, and is not easy to perform peak detection and phase ambiguity value estimation concurrently. Therefore, a simplified algorithm that is easy to implement on FPGA is proposed below.

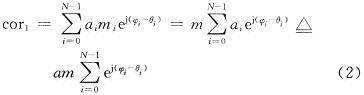

Since the phase ambiguity value needs to be estimated, the phase information in equation (1) cannot be omitted. And because the 8PSK signal has a constant envelope, mi is a constant; under the influence of noise, it is approximately a constant envelope, so ai can be approximately considered a constant. So equation (1) can be simplified to:

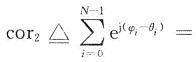

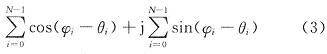

Dividing both sides of the equal sign in formula (2) by am, we can obtain the simplified algorithm in this paper as follows:

Comparing equation (1) and equation (3), it can be seen that the calculation of the correlation value of the latter is only related to the phase of the received symbol and the phase of the local synchronization code. Compared with the former, the amount of calculation is reduced by half, which greatly facilitates the FPGA implementation of the algorithm.

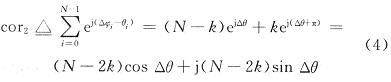

Assume that the frame header of the received data is completely aligned with the local synchronization code, but there are k code elements in the received frame header sequence that have errors. At this time, φi-θi corresponding to Nk i is a constant, set to △θ, and φi-θi corresponding to k i with errors is △θ+π. At this time, the correlation value can be expressed by formula (4):

Where: △θ is the phase ambiguity value; when k is 0, it means that there is no bit error in the frame header. Since in 8PSK modulation, the phase ambiguity value is an integer multiple of π/4, that is

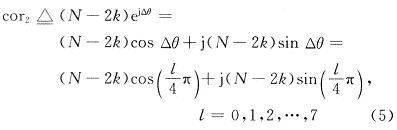

(calculated in the counterclockwise direction), so formula (4) can be written as follows:

(calculated in the counterclockwise direction), so formula (4) can be written as follows:

2.2 Threshold Decision Method

After obtaining the correlation value, the following method of setting two thresholds can avoid the complexity of calculation and can also perform peak pulse detection and phase ambiguity value estimation concurrently.

When the frame header of the received data is completely aligned with the local synchronization code, equation (5) can be discussed as follows:

(1) If l = 0, 2, 4, 6, that is, the phase ambiguity value is an even multiple of π/4, it can be seen from equation (5) that the correlation value only contains the real part or the imaginary part. Therefore, the absolute value of the real part or the imaginary part (the modulus of the correlation value) should be greater than the decision threshold, set to threshold_0.

(2) If l = 1, 3, 5, 7, that is, the phase ambiguity value is an odd multiple of π/4, it can be seen from equation (5) that the correlation value contains real and imaginary parts. The absolute values of the real and imaginary parts are approximately the modulus of the correlation value, so their multiples are approximately the modulus of the correlation value, and both should be greater than the threshold threshold_0. Therefore, they should themselves be greater than

Through the above analysis, we can know that the correlation detection problem can actually be transformed into the problem of comparing the real part and imaginary part of the correlation value with two thresholds. Its judgment logic is shown in Table 1.

Note: The second column is the phase ambiguity value calculated counterclockwise.

Equation (3) shows that the real part and the imaginary part of the correlation value can be calculated only by the phase of the received symbol and the phase of the local synchronization code.

After that, the real part and the imaginary part are compared with the two threshold values respectively, and then according to the decision logic in Table 1, the peak pulse and the phase ambiguity value can be directly detected.

Previous article:Implementation of JPEG Static Image Compression Algorithm Based on DSP Builder

Next article:Design of FPGA on-chip delay phase-locked loop capable of fast locking

Recommended ReadingLatest update time:2024-11-16 19:43

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- CC3235S and CC3235SF SimpleLink Wi-Fi dual-band single-chip solutions

- Design of ESD protection structure for CMOS circuits

- 8 Common Uses of Diodes

- TMS320C6655 Fixed and Floating Point Digital Signal Processor

- [Digi-Key KOL Lecture] Common Techniques for Designing Low-Power DC-DC Converters

- Problems encountered in B-U585I-IOT02A test

- [FS-IR02 + D1CS-D54] - 4: Linking with MCU (FS-IR02)

- [Atria Development Board AT32F421 Review] TEST06 CFFT related tests

- EasyARM-RT1052 Review] + Basic IoT transmission framework (final post)

- TCP/IP Detailed Explanation (Layer 7/Layer 4 Protocol)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号