1 Introduction

TQ6124 is a high-speed and high-precision digital-to-analog converter chip. It has 14 data bits and uses a segmented structure to divide the data bits into the highest 4 bits, the middle 3 bits and the lowest 7 bits. TQ6124 can use different digital-to-analog conversion methods for each segment of data. It integrates high-precision current sources and high-precision resistors to ensure the accuracy of digital-to-analog conversion. The conversion speed of TQ6124 can reach 1GSa/s. The chip is flexible in design and easy to use. Only one or two integrated circuits and a small amount of peripheral circuits are needed to form a complete and high-performance digital-to-analog converter.

2 Structural features and pin functions of TQ6124

2.1 Structure of TQ6124

TQ6124 is mainly composed of latch, encoder, delay, current source, current switch array, R~2R resistor network and other circuits. Figure 1 shows its internal structure block diagram. The main features of TQ6124 are as follows:

●The digital-to-analog conversion rate is up to 1GSa/s;

●Has 14 data bits;

●With 1G analog signal bandwidth;

●The output can be directly used as the front end of RF;

●Clock and digital data are ECL levels;

●Adopt 44-pin QFP package.

2.2 Pin Description of TQ6124

Figure 2 is the pinout of TQ6124. The functions of each pin are as follows (the numbers in brackets are pin numbers):

- Vss (1, 11, 12, 33, 34, 44): Digital power input terminal, usually connected to -5V. The bypass capacitor of the power filter should be as close to the power pin as possible and directly connected to the ground;

- VAA (21, 23, 24): -12V analog power input terminal;

- DGND (6, 7, 8, 28, 29, 37, 40): digital ground;

- AGND (13, 15, 18, 19): analog ground;

- D13~D0: digital signal input terminal, where D13 is the highest bit of data and D0 is the lowest bit of data;

- CLK, NCLK (9, 10): differential clock input terminals;

- NV0, V0 (16, 17): analog signal output terminal, differential signal;

- IREF (14): Reference current input terminal, directly connected to the analog ground, is the virtual current source of the switch array;

- VSNS (20): Determine the voltage output terminal. When the chip is working normally, there is output and Vsns = VREF.

- VREF (21): voltage reference input terminal, generally designed to be -9V. When VREF = -9V, the peak-to-peak value of the output analog signal is 1V.

- Midtrim (25): adjusts the voltage input terminal of the middle data bit to adjust the waveform, optional;

- Lsbtrim (26): adjust the voltage input terminal of the low-order data bit to adjust the waveform, optional;

- ECLref (27): Optional ECL level reference voltage input terminal. When the digital data and clock are at ECL level, this pin is left floating and a -1.34V voltage can be generated inside the chip.

3. TQ6124 Peripheral Circuit Design

TQ6124 is flexible and convenient to use. It only needs a voltage reference chip, an operational amplifier and a small amount of peripheral circuits (as shown in Figure 3). The main purpose of these two integrated circuits is to provide reference voltage for the digital-to-analog conversion chip. In the digital-to-analog converter, the accuracy, stability and jitter of the reference voltage have a great influence on the accuracy, stability and jitter of the generated analog signal. In particular, the 14-bit data bits of the chip are more sensitive to the performance of the reference voltage. AD586 is a voltage reference chip produced by AD Company. It has good performance and the peak-to-peak error is only 4μV, which can meet the 14-bit precision reference voltage requirements of TQ6124. The output of the voltage reference (AD586) and the feedback output VSENSE of the chip can form a negative feedback circuit through the operational amplifier MC34071 to stabilize VREF at -9V, thereby further reducing the impact of slight changes in the external power supply on it, thereby ensuring the accuracy and stability of the output analog signal.

4 Application Description

Although TQ6124 is easy to use, does not require harsh external conditions, and is easy to debug. However, when designing the circuit, especially in the layout and wiring of the printed circuit board, you must pay attention to following certain design rules, otherwise the interference may be very large, and in severe cases, the output analog signal quality is very poor and the signal-to-noise ratio is very low. Therefore, you should pay attention to the following issues when using it:

(1) Power supply decoupling: Generally, when designing the circuit, the analog power supply, digital power supply, and clock power supply should use 0.01μF capacitors to bypass and decouple their respective grounds. The decoupling capacitor should be as close to the input end of the chip power supply as possible. It is best to use surface mount components to reduce the interference caused by the leads, and the capacitor and chip should be on the same level to reduce parasitic inductance and capacitance.

(2) Ground processing: The analog ground, digital ground and clock ground should be connected separately, which helps to eliminate the interference between data and clock. A multi-layer circuit board with a complete and independent ground plane should be used to ensure the integrity of high-speed signals. The impedance between each plane should be as small as possible, and the AC and DC voltage difference between each plane should be less than 0.3V. The analog ground and clock ground should be connected to the digital ground at a single point at the power input end. Usually, magnetic beads or direct connections can be used to avoid interference between each plane.

(3) Termination of high-speed signals: In high-speed digital systems, impedance mismatch on the transmission line can cause signal reflection. The method to reduce and eliminate reflection is to perform terminal impedance matching at the transmitting or receiving end of the transmission line according to the characteristic impedance of the transmission line, so that the source reflection coefficient or the load reflection coefficient is close to zero. Therefore, the input high-speed ECL clock and high-speed ECL digital signal must be terminated before entering the chip to reduce reflection.

(4) Heat dissipation: Since the TQ6124 chip consumes a lot of power, a heat sink must be added when designing the circuit to ensure that the chip can work normally.

(5) High-speed digital signal lines and clock lines should be kept as far away from analog signal lines as possible. Digital ground should be laid around digital signal lines, analog ground should be laid around analog signal lines, and clock ground should be laid around clocks to avoid interference between signals.

(6) All signal lines should be as short as possible. If the signal lines are too long, the crosstalk between the lines may be large.

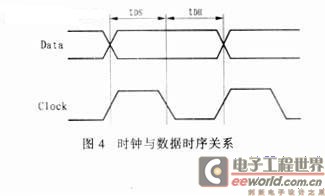

In addition, during the application of the chip, special attention should be paid to the following: Since the chip latches data on the falling edge of the clock, the timing relationship between the clock and data is shown in Figure 4. Therefore, in order to ensure the correctness of the data, the data change is best completed on the rising edge of the clock to ensure that the chip has sufficient setup time when sampling data.

Previous article:Principle and Application of Dual Sigma-Delta Converter with Auxiliary DAC

Next article:High-speed 12-bit analog-to-digital converter and its application in image acquisition

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Automotive External Amplifiers

- Award-winning live broadcast | Firmware upgrade solution for Renesas MCU

- Into space: Solid-state power amplifiers aid space exploration

- Frequency deviation definition and measurement method

- Load Modulation High Efficiency Linear Microwave Circuits—Base Station PA and Doherty

- Compile QT5 application with qt creator

- micropython update: 2021.3

- Show off the Xiaomi mouse I received from the Ti reading activity

- [AutoChips AC7801x motor demo board review] + motor demo board unboxing report and quick new project

- About the problem of L6226 controlling brushless DC motor

Signal Integrity and Power Integrity Analysis (Eric Bogatin)

Signal Integrity and Power Integrity Analysis (Eric Bogatin) PFC Reference Design and Source Code

PFC Reference Design and Source Code

京公网安备 11010802033920号

京公网安备 11010802033920号