The conventional use of D flip-flops is generally as a frequency divider, counter or shift register. However, as long as the peripheral circuit of the D flip-flop is improved, according to its basic logic function, its unique role can be fully utilized. The pulse width detection circuit commonly used in digital devices identifies the width of the pulse signal. For example, when the width of the input pulse is a specific value, a response is generated, otherwise no response is given. The following is an introduction to several pulse width detection circuits composed of CMOS dual D flip-flop CD4013.

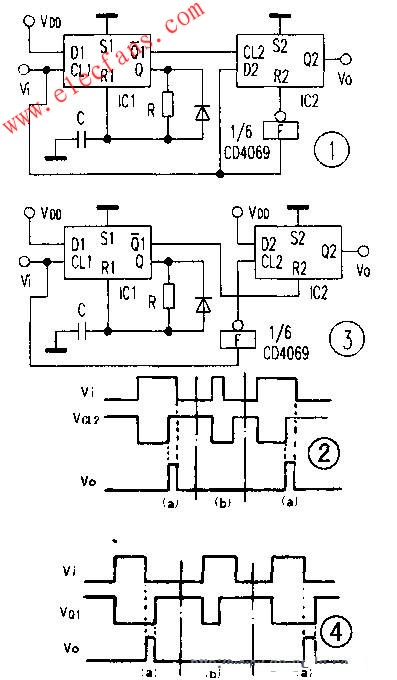

One of the detection circuits is shown in Figure 1. IC1 and IC2 are a piece of CD4013, in which IC1 constitutes a monostable flip-flop, the monostable output terminal Q1 serves as the clock pulse of the D flip-flop IC2, and the Q2 terminal serves as the vo output terminal. Since the set S terminals of ICl and IC2 are grounded, the Ql terminal of ICl is always zero in steady state, the Ql terminal is high level, and the VO output is low level. When the Vi input signal is high, the high level of the D1 terminal is sent to the ICl trigger, the Q1 terminal jumps to a high level, the Q1 terminal is low, the quasi-stable state begins, the IC2 trigger is not triggered, and VO is still low. When Vi is low, the quasi-stable state of the ICl monostable circuit has not ended (see Figure 2b), the IC2 trigger has not been triggered, and VO is low. When the quasi-stable state of ICl ends, the ICl trigger is reset, the Q1 terminal is low, and the Q1 terminal is high. Although the CL2 terminal of IC2 is high. However, since the Vi input signal is already low at this time, the reset terminal R2 of IC2 is high after being inverted by the inverter F, so the VO terminal is still low.

Another situation is: when Vi is high and the Q1 terminal is low, the ICl quasi-stable state begins and VO is low. When the temporary stable state of ICl ends, Vi is still at a high level (see Figure 2a), Ql jumps up, IC2 triggers flipping, R2 is at a low level, the high level of D2 is sent to IC2, and VO outputs a high level. When Vi jumps down, F makes R2 of IC2 a high level, forcing IC2 to reset. VO outputs a low level.

It can be seen that only when the pulse width of the Vi input signal is greater than the monostable output pulse width of ICl. IC2 trigger has an output.

The second detection circuit is shown in Figure 3. This circuit is similar to Figure 1, except that the Vi input signal is inverted by inverter F and used as the CL2 clock pulse of IC2. ICl is still a monostable circuit. In steady state, V0 is low level. When Vi is high level, Ql is high level, the temporary stable state begins, IC2 is not triggered, and V0 is low level. When the monostable state of ICl ends (see Figure 4b), Ql returns to a low level, and Vi is still high level at this time, so VO is low level. When Vi jumps down, the F inversion makes the LC2 end of IC2 jump up, but because the Ql end, that is, the R2 end of ZC2, is at a high level, VO is still at a low level.

Another situation is: when Vi is at a high level, Ql is at a high level, ICl's temporary steady state starts, IC2 is not triggered, and V0 is at a low level. When Vi looks down, the temporary steady state has not ended, the Q1 end is still at a low level, IC2 triggers and flips, and VO outputs a high level (see Figure 4a). When the temporary steady state of the ICl monostable circuit ends, the Ql end jumps up to a high level, forcing IC2 to reset, and VO outputs a low level. It can be seen that only when the pulse width of the Vi input signal is less than the monostable output pulse width of ICl. The IC2 trigger has an output.

Previous article:Frequency response small signal circuit diagram

Next article:Channel design scheme for adding synchronization signals to standard definition video signals

Recommended ReadingLatest update time:2024-11-15 09:54

- Popular Resources

- Popular amplifiers

-

Virtualization Technology Practice Guide - High-efficiency and low-cost solutions for small and medium-sized enterprises (Wang Chunhai)

Virtualization Technology Practice Guide - High-efficiency and low-cost solutions for small and medium-sized enterprises (Wang Chunhai) -

Operational Amplifier Practical Reference Handbook (Edited by Liu Changsheng, Zhao Mingying, Liu Xu, etc.)

Operational Amplifier Practical Reference Handbook (Edited by Liu Changsheng, Zhao Mingying, Liu Xu, etc.) -

CMOS_Transistor_Layout_KungFu

CMOS_Transistor_Layout_KungFu -

Power Integrated Circuit Technology Theory and Design (Wen Jincai, Chen Keming, Hong Hui, Han Yan)

Power Integrated Circuit Technology Theory and Design (Wen Jincai, Chen Keming, Hong Hui, Han Yan)

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

- Detailed explanation of intelligent car body perception system

- How to solve the problem that the servo drive is not enabled

- Why does the servo drive not power on?

- What point should I connect to when the servo is turned on?

- How to turn on the internal enable of Panasonic servo drive?

- What is the rigidity setting of Panasonic servo drive?

- How to change the inertia ratio of Panasonic servo drive

- What is the inertia ratio of the servo motor?

- Is it better for the motor to have a large or small moment of inertia?

- What is the difference between low inertia and high inertia of servo motors?

- 【RPi PICO】Breathing light

- A busbar power supply plant power rapid protection anti-sway cabinet

- How to put C2000 into low power mode

- GD32F350 is easy to use

- Industrial and Automation Solutions Collection

- Award-winning live broadcast | Use ModusToolbox to build a system to flexibly meet IoT design challenges

- Verilog009

- 5G is a revolutionary advancement in mobile communications

- 【GD32E503 Review】 ADC Experiment

- How to achieve ZigBee fast networking?

Virtualization Technology Practice Guide - High-efficiency and low-cost solutions for small and medium-sized enterprises (Wang Chunhai)

Virtualization Technology Practice Guide - High-efficiency and low-cost solutions for small and medium-sized enterprises (Wang Chunhai)

京公网安备 11010802033920号

京公网安备 11010802033920号