1. Design of USB interface based on DSP

1 Introduction

The data processed by DSP often needs to be transferred to PC for storage and reprocessing, so the high-speed communication problem between DSP and PC must be solved. This design uses the C5000 series DSP chip TMS320VC5416 of Texas Instruments (TI) as the microprocessor and uses the USB2.0 interface chip CY7C68001 provided by Cypress to implement the USB2.0 slave interface design, so that PC and DSP can achieve high-speed bidirectional data transmission through the USB2.0 interface.

2 TMS320VC5416 and CY7C68001 EZUSBSX2 hardware interface design

The system solution uses a PC as the host computer, which is responsible for detecting the device access on the USB bus and enumerating and identifying the device, and can control the data transmission by running the application on the PC. The USB chip is used as the USB device end to connect the DSP and the host computer for data exchange. The DSP is used to implement the USB protocol. Through DSP programming, DSP data communicates with the PC through the USB interface, and the descriptor writing of the USB chip and the processing of various command states are all implemented through DSP programming.

TMS320VC5416 is a 16-bit fixed-point high-performance DSP from TI. Due to the low power consumption and high performance of VC5416, its separate instruction and data spaces give the chip a high degree of parallel operation capability, allowing instructions and data to be accessed simultaneously in a single cycle. Coupled with the highly optimized instruction set, the chip has a very high operating speed. At the same time, the chip itself has rich on-chip memory resources and a variety of on-chip peripherals, so it has been widely used in the engineering community.

Cypress's CY7C68001 EZ-USB SX2 is a high-performance, easy-to-use USB2.0 interface chip that meets the USB2.0 protocol and can work in high-speed (480Mbps) or full-speed (12Mbps) mode. It provides a control endpoint for processing USB device requests and four configurable endpoints for transmitting control and data signals. These four endpoints share a 4KB FIFO space and have a standard 8-bit or 16-bit external host interface. It can seamlessly connect to a variety of standard microprocessors, such as DSP, ASIC and FPGA, and can be set as a synchronous or asynchronous interface according to requirements. The chip integrates a phase-locked loop (PLL). This chip is widely used in DSL modems, MP3, card readers, digital cameras, scanners, printers and other devices.

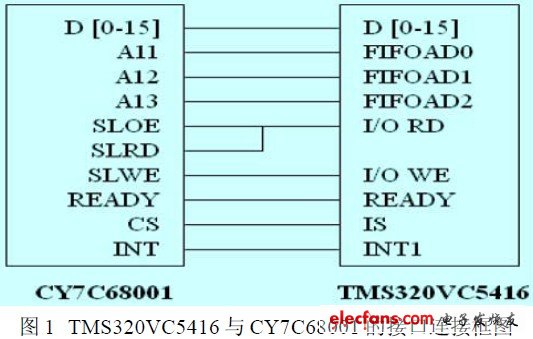

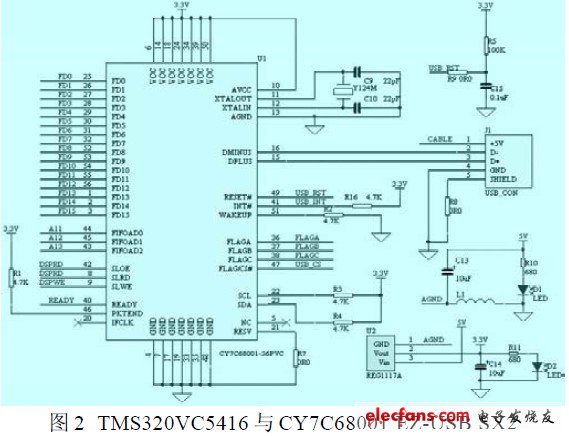

The hardware interface design of the system is shown in Figure 1 and Figure 2. The two communicate through data and address buses as well as read and write signal lines. The chip select signal of CY7C68001 is connected to the I/O space chip select signal of TMS320VC5416, and the FIFO of CY7C68001 is expanded on the I/O space of VC5416.

The power supply part uses a 1117 to convert 5V to 3.3V to supply CY7C68001EZ-USB SX2. The analog ground and digital ground are connected by magnetic beads. The reset part adopts RC circuit design, and the chip data introduces typical values of 100KΩ and 0.1μF.

3 Interface operation principle

CY7C68001 has two external interfaces:

(1) Command interface: used to access CY7C68001 registers, Endpoint 0 buffer, and description table.

(2) FIFO data interface: used to access data in four 1K-byte FIFOs.

Both external interfaces can be accessed synchronously or asynchronously.

This design uses asynchronous access. According to the address allocation in Figure 3, the three high-order address lines (A11, A12, A13) of TMS320VC5416 are used to connect FIFOAD0/1/2 of CY7C68001 to select FIFO2, FIFO4, FIFO6, FIFO8 and the command interface. The address table is shown in Figure 3. When the address line FIFOADR[2:0] of CY7C68001 is 100B, the command port (Command) of CY7C68001 is selected. Through the command port of CY7C68001, 37 registers, Endpoint 0 buffer (64-byte FIFO) and description table (500-byte FIFO) can be accessed. The read and write mode of these registers adopts the secondary addressing mode, that is, the sub-address and operation type (read or write) of the register to be addressed are written through the command port first, and then the data is read out or written into the corresponding register through the command port.

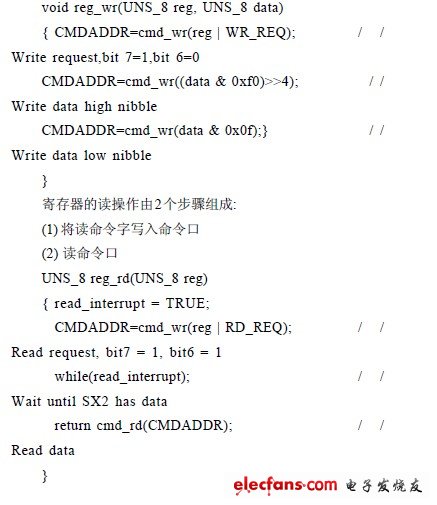

The content written to the command port is called a command word. The command word contains the sub-address of the register to be addressed, or the upper 4 bits or lower 4 bits of the data to be written to the register. The read command port must be followed by writing a read command word to the command port, and the 8-bit data read out is the corresponding register. Therefore, the register write operation consists of 3 steps:

4 USB interface software design

The software design of the USB interface consists of two parts: one is to run the USB 2.0 Utility tool in the PC Windows, which is a Windows graphical user interface software that provides an interface program between CY7C68001 and the Windows operating system, making the development of CY7C68001 simple. The second is to run the embedded application code in the DSP and provide hardware drivers to manage CY7C68001 to perform different data processing methods, thereby realizing the USB2.0 transmission protocol.

4.1 USB interface software design process

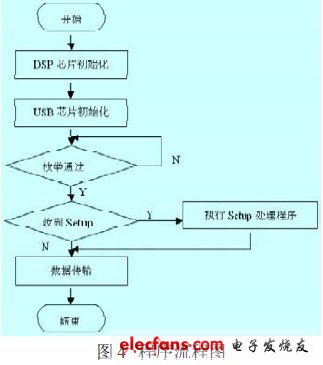

Software design of USB interface, the DSP side code generally includes DSP chip initialization (vc5416_init function), USB chip initialization (sx2_init function), USB chip configuration program (sx2_setup function) and USB chip data reading and writing program (sx2_processdata function). The program flow is shown in Figure 4.

DSP chip initialization (vc5416_init function) is mainly responsible for setting the operating frequency of VC5416, configuring SWCR and SWWSR registers. In addition, this application system uses a GPIO pin as the reset signal of 68001, so it also needs to be set up accordingly.

The USB chip initialization (sx2_init function) is mainly responsible for clearing the Buffer buffer and enabling the external interrupt INT1 of VC5416. After the initialization is completed, a READY interrupt is issued. At this time, the DSP writes the descriptor to 68001 and performs the enumeration process. After the enumeration is successful, an ENUMOK interrupt is issued. The enumeration method can use an external EEPROM to import the descriptor from the outside after powering on the I2C bus, or it can be imported from the DSP to the 68001 by running the DSP program. This application system uses the second enumeration method.

The USB chip configuration program (sx2_setup function) is executed after the command channel (node 0) receives a request from the host computer that cannot be automatically processed and 68001 sends a SETUP interrupt to VC5416. At this time, VC5416 can get an 8-byte request by executing eight consecutive read operations on the SETUP register. The system can respond to the request or STALL the request.

The USB chip data reading and writing program (sx2_processdata function) enables the PC and the USB slave device to communicate data in accordance with the USB transmission protocol.

When the address FIFOAD[2:0] of CY7C68001 is 100, the command interface of CY7C68001 is selected. The reading and writing of the command interface are carried out in two steps, that is, when READY is valid, the sub-address of the register to be addressed and the operation type (read or write) are written through the command interface first, and then, when READY is valid again, the command interface is read and written twice to read and write one byte of data.

4.2 Key points of interrupt service program design

DSP uses an external interrupt pin (INT1) to connect to the INT pin of CY7C68001. A series of activities on the USB bus will trigger corresponding interrupts. Once an interrupt occurs, DSP will read the corresponding value from the Command port of CY7C68001 to determine what kind of interrupt has occurred.

CY7C68001 EZ-USB SX2 includes six interrupt sources: SETUP (interrupt generated when receiving the Setup packet sent from the USB host computer (PC)), EP0BUF (interrupt generated when the endpoint 0 buffer is available), FLAGS (interrupt generated when the status of the OUT endpoint FIFO changes from empty to non-empty), ENUMOK (interrupt generated after SX2 enumeration is completed), BUSACTIVITY (interrupt generated when SX2 detects bus activity) and READY (interrupt generated after SX2 is powered on and reset). Each interrupt source can be enabled or disabled by setting or clearing the corresponding bit in the INTENABLE register.

The CY7C68001 chip uses an interrupt buffer mechanism. There will be only one interrupt source at a time. Other interrupt sources will only issue a new interrupt request after the previous interrupt is read.

Therefore, when an interrupt occurs, the INT pin is in a low level state, and the interrupt status bit will be placed in the command interface. After entering the interrupt program, the interrupt source should be judged first. First, determine whether the interrupt is generated by reading the register. If so, set the data ready flag to 1 and then return. Otherwise, the external PC reads the interrupt status bit from the command interface by selecting the SLRD/SLOE signal to determine what kind of interrupt is generated, and then performs corresponding operations according to the interrupt source. After the DSP reads the interrupt status bit, it automatically clears the interrupt flag bit.

5 Conclusion

Through the construction of the hardware platform and the implementation of the software program, it is verified that the interface circuit can meet the data transmission requirements of high-speed signal processing and has the advantages of fast speed and high reliability.

Previous article:RS232-RS485 three-wire converter schematic diagram

Next article:Key to DSP application design: interface design (Part 2)

- Popular Resources

- Popular amplifiers

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

- STM32 timer interrupt HAL library does not check FLAG

- Why are the sampling results of C8051F350 with different decimation ratios very different?

- The result obtained by using sprintf in KEIL hardware simulation changes the decimal point 0x2E to 0x00

- FPGA Features

- Why does the range of electric vehicles drop significantly in winter?

- Unveiling the electric mask solution

- Why do thyristor controlled solenoid valves often break down?

- EEWORLD University - How to develop a 4g smart device using the new version of Gizwits Cloud platform

- Bluetooth module problem

- [Raspberry Pi Pico Review] - PWM and breathing light examples

TC52N2920ECTRT

TC52N2920ECTRT

京公网安备 11010802033920号

京公网安备 11010802033920号