1 Overall hardware design of infrared guidance control system

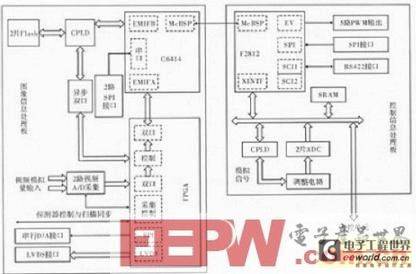

The infrared information data processing system is divided into two major blocks according to its functions, and the data processing system is composed of an image information processing board and a control information processing board. Its infrared guidance control information data processing system is shown in Figure 1. The image information processing board is mainly responsible for a large number of real-time image signal preprocessing, image signal processing and control tasks; the control information processing board controls the acquisition of interface signals, the solution of tracking loops, control output and communication with flight control computers, etc. At the same time, the control management module is also the management module of the system, completing the input/output operation of the system, synchronous control, system status management and other functions.

Figure 1 Block diagram of infrared information data processing system

2 Hardware Design of Image Processing Module

The hardware of the image processing module consists of reset circuit, clock circuit, image acquisition and preprocessing circuit, DSP image processing circuit, power conversion circuit and external interface circuit. The block diagram is shown in Figure 2.

Figure 2 Image acquisition unit circuit composition

2.1 Image acquisition unit

The image acquisition unit consists of a scanning synchronization interface circuit, a detector interface circuit, a front-end adjustment circuit, an A/D conversion circuit, a sampling control and data integration circuit, and a data cache (synchronous dual-port) circuit. The circuit composition block diagram is shown in Figure 2. The scanning synchronization signal comes from the scanning module in the system. This signal provides the system timing reference, and its signal is synchronized with the frame synchronization signal. The scanning synchronization signal is connected from the bottom board connector. The detector interface circuit includes: reference power supply, temperature signal, sampling control signal and 2-channel video analog signal, etc. The above signals are controlled by the internal acquisition circuit of the FPGA to ensure the synchronous acquisition of each frame of image data. The adjustment circuit adjusts the video signal output by the detector to the range of high-speed A/D input. The differential video signal is amplified and driven by the differential driver, and its common-mode input voltage is the reference signal (2.5 V) on the video A/D chip. The analog signal is input to the A/D using a differential input method. The video A/D is mainly used to convert analog signals between video circuits and digital signals. According to the overall requirements of the circuit, the A/D conversion circuit must meet the requirements of high sampling frequency, low power consumption, and high conversion accuracy. The sampling control and data cache circuits are completed by the sampling control circuit inside the FPGA . The data cache circuit is completed by the dual-port memory inside the FPGA, which has the performance of high-speed, synchronous and asynchronous read and write operations.

2.2 DSP image processing circuit

The DSP image processing circuit mainly includes the processor and peripheral configuration circuit, memory circuit and McBSP serial port circuit for communication with the control board interface. The processor uses C6414 GIZA-6E3 from TI's high-performance fixed-point TMS320C641x series as the image information processing C6414-6E3, with a clock cycle of 1.67 ns, an internal working clock of up to 600 MHz, and a maximum processing speed of up to 4 800 MIPS; the internal memory capacity is 8 Mbit; there are 2 extended memory interfaces, EMIFA is 64 bits, EMIFB is 16 bits, the bus frequency of EMIFA can reach 133 MHz, and the maximum addressable space is 1280 MB; the core operating voltage is 1.4 V, and the operating temperature can reach -40~105℃. It completes the main processing algorithms such as image combination, segmentation and enhancement, template matching, background processing, target extraction and target tracking of the infrared imaging guidance seeker.

The FPGA preprocessing unit is another core component on the image information processing board, which is implemented using the XC2V2000-FG676 from the Vertex-II series of Xilinx. The XC2V2000 has a scale of 2 million gates, and its internal storage resources include 1 Mbit Select RAM, 336 kbit Distributed RAM, 408 IO pin resources, and 8 DCMs. The FPGA preprocessing unit design consists of a video acquisition control and data integration unit, a video acquisition buffer and a main processing buffer dual-port memory, a preprocessing unit, an image output daughter card data transmission interface control, a serial SPI interface controller, a LVDS digital video output interface, and a host control circuit for accessing the DSP/HPI interface. In addition, the FPGA configuration of the image information processing board can realize the field online configuration function.

The memory circuit includes two types of memory: Flash and FPGA internal synchronous dual-port memory. It can be connected to the C6414 (EMIF external memory interface, C64 has two buses EMIFA and EMIFB). When in use, the EMIF bus needs to be configured through DSP/BIOS to determine the access timing. There are two Flash resources on the image information processing board, which belong to DSP and FPGA respectively. The Flash belonging to FPGA stores the on-board control code, and the Flash belonging to DSP is used to store module BOOT programs and user applications. In order to configure FPGA in a slave-parallel manner, its Flash is connected to the C6414 EMIFB asynchronous BANK CE0, and asynchronous read and write signals are used; to support the mechanism of C6414 booting from ROM, the Flash belonging to DSP is connected to the C6414 EMIFB asynchronous BANK CE1 using asynchronous read and write signals. The dual-port memory is mainly used to store frame image data. The dual-port memory is configured on the FPGA of the image information processing board. In the application, synchronous or asynchronous dual-port memory can be configured through FPGA design to exchange data with C6414. The capacity can be configured as 16 kbit×16 bit according to the image frame size, and 16-bit or 32-bit access mode can also be configured. The dual-port memory on the image information processing board is connected to the EMIFA synchronous BANK ACE0 space of C6414, and can be configured in synchronous or asynchronous mode.

3 Hardware Design of Control Information Processing Module

The control information processing board consists of a processor, a clock and reset circuit, a memory, a digital pulse counting and logic control circuit, an analog-to-digital conversion A/D circuit, and an indicator light circuit, as shown in Figure 3.

The signal processor of the control information processing board uses TMS320F2812, which is provided with input working clock by 30 MHz crystal, 16-bit bus width, and can access 128 kW on-chip program storage space and 64 kW data storage space, with three levels of external interrupts. The clock circuit uses an external crystal oscillator to provide 30 MHz clock input for F2812, and the internal PLL circuit configures the F2812 working clock to 120 MHz and the external bus working clock to 60 MHz. The reset circuit is output by the LDO power converter of this board, and the reset input generates the reset of the control information processing board DSP through the logic control of CPLD. The control information processing board mainly has the following memory configuration: F2812 on-chip memory includes: 18 kW SARAM, 128 kB Flash, 4kB Boot Rom. The off-chip storage space includes: 512kB SRAM, 1 kB flight control computer dual-port storage space, data registers of 3-way digital pulse counting circuits and data port addresses of 2 A/D converters on the board, etc.

The programmable logic CPLD circuit completes the 3-way digital pulse counting, reset circuit and decoding logic of the control information processing board. The decoding logic generates a chip select signal for accessing the A/D chip and the interface with the flight control module through logic decoding from the external memory chip select signal of F2812 and the high address line.

The principle of CPLD to count and measure the frequency of 3-channel digital pulse signals is: after the 3-channel digital pulse signals are counted and processed by the CPLD frequency measurement circuit, they are read regularly by F2812 through software programming.

Two A/D converters realize analog-to-digital conversion of 9 analog inputs. The A/D circuit is shown in Figure 4. The system inputs 9 differential AC analog signals. These 9 analog signals need to be adjusted to 0~+5 V using differential op amps and input to the A/D converter at the same time. The sampling clock is controlled by the CPLD.

4. Software Function Design

The image control information processing system has a complex structure and many interfaces. Due to space limitations, only a brief introduction is given to the BIT test method to verify whether it meets the requirements of the imaging guidance system and the target signal processing system. The A/D test uses the digital FFT method. The Flash and RAM tests use the read-write comparison chip spatial data to complete the judgment. The interface test is realized by inputting analog signals from the outside through the hardware interface and then running the software to perform threshold judgment on the calculation results. The image data transmission rate test is realized by configuring the EMIF bus and the synchronous dual-port RAM inside the FPCA as a master-slave test loop method. The BIT test results are converted to the RS232 interface through the RS422 interface and connected to the PC for display. The test results are intuitive and local circuit faults are easy to locate.

5 Conclusion

Aiming at the needs of infrared image information processing of missile-borne computers, this paper develops a data processing system with DSP (TMS320C6414) processor + FPGA (XC2V2000-FG676) as the core, and designs the software and hardware. The test results show that the system has strong processing capabilities, is easy to debug, and is easy to locate when hardware failures occur.

Previous article:A Design Scheme of Audio Processing System Based on ARM+DSP

Next article:Design of external FLASH automatic loading based on TMS320C6455

Recommended ReadingLatest update time:2024-11-16 15:43

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Modern arc welding power supply and its control

Modern arc welding power supply and its control -

Intelligent Control Technology of Permanent Magnet Synchronous Motor (Written by Wang Jun)

Intelligent Control Technology of Permanent Magnet Synchronous Motor (Written by Wang Jun)

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Suspicious signal from outer space

- Download gift: USB Type C related development and test materials, read it when you have nothing to do, and you will become a master by accident

- Qorvo explains WIFI and 5G clearly

- SPIN3201 (STSPIN32F0) three-resistance control board: FOC motor drive schematic/code/debugging documents and other detailed information...

- Should segment display screens be backlit? How to add it?

- Installation and setup of CCS StarterWare, successfully compiling a project with CCS7.3

- EEWORLD University ---- Operational Amplifier Video Tutorial

- Have you ever encountered the problem of USB drive repair? Is there any good tool you can recommend?

- Several major wireless technologies

- How to modify the video recorder startup screen

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号