Abstract: This paper uses FPGA to design the LED display receiving control system, focusing on the system hardware design scheme, and further solves the grayscale control of LED large screen data, the performance requirements and implementation methods of external expansion memory. QuartusII software is used to develop each module. The user-friendly interface operation provided by QuartusII software allows many modules to be directly implemented in the system, which is convenient and practical.

LED screens appeared as early as the 1960s, but full-color screens did not appear until the mid-1990s. The price of this technology has dropped significantly in recent years, and the resolution has also improved significantly. For video, the low-resolution performance of LED screens is good. The resolution of LED screens is usually similar to that of computer monitors. LED color display large screens are the most used outdoor display screens and are recognized as the most worthy industry for development in outdoor large display screens. LED screens are superior with their high brightness and long service life. Compared with LCD, LED screens have faster response speed and higher brightness when playing videos. Compared with electron emission displays, LED manufacturing is simpler. Compared with OLED, LED technology is more mature. In short, LED display occupies the high-resolution video display market with its unique advantages. The large-screen LED dot matrix display system based on FPGA designed in this paper processes data faster and has a larger storage capacity. 1. Overall design of the receiving card control system

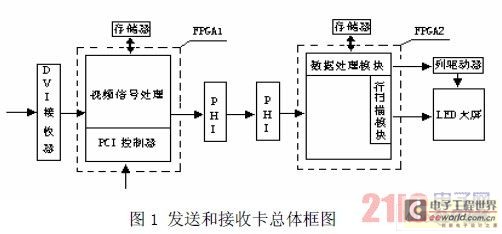

As shown in Figure 1, the video data is transmitted to FPGA1 through the DVI interface to switch the resolution, select the display area, and perform anti-gamma correction on the signal. It is then transmitted to FPGA2 of the receiving card through the network, and FPGA2 performs data caching, grayscale control, and row scanning and column driving functions.

The receiving card receives the data transmitted by DVI to FPGA1 and processed by FPGA1. Data processing is also performed inside FPGA2 to achieve the following goals: (1) Data can be displayed in partitions on the LED screen; (2) 256 grayscale screen size: 256*800.

1. Selection of grayscale implementation scheme

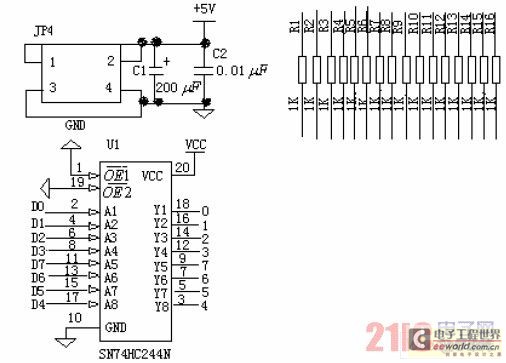

A dedicated driver chip BHL2000 is used to control the LED display dot matrix, which has an automatic grayscale control circuit inside.

BHL2000 is a high-performance ASIC for outdoor and indoor screens that is specially used for LED scanning and driving. BHL2000 chip uses duty cycle modulation for the grayscale of LED dot matrix and accepts 8-bit parallel grayscale pulse width proportional to the grayscale data value. The image data storage capacity is 32*16*8 bits. Data input scanning and data output scanning are independent, and the control system structure is simple.

Compared with general chips, dedicated chips have their own unique characteristics. Dedicated driver chips have SRAM inside and constant current control during output. LED display effect is better, grayscale is simple to achieve, easy to control, and lays a good foundation for future expansion.

2. Memory solution design

There are six memory implementation schemes: (1) FIFO implementation; (2) dual-port RAM implementation; (3) SDRAM implementation; (4) SRAM implementation; (5) FLASHROM implementation; (6) FPGA internal open memory implementation.

According to the 800*256 resolution index and grayscale control method to be achieved by the LED display, SRAM is selected to realize the cache of received data. Because of its large capacity, fast speed, easy address control, it can jump address to read and write data, and facilitate data partition retrieval. [page]

2. Receiving card control system unit module design

1. Clock control module

1. Line count clock and scan control signal

When row scanning is used, a row scanning control signal must be generated. As shown in Figure 2, row[4..0] is the row scanning control signal, which is used to connect a 2-4 decoder and four 3-8 decoders to generate 32 row selection signals to form a 1/32 scanning display. Hclk is the row counting clock, which can also be called the row latch clock.

Figure 2 Schematic diagram of row driver module [page]

2. Shift clock module

The generation of the shift clock CP signal is based on the screen resolution of 256*800, the refresh frequency of 60HZ, and the scanning mode of 1/32, so the shift frequency is 32*800*60=1.5MHZ. Among them, 32 is the scanning mode, and 32 rows share one column drive module. 60 is the refresh frequency, so the shift clock CP can be realized by a clock frequency division circuit.

3. Grayscale control clock

Since the BHL2000 dedicated driver chip is used, the grayscale control clock is generated by FPGA through calculation. According to the 32*32 dot matrix, its refresh frequency is 60HZ, then the dot frequency is 60*32*32=60KHZ, and its line frequency is dot frequency/32=2KHZ, so the grayscale control clock frequency is 256*2k=512KHZ.

2. Memory Control Module

According to the size of the LED display, the capacity and read/write speed of the memory can be determined. The storage is stored in color-separated order. The storage capacity is 256*800=200KB for at least one frame of data. Six SRAMs with a capacity of 256K can be selected. Since a 32*32 dot matrix screen is used for debugging, such a large capacity is not required. Only SRAM is implemented inside the FPGA. In order to facilitate viewing the results of the LED display, ROM is implemented in the FPGA. Some information is fixedly stored in it to prove whether the LED display is the same as the content in the ROM.

3. Display screen drive unit

1. Row driver module III. FPGA development process

The system programming adopts the Verilog language input method, and the software used for design is QuartusII software.

Altera's QuartusII design software provides the most comprehensive FPGA, CPLD and structured ASIC design flow, combined with a variety of intellectual property (IP) cores that can be directly applied to design, which can greatly improve design efficiency. The software provides a complete multi-platform design environment, with solutions for all stages of FPGA and CPLD design, which can well meet the needs of specific designs.

The author's innovation: The large-screen LED dot matrix display system is implemented using a programmable logic device, FPGA, which can be implemented as in-system programmable (ISP). Users can reconstruct the logic device programming or repeatedly rewrite it in the target system or circuit board designed by themselves, thereby realizing the softwareization of hardware design and modification, shortening the development cycle, achieving obvious economic benefits, increasing design flexibility, and further improving the performance of the entire system.

Previous article:FPGA Implementation of a Precise Symbol Timing Algorithm for OFDM Systems

Next article:Application of FPGA in the control system of film processor

Recommended ReadingLatest update time:2024-11-16 15:47

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- LCD Operation (S3C2440)

- The operational amplifier forms a three-point capacitor oscillation

- [NXP Rapid IoT Review] First give SLN-RPK-NODE an emulator

- Guangdong companies are looking for electronic engineers/structural engineers/acoustic engineers

- Can the output voltage of an LDO be equal to the input voltage?

- After importing the 2812 project example, it prompts that it does not match and cannot be run

- EFT 2B, but all others passed.

- STM32 freezes and needs power-on reset

- Schematic diagram and PCB of EBAZ4205 mining board based on Z7010

- 【Repost】Analysis of the process and principle of lithium battery core slurry

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号