The methods to achieve bit synchronization are similar to carrier synchronization. There are two methods: direct method (self-synchronization method) and pilot insertion method (external synchronization method). The direct method is divided into filtering method and phase-locked method. The method introduced in this article is implemented using the phase-locked loop in the direct method.

1 Principle of digital lock phase synchronization extraction

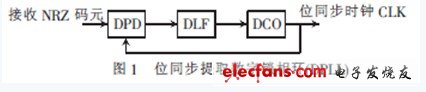

The digital communication system receiving end bit synchronization extraction usually adopts the digital phase locked loop DPLL (Digital Phase Locked Loop) as shown in Figure 1. DPLL consists of three components:

(1) The digital phase detector (DPD) compares the phase of the received code element with the bit synchronization clock output by the local DCO and outputs a digital signal reflecting the phase difference.

(2) The digital loop filter (DLF) filters the phase error digital signal output by the DPD, removes the influence of random noise, and outputs a more accurate phase error digital signal.

(3) Digital Controlled Oscillator (DCO) is an oscillator composed of digital circuits. It outputs a bit-synchronous clock pulse CLK at the same rate as the received code element. Its phase can be advanced or delayed by the phase error digital signal and is finally phase-locked with the received code element.

DPD and DCO are essential components of a digital phase-locked loop, and DLF can be added as needed. Each of the three components consists of a variety of circuits to form different digital phase-locked loops. The most typical digital phase-locked loop is a lead-lag digital phase-locked loop, also known as a differential rectification digital phase-locked loop, which can be implemented by the single-chip microcomputer system shown in Figure 2 when the code rate is not high. In the figure, edge detection is also called zero-crossing detection. It amplifies and shapes the input data signal DK1, and then transforms its jump edge (zero crossing point before shaping) into a narrow pulse ZCD, which is sent to the external interrupt input terminal INT1 of the single-chip microcomputer. The delay circuit in edge detection can be implemented with several levels of gates. The differential rectification circuit has the same function as the edge detection circuit.

This digital phase-locked loop does not use DLF. The T0 timer in the MCU and its interrupt service routine realize the DCO function. When DK1 has no transition edge (no ZCD negative pulse), the MCU does not enter the INT1 interrupt service routine, and the T0 timing is the input code period Tb. When DK1 has a transition edge, it enters the INT1 interrupt service routine, first reads the current value of T0 and the expected value (Tb/2 time constant), and determines by comparison whether the DCO phase is ahead or behind the phase relationship between the DK1 data transition edge, and adjusts the DCO phase accordingly. If the DCO phase is ahead, set the T0 next cycle timing to Tb+δ to delay the DCO phase; if the DCO phase lags, set the T0 next cycle timing to Tb-δ to advance the DCO phase, and finally achieve DCO phase lock with the DK1 data phase. In short, the INT1 interrupt service routine realizes the DPD and DCO control functions, and the T0 timer and its interrupt service routine realize the DCO function. The T1 timer and its interrupt service program implement delay, i.e. phase shift, so that the phase difference between the last output bit synchronization clock CLK and DK1 (or DK2) is 0 or 180°: when the transmission system frequency band is not limited and MSK/FSK modulation and demodulation is adopted, DK1 is a square wave, and the receiving end adopts integration/sampling/judgment for detection, and the phase difference between the two should be 0, that is, CLK and DK1 data edges are aligned; when the transmission system frequency band is limited and GMSK/GFSK modulation and demodulation is adopted, DK2 (the signal of DK1 after LPF) is a bell-shaped pulse, and CLK should sample/judgment at the midpoint of DK2 code element, and the phase difference between the two is 180° or Tb/2, as shown in Figure 2(d). The T1 delay is controlled by the P1.4 input signal MSKC. The block diagram of the INT1, T0 and T1 interrupt service programs is shown in Figure 3. The main program steps after completing the initialization of the three interrupt sources and other initializations.

The bit synchronization extraction digital phase-locked loop is implemented by CPU2, and its P1.4 input control signal MSKC comes from CPU1 and is determined by the working mode: in FSK/MSK working mode, MSKC=1; in GMSK/GFSK working mode, MSKC=0.

For the received random digital signal, it can be approximately considered that the probability of 00, 01, 10, and 11 appearing in two adjacent code elements is equal, and half of them have data jumps. For a digital phase-locked loop without DLF, the phase can be adjusted once every data jump, so the phase can be adjusted once every 2Tb s on average, so the synchronization establishment time is:

The digital phase-locked loop with DLF has a lower phase adjustment rate than the one without DLF, so the synchronous belt is smaller than formula (5).

From equations (1), (2) and (5), we can see that the three performance indicators all depend on the DCO cycle adjustment step δ: the larger the δ, the larger the synchronization band, the shorter the synchronization establishment time, but the phase error increases. Therefore, δ should be selected in a compromise. Under the premise of ensuring that the phase-locked loop can be locked (synchronized), δ should be as small as possible to reduce the phase error.

3 This design uses a single-chip microcomputer chip to implement digital circuit related devices, which simplifies the complex logic circuit design of related devices, reduces the power consumption and cost of the system, and improves the reliability of the system. There are many ways to achieve bit synchronization. This article discusses the use of digital phase-locked loop technology to extract bit synchronization signals. In bit synchronization extraction, how to shorten the synchronization establishment time, reduce the bit error and increase the synchronization holding time are the efforts of a good bit synchronization design.

Previous article:Brief Analysis of Transmitting Performance of 800MHz CDMA Base Station

Next article:Inverter refrigerator reference solution based on TMPM374 and IPD

Recommended ReadingLatest update time:2024-11-16 21:58

- Popular Resources

- Popular amplifiers

-

Wireless Sensor Network Technology and Applications (Edited by Mou Si, Yin Hong, and Su Xing)

Wireless Sensor Network Technology and Applications (Edited by Mou Si, Yin Hong, and Su Xing) -

Modern Electronic Technology Training Course (Edited by Yao Youfeng)

Modern Electronic Technology Training Course (Edited by Yao Youfeng) -

Modern arc welding power supply and its control

Modern arc welding power supply and its control -

Small AC Servo Motor Control Circuit Design (by Masaru Ishijima; translated by Xue Liang and Zhu Jianjun, by Masaru Ishijima, Xue Liang, and Zhu Jianjun)

Small AC Servo Motor Control Circuit Design (by Masaru Ishijima; translated by Xue Liang and Zhu Jianjun, by Masaru Ishijima, Xue Liang, and Zhu Jianjun)

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- I need help from an expert. "When designing a microcontroller hardware circuit using STC89C51, should I design the EEPROM circuit part?"

- Claiming that software is open source when it is not is false advertising

- Zigbee 3.0 universal gateway coordinator based on CC2652R

- Ask a question about the LM35CZ temperature sensor

- MSP430FR2311 LaunchPad Development Kit

- 【NUCLEO-L552ZE Review】- 6: After the summary, start again...

- A simple chopper circuit drawn by myself

- Functions of vent valve and drain valve of magnetic flap level gauge

- Some experience sharing on program debugging

- Pingtouge RISC-V low power board-RVB2601 transplanted CoreMark

Wireless Sensor Network Technology and Applications (Edited by Mou Si, Yin Hong, and Su Xing)

Wireless Sensor Network Technology and Applications (Edited by Mou Si, Yin Hong, and Su Xing)

京公网安备 11010802033920号

京公网安备 11010802033920号