Introduction and application of ModelSim and QuestaSim functions

ModelSim is the most outstanding language simulator in the industry. It provides the most friendly debugging environment and is the first choice for RTL-level and gate-level circuit simulation for FPGA and ASIC design. It supports PC, UNIX, and LINUX platforms, and is a simulator with a single kernel that supports mixed simulation of VHDL and Verilog. It uses direct optimization compilation technology, Tcl/Tk technology, and single kernel simulation. The compilation and simulation speed is the fastest in the industry. The compiled code is platform-independent, which is convenient for protecting IP cores. It has a personalized graphical interface and user interface, providing users with a powerful means to speed up debugging. It fully supports the IEEE standards of VHDL and Verilog languages, as well as the IEEE VITAL 1076.4-95 standard, supports C language function calls, C models, and SmartModel logic models and hardware models based on SWIFT.

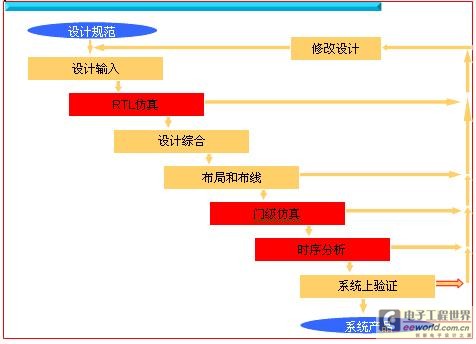

ModelSim supports RTL simulation, gate-level simulation, and timing simulation:

Main features

:

* Direct compilation structure is adopted, and the compilation and simulation speed is the fastest;

* Single kernel seamlessly performs VHDL and Verilog mixed simulation;

* Independent of machine and version, convenient for data migration and library maintenance;

* Machine-independent compiled code is used to protect and utilize IP;

* Simple and easy-to-use and rich graphical user interface, fast and comprehensive debugging;

* Tcl/Tk user-customizable simulator;

* Fully support VHDL/Verilog international standards, fully support Verilog 2001;

* Support numerous ASIC and FPGA manufacturer libraries;

* Integrated Performance analyzer helps analyze performance bottlenecks and accelerate simulation;

* Flexible execution mode, Debug mode can perform efficient debugging, and efficiency mode greatly improves simulation speed.

* Enhanced code coverage function Code coverage, which can report

various coverage conditions such as statement, branch, condition, * expression, toggle, fsm, etc., further improving the integrity of the test;

* The same waveform window can display multiple sets of waveforms, and can perform waveform comparison (Wave Compare) in multiple modes;

* Advanced Signal Spy function, which can easily access the signals of lower-level modules in VHDL or VHDL and Verilog mixed designs, facilitating design debugging;

* Support encrypted IP;

* Integrated C debugger, support for completing test platforms and modules in C language; support 64-bit OS;

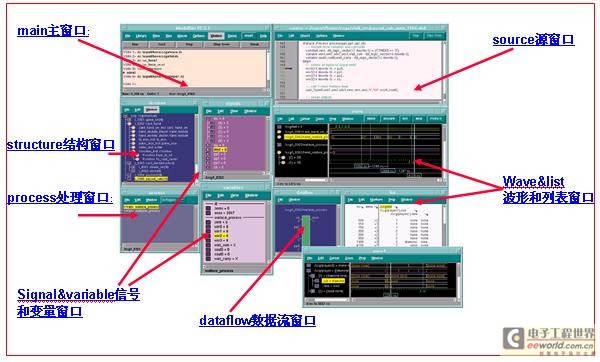

ModelSim user interface:

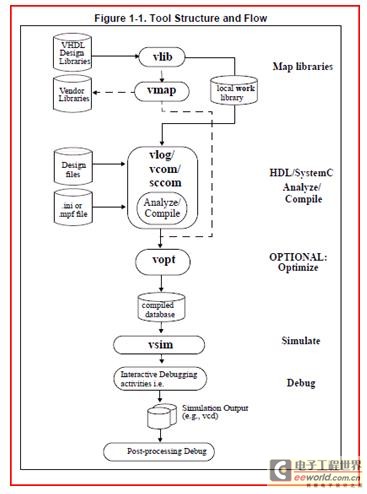

ModelSim design flow:

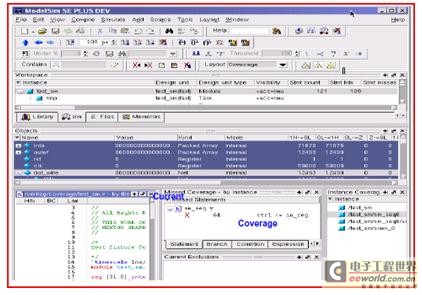

ModelSim coverage verification:

ModelSim Dataflow window:

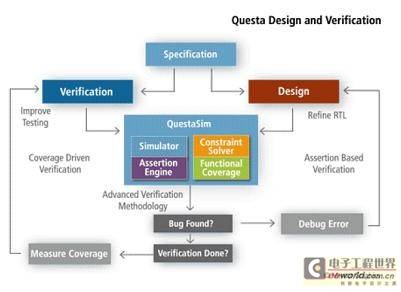

QuestaSim is the first standards-based single-core verification engine that integrates an HDL simulator, a constraint solver, a decision engine, functional coverage, and a common user interface.

Key Features:

*Built-in single core simulator supports SystemVerilog, Verilog, VHDL, PSL and SystemC.

* Built-in constraint interpreter supports constrained-random stimulus generation to achieve testbench-automation;

*Supports functional verification based on PSL and SystemVerilog language assertions, and supports the industry's most famous 0-in Checkware assertion library functional verification

*Integrated support for functional coverage checking and analysis

* High performance RTL and Gate-level simulation speed

*Support high-level testbench design and debugging using SystemVerilog and SystemC

* High-performance integrated mixed-language debugging environment accelerates cross-debugging and analysis of mixed verification languages (SystemVerilog, SystemC, PSL, VHDL, Verilog)

* Standards-based solutions can support all processes to protect investment in verification

* Provide the most cost-effective functional verification solution

Questa AFV provides true mixed language verification

Questa AFV is a single-core verification solution targeting mixed language flow.

It supports SystemVerilog, VHDL, PSL and SystemC at the same time, allowing designers to choose the most appropriate language.

In addition, the close connection with SystemVerilog verification capabilities and its use in

the generation of constrained random test platforms and functional coverage verification is also of great benefit to VHDL users.

The QuestaSim user interface is similar to ModelSim, and the commands are fully compatible.

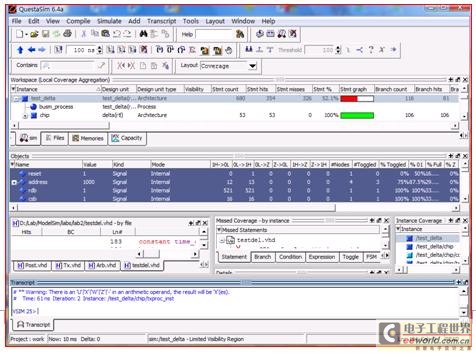

QuestaSim Coverage检查:

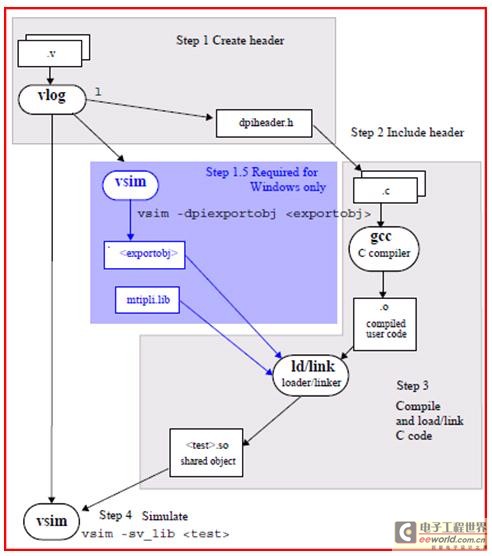

QuestaSim DPI Use Flow:

Previous article:EDA technology design scheme for electronic password lock

Next article:Quamtum-SI DDR3 Simulation Analysis

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- HGI HC32A460 series function comparison chart

- PCB drawing process shortcut keys

- How to start power supply design

- Has anyone tried the baud rate adaptation of LIN communication?

- Analog Electronics Design

- Will adding a nonlinear link to the RC bridge sine wave oscillation circuit cause waveform distortion?

- Introduction to TI_DSP link command file (*.cmd)

- [N32L43x Review] 2. Turn on the lights, blink, blink, blink...

- EEWORLD University Hall - Talking about the development creativity of electronic products and using network resources to help development

- The output of the op amp in the active integrator circuit oscillates. What should I do?

Vivado starts from now (Gao Runner-up)

Vivado starts from now (Gao Runner-up)

京公网安备 11010802033920号

京公网安备 11010802033920号