Developers can use the Configurable Logic Block (CLB) peripheral in the PIC16F13145 family of microcontrollers to implement complex discrete logic functions in hardware, thereby reducing the bill of materials (BOM) and developing custom application-specific logic.

In many embedded system applications, discrete logic devices, such as the 74'HC series, are often used. The advantage of these logic devices is that they can work independently of the microcontroller (MCU) and respond much faster than software. However, these devices increase the bill of materials (BOM) and require additional PCB area.

To address this issue, many of Microchip's microcontrollers integrate a peripheral called the Configurable Logic Cell (CLC) (on PIC® MCUs) or a similar peripheral called Configurable Custom Logic (CCL) (on AVR® MCUs). Both of these peripherals implement software-defined custom logic that can execute independently of the CPU. In other words, once the custom logic function is set, its behavior is independent of the microcontroller.

However, there is a limitation with these two peripherals, namely the amount of logic per instance is very small. Each CLC is roughly equivalent to a lookup table (LUT), while the CCL is equivalent to an instance with several independent LUTs inside. These two peripherals are very powerful and can be used to develop simple logic circuits, mix various signals together, and integrate with other hardware peripherals. For example, examples such as hardware button debounce, WS2812 output generation, and orthogonal decoding require the use of these two peripherals, but the number of these two peripherals in a single chip is not large, thus limiting the complexity of the application.

To support more complex applications, the PIC16F13145 family of microcontrollers introduces a new type of logic peripheral called the Configurable Logic Block (CLB), as shown in Figure 1. Note that the CLB does not replace the CLC or CCL peripherals, and a device can have both CLC/CCL and CLB.

Figure 1 - CLB Block Diagram

The CLB on the PIC16F13145 family of microcontrollers contains four logical groups, each containing eight BLEs. The BLEs in different logical groups are connected to each other - each logical group represents two GPIO outputs and an optional CPU interrupt. When the operating voltage is 5.5V, the propagation time of BLE is typically less than 6 ns. All BLEs in the entire structure share a common clock, and its clock source is configured in software together with an optional clock divider. The CLB can use one of the internal clock sources of the microcontroller or an externally provided clock source.

The peripheral is initialized from the microcontroller's memory, and the pins can then be controlled directly from its own structure through the Peripheral Pin Select (PPS). PPS allows the user to reassign I/O pins used for hardware peripherals, giving them greater design flexibility. For example, if the SPI clock previously used RA1, but it would be more beneficial to use RA6, then PPS can be used to remap the pins.

Other elements in the CLB include a dedicated 3-bit hardware timer with decoded output, edge detectors for input signals, and 32-bit output registers for debugging. Outputs of other Core Independent Peripherals (CIPs) on the microcontroller can be used as inputs to the CLB to enable more complex designs.

Since CLBs are much more complex than CLCs or CCLs, Microchip has developed a new tool called the CLB Synthesizer. The CLB Synthesizer provides a graphical interface for configuring the logic, as shown in Figure 2 below. In addition to logic primitives, the tool also supports a library of more advanced logic blocks (which can be pre-provided or customized by the user).

When interacting with the graphical tool, a Verilog module is automatically generated in the background for synthesis. If the developer prefers to write their own Verilog or has the file ready, it can be imported directly into the tool as a module.

Figure 2 – CLB synthesizer with the Phase Shift Keying (PSK) example turned on

The output of the CLB Synthesizer is an assembly file that contains a bitstream to set up the CLB and some source code to configure the CLB as a peripheral. The tool can be run through the MPLAB® Code Configurator (MCC) or a standalone online tool. MCC is a code generation utility that allows the user to set up and configure peripherals in the microcontroller using a visual interface. Once the hardware peripherals are configured, MCC will generate initialization code and device APIs.

At run time, the CLB bitstream is loaded directly from program memory using on-board hardware. The benefit of this implementation is that if the CLB configuration needs to be changed while the program is running, the loading process can be repeated with a different bitstream stored in device memory.

To demonstrate the application of the CLB, we have created a series of use case examples. Here we will discuss two examples: 7-segment display converter and SPI to WS2812 converter. The use case examples can be copied as building blocks to be used as part of a complete solution. The purpose here is to show the usefulness of this peripheral and the value it can bring to a design.

The first use case is a 7-segment display converter. 7-segment displays can be driven via a normal set of I/O pins, but standard implementations typically require the use of a software-defined lookup table to convert the input digits to the correct output pattern for the display. In this implementation, the CLB acts as a hardware lookup table. The desired output character (0 to F) is loaded from software into the CLB input register. Each output segment of the display is controlled by a LUT to map the input to the output.

This use case example was used internally to build a new control board for a timing system. The original user interface was developed in the 1980s using 74'HC series logic. With the CLB, a single 20-pin microcontroller was able to implement the display and keyboard logic on the board, greatly reducing the bill of materials (BOM). Figure 3 shows the two solutions side by side for comparison.

Figure 3 – Side-by-side comparison of the original PCB and the new PCB. This example was developed by Josh Booth.

The next example is an SPI to WS2812 converter. WS2812 is a single wire serial protocol used to control an LED array via pulse width modulation. In this example, the SPI hardware is used as a shift register for the data to be sent to the LEDs, while CLB is used to convert SCLK and SDO to the expected outputs.

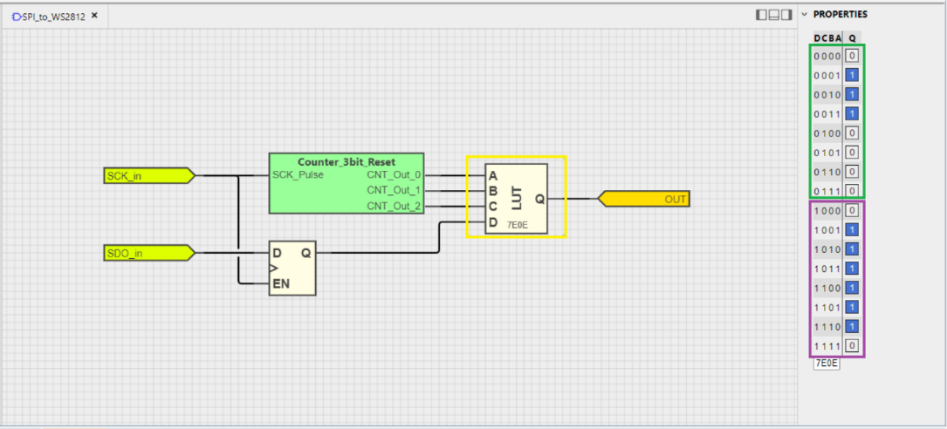

In this case, this is achieved with a one-shot 3-bit counter, a D latch with enable, and a 4-input LUT, as shown in Figure 4 below. The trick to this implementation is in the clock sources for the SPI and CLB. The SPI clock is set to idle high, change state on the rising edge, and run at the frequency of the WS2812 output (800 kHz), while the clock source for the CLB runs at 10 times the frequency of the former (8 MHz). When SCLK is low, the 3-bit counter is triggered and starts counting. When the count reaches 7 (0b111), the 3-bit counter stops and remains at 0 until the next low cycle of the clock pulse.

The output of the counter is fed into a 4-input LUT along with a latched version of the output data. This sets the output pattern of the data as shown on the right side of Figure 4. Once the counter is reset, the counter output remains at 0 to complete the cycle. The next byte in the SPI hardware can then be sent as needed and the cycle repeated.

Figure 4 – Block diagram of SPI to WS2812 converter (developed by Petre Teodor-Emilian)

Both examples demonstrate the advantages of discrete logic inside a microcontroller. Hardware peripherals free the CPU from various tasks, thereby improving response time and reducing power consumption while reducing the number of components. With CLB, complex applications that were previously impossible to implement inside a microcontroller can now be developed smoothly. Currently, you can purchase the PIC16F13145 series microcontroller from the Microchip direct sales website or other distributors to obtain CLB.

Robert Perkel is an applications engineer at Microchip. He is primarily responsible for editing technical content such as application notes, contributing articles and videos, analyzing use cases for peripherals, and developing code examples and demonstrations. Perkel graduated from Virginia Tech with a Bachelor of Science in Computer Engineering.

Previous article:Renesas Launches New RA8 Entry-Level MCU Product Group, Offering Cost-Effective, High-Performance Arm Cortex-M85 Processor

Next article:Infineon Technologies Launches Industry's First 20 Gbps Universal USB Peripheral Controller

- Popular Resources

- Popular amplifiers

- Learn ARM development(16)

- Learn ARM development(17)

- Learn ARM development(18)

- Embedded system debugging simulation tool

- A small question that has been bothering me recently has finally been solved~~

- Learn ARM development (1)

- Learn ARM development (2)

- Learn ARM development (4)

- Learn ARM development (6)

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

- CGD and Qorvo to jointly revolutionize motor control solutions

- CGD and Qorvo to jointly revolutionize motor control solutions

- Keysight Technologies FieldFox handheld analyzer with VDI spread spectrum module to achieve millimeter wave analysis function

- Infineon's PASCO2V15 XENSIV PAS CO2 5V Sensor Now Available at Mouser for Accurate CO2 Level Measurement

- Advanced gameplay, Harting takes your PCB board connection to a new level!

- Advanced gameplay, Harting takes your PCB board connection to a new level!

- A new chapter in Great Wall Motors R&D: solid-state battery technology leads the future

- Naxin Micro provides full-scenario GaN driver IC solutions

- Interpreting Huawei’s new solid-state battery patent, will it challenge CATL in 2030?

- Are pure electric/plug-in hybrid vehicles going crazy? A Chinese company has launched the world's first -40℃ dischargeable hybrid battery that is not afraid of cold

- The diameter of the four holes on the EK140 base plate

- This circuit is called a "lawn mower"

- CC3200-LAUNCHXL

- How to monitor battery voltage with Arduino

- Image Algorithm Transplantation to DSP and Its Optimization Steps

- Prize-winning live broadcast: Keysight’s Metaverse Test Series Seminar: Challenges in VR/AR Digital Interface Testing in Progress!

- 51 STM32 reference study manuals, one-click download without points!

- Microwave and RF Applications

- [ESP32-S2-Kaluga-1 Review] 3. Physical buttons?

- Unable to search for Bluetooth signal after adding characteristic value

TLE2062BMLB

TLE2062BMLB

京公网安备 11010802033920号

京公网安备 11010802033920号