Abstract: In order to design a high-precision signal source and reduce the design cost, the Cyclone II series low-end FPGA is used as the core, and the direct frequency synthesis technology is used to compress the sine signal and other data into ROM by 1/4 cycle. When the external clock frequency is 50 MHz, the design of the sine signal source is realized. At the same time, the digital modulation signals such as triangle wave, sawtooth wave, rectangular pulse and 2-ASK, 2-PSK and 2-FSK are realized. The system also has functions such as frequency sweep and specified waveform times. The simulation results show that the signal source has high precision, the frequency adjustment step can reach 0.034 92 Hz, the frequency range is 0.034 92 Hz~9.375 MHz, the production cost is low, and the function is rich.

0 Introduction

In recent years, the rapid development of electronic information technology has led to increasing requirements for signal sources in various fields. Not only do they require high frequency stability and accuracy, and convenient frequency change, but they also require the ability to generate arbitrary waveforms and output signals of different amplitudes. DDFS technology is a new type of direct frequency synthesis technology that has appeared since the 1970s. DDFS technology is proposed on the basis of the sampling theorem of signals. Starting from the concept of "phase", frequency synthesis can not only utilize the high frequency stability and high accuracy of crystal oscillation, but also the convenience of frequency change, fast conversion speed, and easy generation of arbitrary waveforms. Therefore, DDFS technology is the core technology of high-precision signal sources.

1 DDFS technical principle and related parameter calculation

The principle of DDFS technology: the sampled quantized data of the sinusoidal signal (or other signal) is stored in the ROM memory, and the data in the ROM is read sequentially or at certain intervals under the control of the clock, and then converted into an analog signal through the D/A conversion chip, and further passed through the low-pass filter and power amplifier circuit of the subsequent stage to realize frequency synthesis. Its main components include phase accumulator, data storage ROM table, D/A conversion, low-pass filter and power amplifier circuit.

According to the DDFS principle, the main parameters of DDFS include the number of sampling points N of the sinusoidal signal, the maximum output frequency fomax, the minimum output frequency fomin and the frequency resolution △fo, etc. This design is to generate a sinusoidal signal in the range of 1 Hz to 10 MHz with a step of 1 Hz. The parameter calculation is as follows:

1) The general formula of output frequency is fo

, where N is the number of sampling points and S is the step length.

, where N is the number of sampling points and S is the step length.

2) Output maximum frequency fomax

; According to Nyquist sampling theorem, at least two points must be sampled in one cycle to ensure the frequency information of the original signal. In engineering applications, at least 16 points or more must be sampled in one cycle to ensure the quality of the output signal. The maximum output frequency must reach 10 MHz, and the required system clock signal frequency fc is 160 MHz. Since the external crystal oscillator used in this article is 50 MHz,

the digital phase-locked loop (PLL) of

the CycloneII

series FPGA must be used to multiply the input clock to achieve the required clock frequency of 160 MHz. It can be multiplied by 3 to 150 MHz. At this time, the maximum frequency of the system output is: fomax=150 MHz/16=9.375 MHz. Although the operating frequency can be further increased by increasing the multiplication number of the phase-locked loop, thereby generating a higher output signal frequency, the maximum frequency at which it can work will restrict the multiplication number when designing the DDFS module.

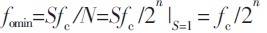

3) The minimum output frequency fomin

needs to be fc/N=1 Hz, then N=2n=150M, n=log2(150M)=[27.16]=28. That is, the sampling data in the ROM is 150M points, and the corresponding address bit data length of the addressing ROM is 28 bits.

; According to Nyquist sampling theorem, at least two points must be sampled in one cycle to ensure the frequency information of the original signal. In engineering applications, at least 16 points or more must be sampled in one cycle to ensure the quality of the output signal. The maximum output frequency must reach 10 MHz, and the required system clock signal frequency fc is 160 MHz. Since the external crystal oscillator used in this article is 50 MHz,

the digital phase-locked loop (PLL) of

the CycloneII

series FPGA must be used to multiply the input clock to achieve the required clock frequency of 160 MHz. It can be multiplied by 3 to 150 MHz. At this time, the maximum frequency of the system output is: fomax=150 MHz/16=9.375 MHz. Although the operating frequency can be further increased by increasing the multiplication number of the phase-locked loop, thereby generating a higher output signal frequency, the maximum frequency at which it can work will restrict the multiplication number when designing the DDFS module.

3) The minimum output frequency fomin

needs to be fc/N=1 Hz, then N=2n=150M, n=log2(150M)=[27.16]=28. That is, the sampling data in the ROM is 150M points, and the corresponding address bit data length of the addressing ROM is 28 bits.

4) Frequency resolution △fo △fo=fc/2n. It is known that the address bit of ROM is at least 28 bits. In this design, 32 bits are taken. The obtained fomin and △fo are 150M/232=0.03492 Hz.

5) ROM data 1/4 cycle compression The address bit length of the ROM is 32 bits, that is, the number of ROM units required will be 232. However, it is not necessary to store so many data points in the ROM, because the amount of data repetition is very large, and only a certain amount of points need to be stored. In this design, according to the data characteristics within the period of the sine signal, the (0, π/2) interval of the periodic sine signal is sampled at 1 024 points, quantized at 12 bits and stored in the ROM. This is equivalent to sampling 4 096 points in the (0, 2π) interval, and the ROM data volume is compressed to 1/4. At this time, the phase accumulator output address bit is correspondingly modified to 30 bits. In this way, when outputting data, the data in the (π, 2π) interval must be complemented. Because the sine signal data in this interval is negative.

6) ROM address bit length Through data compression, the ROM address only needs 10 bits. At this time, only the 30-bit address bit output value of the phase accumulator needs to be output, and the upper 10 bits are used for ROM addressing.

7) Step bit length The maximum step length should be 232/24=228, which is a 28-bit binary number.

2 FPGA Implementation of DDFS

The design principle diagram of the DDFS module in this design is shown in Figure 1. It mainly consists of an address generation unit (phase accumulator), a ROM storage unit, a complement code conversion circuit, and some data delay units. Each part of the work is described in VHDL language and a module is generated for calling in the top-level file.

Figure 1 FPGA implementation of DDFS

1) Phase accumulator (address generation unit) The design idea is to calculate the number of points m sampled in a 1/4 cycle according to the input STep value, and then count under the action of the clock. When the count value reaches m, it means that all points have been taken in a quadrant. At this time, the quadrant control word is incremented by 1, and the counting variable is reset to zero. At this time, the following 30-bit binary addresses (0, Step, ..., (m-1) Step) are generated in sequence. The upper 10 bits of this address can be intercepted to address the ROM space. According to the characteristics of the sinusoidal signal, the address generated in the next quadrant should be: ((m-1) Step, (m-2) Ste-p, ..., 0), and so on. And the quadrant control word is incremented.

2) ROM storage unit The data of ROM storage unit can be obtained by calculation through Matlab and stored as dds_sin.mif. Other high-level languages can also be used to obtain ROM storage data.

3) The complement code conversion circuit (0, π) data is directly output, and the data in the (π, 2π) quadrant should be subjected to complement code operation. By slightly modifying this complement code circuit, two sinusoidal signals with opposite phases can be output simultaneously.

4) Data Delay Unit In order to make the quadrant control word output by the address unit work with the asynchronous ROM, the corresponding data should be delayed to ensure the correctness of the output data. In this design, the phase control word is delayed by one clock cycle.

3 DDFS Design Module Performance and Resource Analysis

1) Timing analysis of DDFS module First, the maximum clock frequency fmax of DDFS module should be analyzed, because it determines whether the system can work at a clock frequency of 150 MHz or higher. Through the timing analysis of Timing Analyzer Tools provided by Quartus II 6.0, the fmax of DDFS module in this design is 179.18 MHz, which is higher than 150 MHz. Therefore, the theoretical maximum frequency of the sinusoidal signal that can be output by this design can reach 11.198 MHz.

2) DDFS module resource analysis The FPGA used in this design is Ahem's CycloneⅡ series chip EP2C5Q208C8. The designed DDFS module occupies only 2% of the on-chip resource logic units and 12,288 bits of data storage space, which is about 10% of the total data storage space of 119,808 bits. It can be seen that after the ROM storage table is processed, the DDFS module occupies less on-chip storage resources. Therefore, the ROM resources on the FPGA allow the call of several DDFS modules to complete various functional modules, such as 2-PSK, 2-FSK, 2-ASK and other digital modulations.

4 System Performance Simulation and Testing

Based on the DDFS module, this design realizes functions such as two sets of anti-phase sine signals, cosine signals, triangle wave signals, sawtooth waves, 2-PSK, 2-FSK, 2-ASK and other digital modulation signals, frequency sweep and arbitrary waveform output.

In this design, the simulation is mainly carried out through the Simulator Tool of QuartusII6.0. The correctness of the design can be verified from the simulation diagram. At the same time, the hardware verification of the logic function is carried out through the Signal TapⅡ logic analyzer of QuartusII6.0.

1) Basic sinusoidal signal output In this design, two groups of signals are generated simultaneously, one group is a sinusoidal signal, and the other group is inverted. Figure 2 is a sampling diagram of the sinusoidal signal Signal Tap II when the step length is set to (50 000 000) 10, and its frequency is fo = 582.076 6 kHz. At this time, the output signal is the highest frequency that can be generated. From the waveform of the obtained output signal, when the frequency is low, the curve is stable and smooth; when the frequency is high, the waveform distortion is not large, and the waveform can be further smoothed through the post-filter network. And the frequency stability is quite high.

Figure 2 Sine signal Signal Tap II sampling diagram when S = (50 000 000)10

At an external clock frequency of 50 MHz, the highest frequency that can be obtained is about 3.125 MHz, and the lowest frequency and frequency step can be as low as 11.64 MHz. When the external clock signal is multiplied to 150 MHz, the highest output frequency can reach 9.375 MHz, and the lowest frequency and frequency step can be as low as 34.925 MHz. Further improving the frequency and module performance can obtain signals with a larger frequency range.

In addition, it can be seen from the figure that the address output signal is actually a set of triangular wave signals with a frequency twice that of the sine signal. It can be seen that while generating a sine signal output, a set of 2-fold triangular wave output signals can also be generated. Just take the high 12 bits of the address as the output.

2) 2-ASK, 2-FSK, 2-PSK digital modulation signals It is relatively easy to generate digital modulation signals such as 2-ASK, 2-FSK, 2-PSK, etc. Just input the digital baseband signal into the module bit by bit under the action of its transmission clock signal, and use the '1' and '0' of the baseband digital signal to select the sinusoidal signal output with different amplitudes, frequencies or phases.

2-ASK signal: A 3.125 MHz signal is used to represent a digital signal's '1', and an output amplitude of 0 is used to represent a digital signal's '0'.

2-FSK signal: A 3.125 MHz signal is used to represent a digital signal'0', and a 582.077 kHz signal is used to represent a digital signal'1', as shown in Figure 3.

Figure 3 2-FSK signal word modulation signal

2-PSK signal: The '1' of the sinusoidal signal with an initial phase of 0 is used, and the '0' of the digital signal is represented by a signal with an initial phase of 180°, as shown in Figure 4.

Figure 4 2-PSK signal word modulation signal

3) Frequency sweep function The frequency sweep function is realized by changing the step. After each cycle of the sine signal is generated, the step is incremented. For the convenience of observation, the initial value of S is set to (50 000 000) 10, and the step increment is (10000000) 10. The frequency sweep function is realized, and the starting frequency of the frequency sweep is 582.077 kHz. The frequency sweep step is about 11*15 kHz. The frequency sweep signal is shown in Figure 5. At the same time, the synchronization information of each frequency signal can be provided. By changing the initial value of the step and the increment, a wider frequency sweep range and a better frequency sweep step can be achieved. In fact, FM signals can also be realized by controlling the step of the output signal.

Figure 5 Sweep frequency signal

5 Hardware Circuit Implementation

The ultimate goal of the design is to realize the circuit with hardware. Therefore, it is also necessary to design VHDL program modules such as the keyboard module for input step settings and mode selection, the frequency setting data display module, the low-pass filter network of the post-stage, the power amplifier circuit, etc. After completing these tasks, a complete DDFS signal source design and production can be completed.

6 Conclusion

The innovation of this paper is to optimize the DDFS design, make full use of the on-chip resources of the Cyclone II series FPGA, and generate a sinusoidal signal with a maximum frequency of 9.3125 MHz, a minimum frequency component and a frequency resolution as low as MHz. By further optimizing the performance of each DDFS module, such as reducing the operation time of modules such as the phase accumulator and data complement, further improving the maximum frequency of the system operation; further optimizing the characteristics of the post-stage filter network, etc., a high-quality signal source with a smoother performance curve, higher output frequency, and stronger load capacity can be obtained. At the same time, the FFT algorithm module can be added to perform other functions such as spectrum analysis on the signal.

Previous article:Design and implementation of efficient FIR filter based on FPGA

Next article:AD9910 Control Design Based on FPGA

Recommended ReadingLatest update time:2024-11-16 16:20

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Medical device requirements for chip temperature

- Send Chip Coins: #What to do when you encounter problems with Guoxin#, technical support is rubbed on the ground?

- 【RPi PICO】MicroPython firmware with encryption support

- I want to use a 3.3v microcontroller to share power to control a relay, but the microcontroller stops working after grounding.

- Welfare is coming! The recommended chip list for the TI Cup is freshly released!

- Based on RT-Thread open source works show - rice field environmental information monitoring system

- A brief introduction and configuration of 28335 external interrupt

- Analyze the relationship between J-link hardware, firmware, and drivers

- [ST NUCLEO-G071RB Review]_05_System clock configuration and Tetris game implemented on the serial port

- stm32F429 uses analog IIC to drive AD5933 to measure human body impedance (small impedance). After writing to the register, all the results read are FF.

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号