With the increasing requirements of various high-speed and long-term physical experiments, the system's demand for high-speed data acquisition modules is also increasing. In many special application occasions, the system also needs to collect and process a large amount of burst data. The high refresh rate and high resolution image acquisition system implemented with FPGA is used for shipborne radar image recording. The system consists of AD, FPGA, and SDRAM. The AD chip converts the image signal provided by the radar in the form of a VGA interface into a digital signal. The FPGA controls the timing and writes it into the SDRAM through the full-page burst mode, and provides an interface for subsequent processing.

China Classification Society stipulates that starting from 2004, all domestic and international ships must be equipped with shipborne voyage data recorders, of which shipborne radar image recorders are a very important part. Shipborne radar images are output according to VGA image standards, with a resolution of 640×480-1280×1024 and a refresh rate of 60-85Hz. Currently, most common image acquisition systems are aimed at the acquisition of composite video signals or CCD image signals. These image acquisition systems cannot meet the requirements of radar image acquisition. Even a few acquisition systems for high-resolution and high-refresh-rate images are in the form of computer boards, and require a computer when running.

At present, some VME bus-based data acquisition systems with a speed of up to 1GSPS can achieve data acquisition at a speed of 1GSPS through a 4-channel system with a collection speed of up to 250MHz per channel. However, since there is no large-capacity data cache in this type of system, high-speed and long-term data acquisition cannot be achieved. Other systems use an acquisition system based on FPGA, using multiple SDRAMs as data caches. This type of system solves the problem of long-term high-speed acquisition and can collect data with a frequency of 100MHz and a bit width of 16bit. However, since it uses multiple FIFOs to reduce the operating frequency of SDRAM, this type of system will have some data synchronization problems when used in high-speed image acquisition systems that require strict data synchronization. There is also a high-resolution image acquisition card in the form of a PC board. The system directly compresses the image and stores it, and provides it to the PC through the PCI interface. This form is not suitable for the small space on the ship, nor can it meet the data protection requirements when the ship is wrecked.

This paper proposes a high-resolution and high-refresh-rate image acquisition system. This system is used in embedded systems. It is not only small in size, but also solves the problem of data protection. It can be used in shipborne radar image recording systems. The system can support up to 4 8-bit data channels with a maximum sampling rate of 120MHz, or one VGA image signal, and can store the collected data for a long time. The specific continuous acquisition time varies depending on the capacity of the SDRAM used in the system. The system also provides an ASRAM interface for subsequent data processing, so that the SDRAM used to cache data can also be used as the system memory of the subsequent processing CPU. This can not only improve the data processing speed, facilitate the subsequent compression or recognition processing of radar images, but also save resources.

Acquisition system design

System Analysis and Chip Selection

First, determine the system requirements. The current standard stipulates that the VGA resolution is adjustable from 640×480 to 1280×1024, and the refresh rate is adjustable from 60 to 80Hz. The system should be able to accept the highest resolution of 1280×1024 and a refresh rate of 60Hz. In this case, the image pixel frequency is: 1280×1024×60=75MHz.

VGA is an analog interface used to provide image signals to analog devices such as displays. It has three analog signal components, RGB, and a horizontal and vertical synchronization signal, of which the horizontal and vertical synchronization signal is a pulse signal that complies with the TTL level. Since the analog VGA signal contains the vertical synchronization time, the horizontal synchronization time, and the blanking time, when the image is 1280×1024@60Hz, the pixel frequency after AD conversion is higher than the actual calculated 75MHz. Such a high sampling rate places high demands on AD. Therefore, the chip of Analog Device is used. The AD chip has 3 channels with a sampling accuracy of 8bit, a maximum sampling rate of 140MSPS, an analog bandwidth of 300M, and is specially optimized for computer and workstation image interfaces, which can meet the sampling of videos with a resolution of 1280×1024 and a refresh rate of 75Hz.

Since the sampling rate of AD is relatively high, the corresponding output data rate is also very high. Under the highest system requirements, the pixel frequency is 108MHz, and the corresponding data rate is 324Mbit/s (RGB3 components, 8bit each). At the same time, since the image data is collected, the system has high requirements for line synchronization, because if one or more points of data are lost in a line of image data, the entire image will be tilted, as shown in Figure 1. Figure a is the image obtained after correct collection, without tilt; Figure b is that the line collection data is less than the horizontal resolution of the display; Figure c is that the line collection data is greater than the horizontal resolution of the display. Therefore, it is necessary to store the data of each line in bursts to ensure that the data is not lost. The length of the burst is the horizontal resolution of the image.

From the above analysis, we can see that the timely storage of AD data is very demanding. Under extreme conditions, the system must store data at a burst length of 1280×3Byte at a frequency of about 110MHz. The traditional method of storing data in SDRAM through DSP cannot meet such a high speed and such a long burst length. Therefore, we use FPGA to directly control SDRAM storage. Considering the frequency and size of image data, we use SDRAM working at 133MHz.

Since the original image data is very large and requires a relatively large storage space, the collected image data must be processed later. Therefore, in addition to receiving the AD converted data and controlling SDRAM, FPGA also needs to provide an interface for the subsequent processing of the image.

In summary, FPGA needs to realize the following functions: synchronously receive data collected by AD; read and write SDRAM; provide subsequent image processing interface; provide control interface.

The design uses the FPGA EP1C6 of the Cyclone series of Altera. The EP1C6 has two phase-locked loops, contains 5980 logic units, equivalent to a scale of 120,000 gates, and also contains a maximum frequency of 200MHz and 92160bit internal RAM. The frequency and pin IO resources of the chip can well meet the requirements of this system.

Overall Design

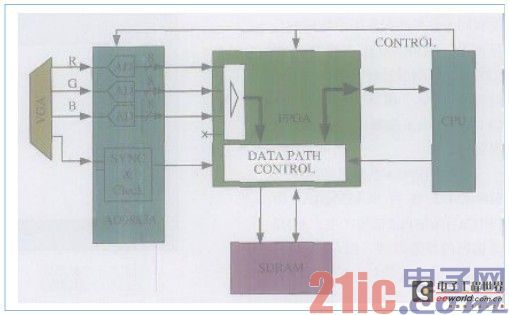

The overall block diagram of the acquisition system is shown in Figure 2.

[page]

[page]

The acquisition system consists of AD, FPGA, SDRAM and main CPU. The whole system is controlled by CPU. When acquiring, the CPU first determines the resolution and refresh rate of the image according to the horizontal and vertical synchronization signals, and sets AD and FPGA accordingly. Secondly, the CPU enables FPGA to acquire. After acquiring one frame, the CPU can process the image data.

The AD module can collect multiple VGA image formats, but it cannot automatically detect the image format. It must be set through the IIC interface it provides. We implement automatic detection of image formats in the main CPU and set the AD module. In addition, the effective pulse level of the field synchronization signal in VGA images of different formats is not unified. The AD module can automatically detect the polarity of the input field synchronization signal and indicate it in the internal register. By reading the register, the polarity of the input VGA signal field synchronization can be determined. The field synchronization signal output by the AD module can achieve the inversion of the input field synchronization signal. The synchronization logic inside the FPGA only supports one effective level of field synchronization signal. Therefore, before acquisition, it is necessary to determine the polarity of the current input synchronization signal by reading the register inside the AD to determine whether the AD chip needs to be set to invert the field synchronization signal.

In order to facilitate the main CPU to control the FPGA, the FPGA provides an IIC interface. The main CPU can control the FPGA through the same IIC interface as the AD module. Set the size of the captured image, the image storage start address, the blanking time and other information to ensure the accuracy and completeness of the captured image size. At the same time, in order to facilitate the main CPU to process the image later, the FPGA converts the SDRAM that stores the image into an ASRAM interface and provides it to the CPU for processing, thereby directly mapping the space for storing the image to the CPU's addressing space. The CPU can quickly read and process the image data through DMA to improve system efficiency.

FPGA internal design

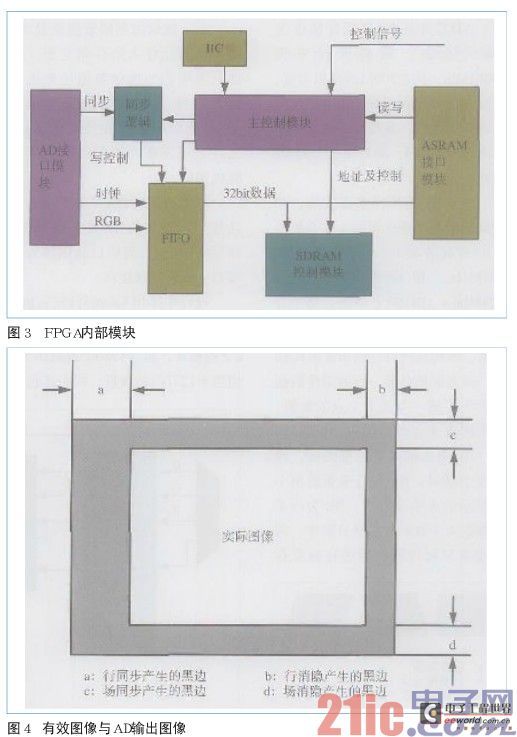

The internal modules of FPGA are shown in Figure 3.

The FPGA is composed of main control, SDRAM controller, AD interface, FIFO, ASRAM interface, IIC and other modules. The main control module is responsible for receiving the control signal of the CPU and coordinating the work between various modules. The SDRAM control module implements the operation logic of SDRAM. The AD interface module receives the data and synchronization signal output by the AD module and ensures the row and field synchronization of the image data. The ASRAM interface module converts the CPU's operation on ASRAM into the operation instruction on SDRAM. The IIC logic module receives the CPU's various parameter settings and controls for the FPGA acquisition system. [page]

The main clock frequencies of the system FPGA are the SDRAM operating frequency of 133MHz, which is generated by the PLL multiplication of the EP1C6; the pixel clock output by the AD module is generated by the PLL inside the AD chip, and the clock in the IIC module is generated by the CPU. The clock output by the AD chip has a relatively large range of variation, from 25-108MHz, depending on the input image format, while the read and write clock of the SDRAM is fixed at 133MHz. Therefore, a FIFO must be added between these two clocks of different frequencies for synchronization. The FIFO uses the free IP core provided in the QuartusII software and is implemented by using the high-speed RAM inside the FPGA.

The AD module is responsible for the interface logic with the AD chip. The importance of synchronization in image acquisition has been analyzed above. If a row of data in the image is incomplete, the entire image will be affected. The AD module uses the line and field synchronization signals output by the AD chip to synchronize the image data. The AD chip outputs the dot frequency as the write clock of the FIFO module, and the combination logic of the line and field synchronization signals constitutes the write enable of the FIFO. In addition, since the analog VGA interface has line and field synchronization time and line and field blanking time, in order to ensure the accuracy and integrity of image acquisition, the AD chip requires that the dot frequency be set to 20%-30% larger than the actual effective dot frequency, because the line width and field width in the image after AD conversion are often larger than the actual image, resulting in a relatively large black edge on the image. As shown in Figure 4. In order to obtain accurate image data, the AD module sets a counter to filter the black edge at the beginning of the image. Its count value can be set through the IIC interface.

SDRAM has multiple burst modes with different lengths. In this design, since the maximum frequency of AD output is close to 110MHz, the length of burst storage is relatively long. In order to ensure that data can be stored in time, the SDRAM with an operating frequency of 133MHz must work in the full-page burst mode to achieve the highest data throughput.

In order to improve versatility, this design converts the SDRAM interface into an ASRAM interface and provides it to the main CPU, avoiding the trouble of switching SDRAM control rights caused by the difference between the SDRAM operating frequency and the CPU external clock, and improving compatibility with various CPUs. The ASRAM interface logic realizes the mapping of CPU addresses to SDRAM addresses and the conversion of operation timing. The main control module generates corresponding SDRAM control instructions to control SDRAM reading and writing. The operation of SDRAM is transparent to the CPU.

The acquisition system can also acquire 4 8-bit AD channels, because the AD logic module inside the FPGA provides a 32-bit interface, and the VGA acquisition method only uses 24 bits. When using the 4-channel 8-bit mode, only the front-end AD part needs to be adjusted.

Practical Application

In the performance requirements of China Classification Society for shipborne voyage data recorders, it is required that the shipborne voyage data recorder should be able to connect to the video cache output of the radar display whose image is to be recorded. Through the dedicated radar cache output interface, the data recorder needs to record a series of single and full-screen video frames. The resolution of the display designed for this requirement should be between 640×350 and 1280×1024, and the refresh rate should be between 60-85Hz. This design can fully meet this requirement.

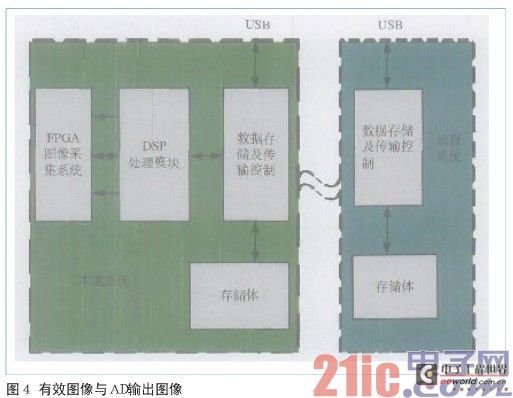

Figure 5 shows the complete radar image recording system block diagram.

In general, the system consists of two parts: the local system and the remote system. The local end is responsible for the acquisition, compression and storage backup of radar images. The remote system saves a copy of the radar image. The local system consists of three parts: acquisition, processing, and storage and transmission. The acquisition part is the radar image acquisition system with FPGA as the core mentioned above. The processing part uses TI's C6000 series DSP as the system's CPU. The main chip of the storage and transmission part uses Samsung's SOC chip S3C2410. The storage body uses multiple large-capacity NAND Flash.

The remote system is the same as the storage and transmission part of the local system. It is only responsible for the storage of radar images.

The local system and the remote system communicate with each other via 485 or Ethernet. At the same time, both the local system and the remote system provide USB interfaces. The images stored in the device can be read through the USB interface on the computer, and the device parameters can be set.

The high-speed image acquisition system introduced in this paper fully realizes the expected functions. It can acquire radar images with a maximum resolution of 1280×1024 and a refresh rate of 60Hz, and provide the image data to the CPU for subsequent processing through the ASRAM interface.

The acquisition system is suitable for embedded systems and has been successfully used in shipborne radar data recorders to achieve radar image acquisition and pass actual tests. The main performance is as follows: the image acquisition resolution is adjustable from 640×350 to 1280×1024, the refresh rate is adjustable from 60-85Hz, and the radar image can be saved for 24 hours with an acquisition interval of 15s, and the radar image can be reproduced on the computer through the USB interface.

In addition, this acquisition system realizes the acquisition of high-speed burst-length data and provides a relatively universal control and access interface, so that the application of the system is not limited to the acquisition of radar images. By modifying the front-end AD module, the system can also simultaneously acquire data from 4 AD channels with a bit width of 8 bits and a maximum sampling rate of 120MHz, making it suitable for other occasions that require high-speed acquisition. It has strong versatility.

Previous article:Application of CPLD in signal filtering and anti-interference

Next article:Application reference of programmable logic devices

Recommended ReadingLatest update time:2024-11-16 19:27

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- TI Cortex MCU Industrial Safety Applications

- [Raspberry Pi Pico Review] WS2812B Snowflake Light Practice -- and IoT Communication RGB Control

- How to convert a sine wave into a square wave

- If you want to work in electronics, you need to remember these English words!

- Decoupling Technology

- Bluetooth 4.0 BLE Development Complete Manual: Practical IoT Development Technology

- UltraISO, English learning .iso files made on PC, cannot be played?

- How to calculate the saturation of an inductor with a magnetic core? Is there a calculation formula for reference?

- What is the difference between the PLL input clock (1) the clock generated by the XTH crystal oscillator and (2) the clock input from the XTH pin PD00?

- Summary: GigaDevice GD32F350 Innovation Design Competition Participants' Shared Content

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号