Meeting demanding frequency synthesizer requirements often requires a certain degree of design flexibility. Basic phase-locked loop (PLL) frequency synthesizers have been at the heart of radio frequency (RF) systems for some time, providing reasonable spectral purity and frequency agility in a low-cost, space-efficient, low-power package. However, where fast switching speeds, low phase noise, or low spurious signal levels are required, more complex architectures are necessary. With the right design approach, the combination of modern low-cost, highly integrated PLL and direct digital synthesizer (DDS) integrated circuits (ICs) can greatly facilitate the realization of high-performance architectures.

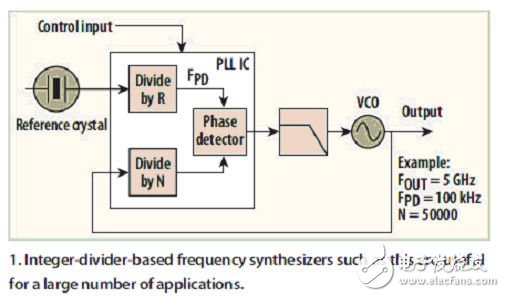

Most high-frequency systems use either a traditional integer-divider-based design (Figure 1) or a fractional-N-divider-based design. Regardless of which design is used, the required functionality is usually achieved using a single general-purpose frequency synthesizer IC in conjunction with an external voltage-controlled oscillator (VCO). The VCO function can be implemented using an IC, module, or discrete component solution, or even inside the synthesizer chip, depending on the required frequency range, phase noise performance, and space, cost, and power constraints. The final design is usually based on the manufacturer's application notes, and functions such as loading the synthesizer's registers and setting the phase detector gain can usually be accomplished using a downloadable application.

Figure 1: Frequency synthesizers based on integer dividers like this one are useful for many applications.

However, for some very demanding applications, the performance of the basic architecture may be far from sufficient, especially in terms of phase noise, spurious signal levels, and frequency switching speed. Frequency synthesizers used in Doppler radar systems and communication systems operating at microwave frequencies that use fast frequency switching and/or high-order modulation schemes are good examples of such applications.

For example, if an application requires an integer PLL synthesizer with a high output frequency and a relatively small tuning step size (which means a high division ratio), this will result in a very high phase noise floor within the loop bandwidth (because the phase detector noise will increase by 20log(N) relative to the output). For example, the required division ratio is 50,000 for a 5GHz output frequency and 100kHz channel spacing, which will result in a 94dB loop bandwidth noise floor that exceeds the phase detector noise (typically about -75dBc in 1Hz bandwidth). Typical fractional-N frequency synthesizer ICs can achieve a noise specification of about -85dBc in 1Hz bandwidth.

Although direct analog frequency synthesizers (generally consisting of switch-selectable frequency multipliers, mixers, and filters) may be superior in terms of switching speed and phase noise, their implementation is usually too complex, especially when good spurious signal performance is required. Direct digital synthesizers (DDS) can provide fine tuning steps, fast frequency switching speeds, and good phase noise, but cannot directly provide microwave frequency outputs without additional frequency multipliers.

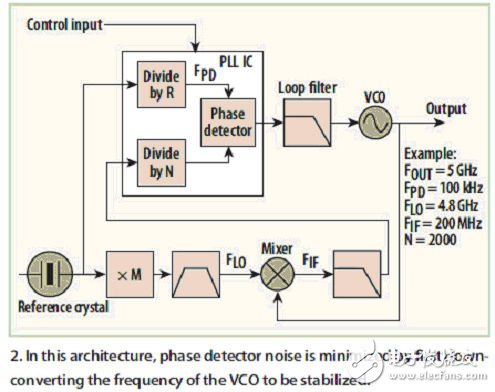

While not specifically designed for this purpose, PLL and DDS type devices developed for more common applications can often be used as building blocks in more complex, higher performance architectures. Figure 2 shows an example of a PLL-based architecture that can be used to improve phase noise performance. In this example, the VCO output is downconverted to a much lower frequency before connecting to the synthesizer IC input. This reduces the required division ratio, thereby reducing the noise contribution from the phase detector. For the example shown, the division ratio would be reduced from 50,000 to 2,000, and the phase noise floor limit within the loop bandwidth would be improved by 28 dB to -103 dBc. For wideband applications, multiple stages of downconversion can be used, with the local oscillator (LO) frequency selected by switches to keep N low.

Figure 2: In this architecture, phase detector noise is minimized by first downconverting the VCO frequency to be stabilized.

The architectural changes are also very useful in achieving fast frequency switching times. The time required for a PLL to settle to a new frequency is inversely proportional to the loop bandwidth. In simple architectures, the requirement for small channel frequency spacing means using a narrow loop bandwidth, which results in a slower frequency step settling time for the loop. In integer PLL-based designs, the reference frequency will be equal to this frequency step size, and the loop bandwidth must be approximately an order of magnitude smaller than this step size. In fractional-N based designs, while the reference frequency can be maintained at much higher values, the loop filter must still typically provide high attenuation for signals that fall at multiples of the step size, placing an upper limit on the loop bandwidth. However, by using a DDS as a high frequency reference source within the PLL, the division ratio can be kept low (thus minimizing noise) while achieving very small frequency steps without constraining the loop bandwidth.

Modern DDS ICs can produce outputs in the very high frequency (VHF) range in a very small package with MHz tuning steps and excellent phase noise. Frequency and phase modulation functions are usually included. The level of close-in spurious signals depends on the phase lookup table resolution and the output digital-to-analog converter (DAC) and is generally very good (about -80dBc); however, other sampled signals will be present at the output at very high levels. By using the DDS IC as a frequency reference source in the PLL, the output frequency can be converted to any frequency required, and the unwanted sampled signals can be filtered out by the PLL efficiently. Figure 3 shows an example of this architecture.

Figure 3: In this approach, a DDS is used as a frequency reference source in a phase-locked loop synthesizer.

The PLL can be thought of as providing a tracking filter function, which is beneficial because it greatly attenuates unwanted sampled signals at the output of the DDS as well as other signals generated by the down-conversion process. Depending on the tolerable spurious signal levels, the PLL can be required to provide little or no additional attenuation of the already low level near-end spurious signals. In this way, the loop bandwidth of the PLL can be kept much larger than the actual bandwidth in a traditional PLL synthesizer, thereby increasing the frequency switching speed. The PLL reference frequency can be made much higher than the DDS frequency step size, and the division ratio is very small, thereby achieving excellent phase noise performance. Since a larger loop bandwidth is equivalent to a larger loop gain at a specific offset, and the noise contribution from the phase detector is lower, the noise component contributed by the VCO can also be effectively reduced.

It is important to note that the details of frequency planning in this architecture must be carefully considered. The frequencies of the reference oscillator, DDS clock source, and PLL reference source must be carefully selected relative to the required channel spacing to minimize the complexity of the required reference generation hardware and to avoid the generation of near-end spurious signals that cannot be filtered out.

As mentioned above, many DDS ICs have frequency and phase modulation capabilities, and these functions may be used in situations where a modulated output is required, such as generating a linear frequency ramp required by a frequency modulated continuous wave (FMCW) radar system. In practical applications, in order to minimize spurious signal outputs, it is better to add modulation circuits using a more sophisticated architecture, such as through an additional tracking loop, as shown in Figure 4.

Figure 4: To minimize spurious outputs, the correct approach is to add modulation circuits using a more sophisticated architecture, such as through additional tracking loops.

特别是在宽带系统中,通过使用前馈技术可以极大地提高频率切换速度,案例见图5。当接收到一个改变频率的命令时,环路被断开,VCO控制电压随后受DAC的控制,并到达一个预期对应所需新输出频率的值。接着环路再次闭合,同时PLL开始消除任何残留的相位与频率误差。在实际应用中,控制电压会很快调整到接近要求的值,而且由于PLL只需消除很小的残留误差,因此系统总的稳定时间将得到显著缩短。注意,除了加快稳定过程外,这种安排实际上在环路中使用许多频率转换级的宽带系统中已被证明是非常有用的,而如果不这样做的话,PLL可能没有足够的捕获带宽来稳定大的步长。为了实现信道改变过程中严格受控的时间顺序,控制逻辑功能最好由FPGA来完成。在实际使用时,对于拥有串行控制接口的器件来说,写入要求的寄存器数据所需的时间可能是决定可以实现的切换时间中最重要的因素。

Figure 5: This feed-forward technique can increase the frequency switching speed of the synthesizer.

A practical microwave frequency synthesizer based on the above techniques can simultaneously achieve low spurious signal levels, fast switching speeds, and excellent phase noise, while also providing frequency modulation (FM) and phase modulation capabilities. By carefully selecting the architecture and frequency planning, and using modern PLL synthesizers and DDS ICs under field-programmable gate array (FPGA)-based logic control, we can achieve this high-performance design in a power-efficient and space-efficient package (Figure 6).

Figure 6: Combining PLL and DDS ICs in an FPGA-controlled architecture can provide the required performance level in a power- and space-efficient package.

Previous article:Design of Fire Control Computer Interface Circuit

Next article:How to choose filter design software

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- 【MicroPython】Programmable USB Hub

- [Repost] PCB Design Inspection Specification Guide

- RDDI-DAP Error

- How semiconductor technology is changing the automotive lighting roadmap

- Explain the CM3 core clock source in easy-to-understand terms

- BlueNRG-1 drives WS2812B full-color light bar to simulate Audi's flowing water effect turn signal

- Have you overlooked the design of the pad in PCB design?

- Is there such a pressure sensor?

- Thank you for being there + thank you for persisting

- Embedded OTA air download technology

ICCV2023 Paper Summary: Video Analysis and Understanding

ICCV2023 Paper Summary: Video Analysis and Understanding Signal Integrity and Power Integrity Analysis (Eric Bogatin)

Signal Integrity and Power Integrity Analysis (Eric Bogatin)

京公网安备 11010802033920号

京公网安备 11010802033920号