3-wire full-duplex synchronous transmission

Two-wire simplex synchronous transmission without a third bidirectional data line

8 or 16 bit transmission frame format selection

Master or slave operation

8 modes baud rate division coefficients

Slave Mode Frequency

Fast communication in master and slave modes: maximum SPI speed reaches 18MHz

Both master and slave modes can be managed by software or hardware: Dynamic change of master/slave operation mode

Programmable clock polarity and phase

Programmable data order

Dedicated transmit and receive flags that can trigger interrupts

SPI bus busy status flag

Hardware CRC for reliable communication

Usually SPI is connected to external devices through 4 pins

MISO: Master input/slave output pin, this pin sends data in slave mode and receives data in master mode

MOSI: Master device output/slave setting input pin, this pin sends data in master mode and receives data in slave mode

SCK: serial port clock, output of the master device and input of the slave device

NSS: Slave Setting Selection, this is an optional pin used to select the master/slave setting. Its function is to be used as a chip select pin, so that the master device can communicate with a specific slave device alone to avoid conflicts on the data line. The NSS pin of the slave device can be driven by the master device as a standard IO. Once the SSOE bit is enabled, the NSS pin can also be used as an output pin and pulled low when the SPI is set to master mode. At this time, all SPI devices whose NSS pins are connected to the NSS pin of the master device will detect the low level. If they are set to NSS hardware mode, they will automatically enter the slave device state.

Phase and polarity of clock signals

The CPOL and CPHA bits of the SPI_CR register can be combined into four possible timing relationships. The CPOL (clock polarity) bit controls the idle state level of the clock when there is no data transmission. This bit is valid for devices in master mode and slave mode. If CPOL is cleared to 0, the SCK pin remains at a low level in the idle state; if CPOL is set to 1, the SCK pin remains at a high level in the idle state

If the CPHA clock phase bit is set to 1, the second edge of the SCK clock (the falling edge when the CPOL bit is 0, the rising edge when the CPOL bit is 1) samples the data bit, and the data is latched on the second clock edge.

The combination of CPOL clock polarity and CPHA clock phase selects the clock edge for data capture.

SPI Slave Mode

In the slave configuration, the SCK pin is used to receive the serial clock from the master device. The setting of BR in the SPI_CR1 register does not affect the data transmission rate.

Configuration steps

1. Configure the DFF bit to define the data frame format as 8 bits or 16 bits

2. Select CPOL and CPHA bits to define the phase relationship between data transmission and serial clock. To ensure correct data transmission, the CPOL and CPHA bits of the slave device and the master device must be configured in the same way.

3. The frame format (MSB first or LSB first depends on the LSBFIRST bit in the SPI_CR1 register) must be the same as the master device

4. In hardware mode, the NSS pin must be low during the complete data frame transmission process. In software mode, set the SSM bit in the SPI_CR1 register and clear the SSI bit.

5. Clear the MSTR bit and set the SPE bit to make the response pin work in SPI mode

In this configuration, the MOSI pin is the data input and the MISO pin is the data output.

Data sending process

Data words are written in parallel to the transmit buffer

When the slave receives the clock signal and the first data bit appears on the MOSI pin, the transmission process starts, the first bit is sent out, and the remaining bits (for 9-bit data frame format, there are 7 bits; for 16-bit data frame format, there are 15 bits) are loaded into the shift register. When the data in the transmit buffer is transferred to the shift register, the TXE flag in the SPI_SR register is set. If the TXEIE bit on the SPI_CR2 register is set, an interrupt will be generated.

Data receiving process

For the receiver, when data reception is completed

The data in the shift register is transferred to the receive buffer and the RXNE flag in the SPI_SR register is set.

If the RXEIE bit of the SPI_CR2 register is set, an interrupt is generated

After the last sampling clock edge, the RXNE bit is set to 1, the received data byte in the shift register is transferred to the receive buffer, and the SPI device returns this value when the SPI_DR register is read. When the SPI_DR register is read, the RXNE bit is cleared.

SPI Master Mode

In master configuration, the serial clock is generated on the SCK pin.

Configuration steps

1. Define the serial clock baud rate through the BR bit of the SPI_CR1 register

2. Select CPOL and CPHA bits to define the phase relationship between data transmission and serial clock

3. Set the DRR bit to define the 8-bit or 16-bit data frame format

4. Configure the LSBFIRST bit of the SPI_CR1 register to define the frame format

5. If the NSS pin needs to work in input mode, the NSS pin should be connected to a high level during the entire data frame transmission in hardware mode; in software mode, the SSM and SSI bits of the SPI_CR1 register need to be set. If the NSS pin works in output mode, only the SSOE bit needs to be set.

6. MSTR and SPE bits must be set

In this configuration, the MOSI pin is the data output and the MISO pin is the data input.

Data sending process

The transmission process starts when a byte is written into the transmit buffer.

When sending the first data bit, the data word is transferred in parallel (through the internal bus) into the register, and then overflows serially to the MOSI pin; whether the MSB is online or the LSB is online depends on the LSBFIRST bit in the SPI_CR1 register. The TXE flag will be set when the data is transferred from the transmit buffer to the shift register. If the TXEIE bit in the SPI_CR1 register is set, an interrupt will be generated.

Data receiving process

For the receiver, when the data transmission is completed

The data in the shift register is transferred to the receive buffer and the RXNE flag is set.

If the RXEIE bit in the SPI_CR2 register is set, an interrupt is generated.

At the last sampling clock edge, the RXNE bit is set, and the data word received in the shift register is transferred to the receive buffer. When the SPI_DR register is read, the SPIU device returns the received data word, and reading the SPI_DR register will clear the RXNE bit.

Once the transmission starts, if the next data to be sent is placed in the transmit buffer, it can be a continuous transmission stream. Before trying to write to the transmit buffer, make sure that the TXE flag should be 1.

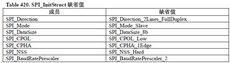

SPI_InitTypeDef SPI_InitStructure;

RCC_APB1PeriphClockCmd(RCC_APB1Periph_SPI2,ENABLE);

SPI_Cmd(SPI2, DISABLE); //Must disable before changing MODE

SPI_InitStructure.SPI_Direction =SPI_Direction_2Lines_FullDuplex; //Two-line full-duplex

SPI_InitStructure.SPI_Mode =SPI_Mode_Master; //Master

SPI_InitStructure.SPI_DataSize =SPI_DataSize_8b; //8-bit

SPI_InitStructure.SPI_CPOL =SPI_CPOL_High; //CPOL=1 clock floating high

SPI_InitStructure.SPI_CPHA =SPI_CPHA_1Edge; //CPHA=1 data capture second

SPI_InitStructure.SPI_NSS =SPI_NSS_Soft; //Software NSS

SPI_InitStructure.SPI_BaudRatePrescaler =SPI_BaudRatePrescaler_2; //2-division

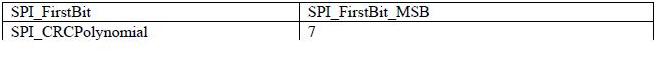

SPI_InitStructure.SPI_FirstBit =SPI_FirstBit_MSB; //High bit first

SPI_InitStructure.SPI_CRCPolynomial =7; //CRC7

SPI_Init(SPI2,&SPI_InitStructure);

SPI_Cmd(SPI2, ENABLE);

//The spi configuration is complete and can be used.

You can also use the SPI_StructInit function to fill in each parameter in SPI_InitStruct with the default value.

_____________________________________________________________________________________

Transmit buffer empty flag (TXE) [3.0 SPI_I2S_FLAG_TXE]

When this flag is '1', it indicates that the transmit buffer is empty and the next data to be sent can be written into the buffer. When writing SPI_DR, the TXE flag is cleared.

Receive buffer not empty (RXNE) [3.0 SPI_I2S_FLAG_RXNE]

When this flag is '1', it indicates that the receive buffer contains valid receive data. Reading the SPI data register can clear this flag.

Note that in the 2.0 library function

SPI_SendData SPI_ReceiveData SPI_GetFlagStatus etc. are changed to

SPI_I2S_SendData SPI_I2S_ReceiveData SPI_I2S_GetFlagStatus

Write a send/receive function

static u8 SPIByte(u8 byte)

{

while((SPI2->SR &SPI_I2S_FLAG_TXE)==RESET);

//while((SPI_I2S_GetFlagStatus(SPI2,SPI_I2S_FLAG_TXE))==RESET);

SPI2->DR = byte;

//SPI_I2S_SendData(SPI2,byte);

while((SPI2->SR &SPI_I2S_FLAG_RXNE)==RESET);

//while((SPI_I2S_GetFlagStatus(SPI2,SPI_I2S_FLAG_RXNE))==RESET);

return(SPI2->DR);

//returnSPI_I2S_ReceiveData(SPI2); read register and clear flag by hardware.

//SPI_I2S_ClearFlag(SPI2,SPI_I2S_FLAG_RXNE); clear flag by software directly.

}

Previous article:STM32 DMA Understanding

Next article:STM32 EXIT

- Popular Resources

- Popular amplifiers

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

- Keysight Technologies Helps Samsung Electronics Successfully Validate FiRa® 2.0 Safe Distance Measurement Test Case

- Innovation is not limited to Meizhi, Welling will appear at the 2024 China Home Appliance Technology Conference

- Innovation is not limited to Meizhi, Welling will appear at the 2024 China Home Appliance Technology Conference

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Download from the Internet--ARM Getting Started Notes

- Learn ARM development(22)

- Learn ARM development(21)

- Learn ARM development(20)

- Learn ARM development(19)

- Learn ARM development(14)

- Please give some advice on the working mode of the boost circuit

- Gowin GW1N development board logic analyzer speed test

- Which MSP430FR6972 development board is suitable?

- Please recommend some easy-to-understand books or web links about phase detectors and frequency detectors. Thank you.

- PS2 Interface.pdf

- DIY a CNC switching power supply, you need to master these knowledge

- General architecture of the hardware system of the C6000 series DSP

- Two symmetrical cascade amplifiers in one cavity + layout looks very pleasing to the eye

- Mini2440 serial communication

- State Machine Design-English.pdf

5962-8767401CX

5962-8767401CX

京公网安备 11010802033920号

京公网安备 11010802033920号