"In the past decade, the growth rate of verification costs has been much higher than that of design. In the entire front-end design, verification resources including engineers, software, and hardware will account for 70% of the total, while design only accounts for 30%. This shows that the proportion of verification in the entire work will become higher and higher." said Ling Lin, global vice president of Siemens EDA and general manager of China.

With the development of technology, the number of transistors has reached the level of tens of billions, and the complexity of SoC has increased exponentially. In order to meet the stringent development cycle and development efficiency, the demand for hardware simulation has continued to increase, and in 2018, the growth in spending officially surpassed RTL simulation, despite the higher overhead compared to RTL simulation.

Precisely because of the importance of hardware-assisted verification, the three EDA giants now have corresponding hardware-assisted verification systems, including Siemens EDA's Veloce, Synopsys' Zebu and Cadence's Palladium.

Ling Lin said: "The cost of SoC software verification is growing rapidly and has surpassed traditional hardware verification. This is because the software environment in which SoC is located is becoming more and more complex and large in scale. At the same time, hardware such as power supply and analog mixed signal not only need to verify their own functions, but also need to be co-verified in the operating system or other software environments."

The cost of verification is becoming increasingly high

Li Liji, technical director of Siemens EDA Asia Pacific, also believes that nowadays, to ensure the success of chip development and market acceptance, it is no longer a matter of competing on the level of functionality, but rather on the performance of the software. "So during the chip development process, the software needs to be run directly on the chip to collect data. During the design process, the workload needs to be placed on the chip, and performance and power consumption analysis and optimization need to be performed at the same time. Therefore, verification needs to be involved early in the design process, including comprehensive verification and optimization of functions, performance, and power consumption."

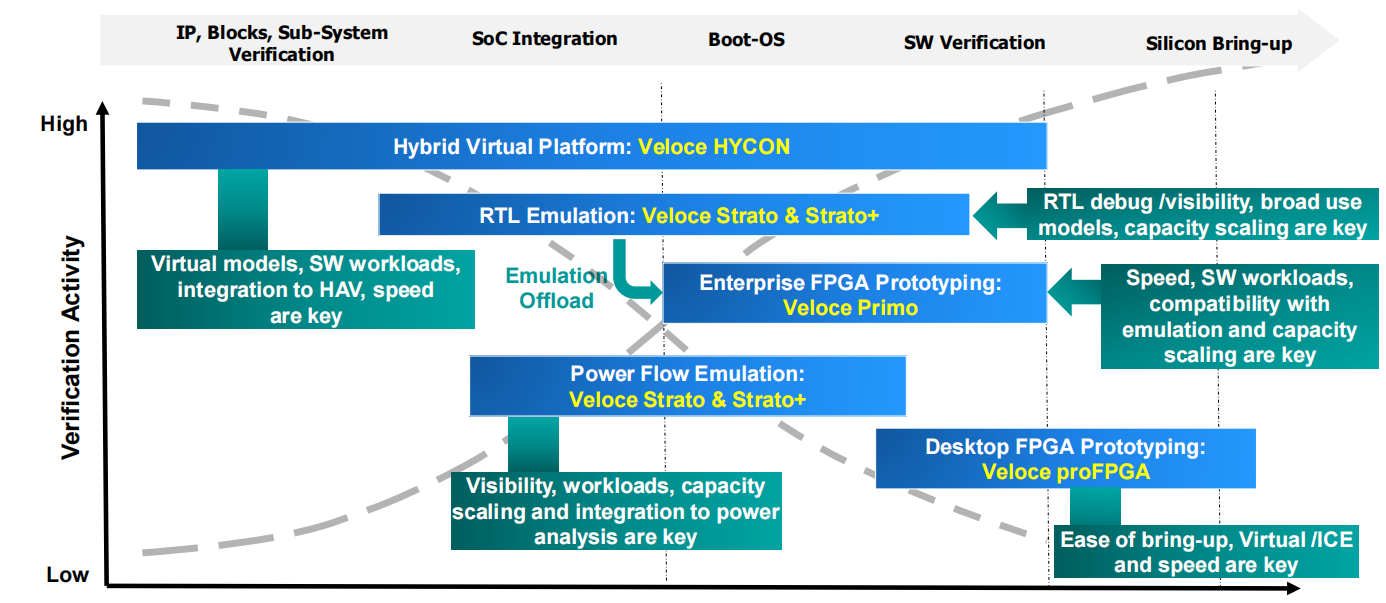

The importance of verification in each link

Li Liji took the entire design process as an example to introduce the specific steps of simulation verification.

The first is the virtual verification stage, which is to conduct targeted evaluation and verification through hardware simulation of various IPs in the chip. The biggest benefit of virtual verification is that it realizes software-defined SoC, so the overall design time is greatly shortened. Through the combination of software and hardware, problems can be discovered early and the design direction can be guided, meeting the shift-left concept in the design methodology. At the same time, the CPU is not implemented using RTL, so the running speed is quite fast, up to 100 MIPS.

Later, as the hardware design begins to improve and various unstable factors need to be debugged, some visible hardware acceleration is needed to assist in debugging.

Third, after the chip is more perfect, it is necessary to evaluate power consumption and performance, extract and analyze, and import software workloads into hardware emulators for evaluation.

Fourth, as the chip approaches maturity, it needs to be simulated systematically and integrated into the entire hardware system to confirm the interaction between systems so that it can be transferred to the FPGA prototype system.

Introduction to Hardware-Assisted Verification System Platform

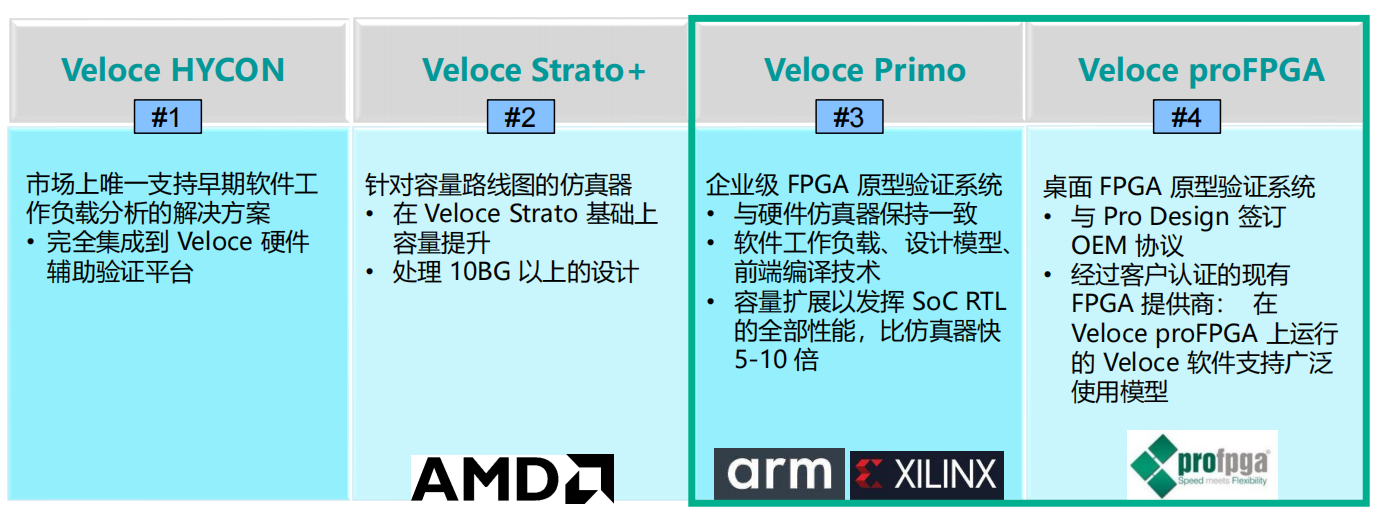

In order to meet the four steps of verification, Siemens EDA recently released the next-generation comprehensive hardware-assisted verification system platform, which is the industry's first complete integrated solution that integrates first-class virtual platform, hardware simulation and FPGA prototype verification technology. It includes Veloce HYCON (HYbrid CONfigurable) for virtual platform/software activation verification, 15 billion gate-level circuit Veloce Strato+, Veloce Primo enterprise-level FPGA prototype verification system and Veloce proFPGA desktop FPGA prototype verification system.

Veloce platform four product families

Li Liji gave a detailed introduction to the four major categories of products on the platform.

Veloce HYCON is the only solution in the industry that supports early software workload analysis and software-based design methods, which is in line with today's shift-left design methodology. This shortens the overall development time and advances the integration of software and hardware, so that architectural problems can be discovered and modified more quickly. "Customers can connect the hardware of their own design directly to the HYCON model, and then they can execute the operating system and perform evaluations. Because the CPU is not developed using RTL, it runs faster and the verification time is greatly shortened," said Li Liji. The benefits of virtual solutions are obvious. As SoC designs are increasingly dependent on software and IP, if they can be confirmed earlier in the subsystem environment, the design, verification, and time to market can be greatly shortened.

Veloce Strato+ realizes the blueprint released when the Veloce Strato platform was launched in 2017. Due to the innovative design and manufacturing of the new proprietary 2.5D chip - Crystal 3+, it achieves higher internal interconnection speed, lower power consumption and smaller area, making the system capacity 1.5 times higher than the previous Veloce Strato. Li Liji emphasized that although the use of fully customized ASIC is more expensive than FPGA, it can achieve complete visibility to meet customers' verification needs.

Li Liji emphasized that AMD, as a cooperative customer of Strato+, highly recognized the performance of Strato+. Alex Star, AMD Enterprise Fellow and Methodology Architect, emphasized, "The high-performance designs we develop require the use of scalable, reliable, and innovative simulation solutions. We are very happy to work with Siemens to first deploy large-capacity Veloce Strato+ systems at AMD. In addition, we are also very happy to see that our second-generation and third-generation AMD EPYC processors can be used in Veloce Strato and Veloce Strato+ platforms. The high performance of these two processor series can bring higher design productivity to the Veloce ecosystem and customers including AMD."

Siemens EDA divides FPGA prototyping systems into enterprise-level and desktop-level systems. The enterprise-level FPGA prototyping system Veloce Primo provides excellent performance, with capacity that can be expanded to 320 FPGAs, supporting up to 12 billion gate arrays. The Veloce proFPGA desktop series adopts a modular capacity solution and can use high-end FPGAs such as Intel Stratix 10 GX 10M and Virtex UltraScale+ VU19P to meet a variety of capacity expansion requirements from 40 million gates to 800 million gates.

“Growing computing demands across industries mean shorter time to market,” said Tran Nguyen, senior director of design services at Arm. “Siemens’ Veloce Primo enterprise-grade FPGA prototyping solution helps Arm quickly solve design problems and achieve verification goals, enabling our ecosystem to develop high-quality Arm-based SoCs to accelerate innovation.”

Nowadays, in the field of FPGA prototyping, some companies choose to develop their own FPGA prototyping platforms. In response to this, Li Liji said that the difficulty of FPGA prototyping is not in hardware design, but in how to divide a design and layout it into the FPGA prototyping system. This division algorithm determines the performance of the operation.

The charm of platformization

Ling Lin pointed out that many large chip design companies will choose verification systems from different suppliers according to their chip design needs and directions. However, for the Chinese market, there are more small and medium-sized enterprises, so whether in terms of technical factors or business convenience, platform solutions are more suitable for China.

Platformization can minimize the cost of technology migration. For example, Strato and FPGA prototype verification systems are unified and interoperable, using a unified operating system, unified solutions, and a unified RTL front-end compiler. Therefore, customers can easily reuse RTL at different stages, whether migrating from Strato to the FPGA prototype verification system to achieve the next verification link, or finding bugs during the FPGA prototype verification process and then tracing back to Strato for debugging with higher visibility. This flexible design can maximize the reuse of verification materials, environments, and test content, thereby providing the necessary foundation for the implementation of seamless methods.

Li Liji also added that the Veloce hardware platform has many apps that can accelerate traditional EDA software functions as well as DFT acceleration, which is equivalent to one platform that can accomplish various tasks.

Synergies with Siemens

This press conference is the first appearance of Siemens EDA after the name change, so Li Liji and Ling Lin also interpreted the significance behind Mentor's name change to Siemens EDA.

Li Liji said that the digital twin design concept advocated by Siemens is completely consistent with Mentor's simulation product concept. For example, the PAVE360 solution from chip to autonomous driving system relies on the Veloce Strato hardware simulator to test the performance of autonomous driving in a virtual environment.

Ling Lin said that the company's name change is not giving up or terminating, but facing a new and broader platform. Siemens is a more profound, broader and deeper technology company. Take simulation as an example. As chip design increasingly needs to consider performance in the system, it needs to face more cross-domain simulation requirements. Including electronics, electromagnetics, thermodynamics and even mechanics. "After changing our name to Siemens EDA, we can meet the broader R&D needs of existing or potential customers. Some problems can be solved within the chip, and some problems require collaborative cross-domain integration and simulation with other systems. Therefore, Siemens EDA can bring system-level design concepts to customers."

Previous article:Five highlights of the new generation of DDR5 DIMMs and the outlook for next-generation server memory

Next article:Intel Fellow Swan: Reshaping Chip Design from the Outside In

- Popular Resources

- Popular amplifiers

- Vietnam's chip packaging and testing business is growing, and supply-side fragmentation is splitting the market

- The US asked TSMC to restrict the export of high-end chips, and the Ministry of Commerce responded

- ASML predicts that its revenue in 2030 will exceed 457 billion yuan! Gross profit margin 56-60%

- ASML provides update on market opportunities at 2024 Investor Day

- It is reported that memory manufacturers are considering using flux-free bonding for HBM4 to further reduce the gap between layers

- Intel China officially releases 2023-2024 Corporate Social Responsibility Report

- Mouser Electronics and Analog Devices Launch New E-Book

- AMD launches second-generation Versal Premium series: FPGA industry's first to support CXL 3.1 and PCIe Gen 6

- SEMI: Global silicon wafer shipment area increased by 6.8% year-on-year and 5.9% month-on-month in 2024Q3

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

- Parasitic parameter issues of vias in PCB

- [GD32L233C-START Review] 3. DMA issues

- #idlemarket#Selling GigaDevice GD32 E231C-START development board

- Goodbye 2019 ~ Hello 2020 - Looking back at 2019 and planning for 2020

- 【Home Smart Dashboard】Project Submission

- FPGA design ideas and techniques: data interface synchronization

- Together: About the GD32L233 development board unpacking test

- EEWORLD University Hall----Research and development of high-speed motors

- How to choose between different chips in TI's Sub-1GHz product line?

- Why does C6000 need Cache?

5962-9313101M2X

5962-9313101M2X

京公网安备 11010802033920号

京公网安备 11010802033920号