Introduction

--- Biochip is a high-tech technology that emerged with the research and development of the "Human Genome Project" at the end of the 20th century. It is an effective means for people to obtain biological information efficiently and on a large scale. At present, most biochips use fluorescent dyes to mark the sample molecules to be tested. The biochip scanner uses laser to excite the fluorescent dye, and detects a point by imaging the excitation point; combined with the movement of the XY two-dimensional precision scanning stage of the biochip, the entire chip is scanned. The position detection accuracy of the XY two-dimensional scanning stage directly affects the scanning resolution, which is a key parameter of the performance of the biochip scanner. The position detection circuit of the XY two-dimensional scanning stage in the biochip scanner based on the traditional digital circuit has counting errors and false zeroing problems. This article solves this problem with the position detection circuit designed based on FPGA. Replacing the traditional digital circuit with FPGA chips can not only improve the integration and reliability of the system, but also the maximum operating frequency of FPGA has exceeded 200MHz. By programming FPGA with hardware description language, the circuit design is more flexible, leaving more margin for the biochip scanner to further improve the scanning speed and scanning resolution.

1 XY two-dimensional scanning stage position detection principle

diagram 1 2

--- XY two-dimensional scanning stage X-axis and Y-axis position detection elements use open gratings, 50 lines/mm, and after being subdivided by a special subdivision ruler 10, the measurement resolution is 2μm. The open grating directly uses the principle of photoelectric conversion to output three-phase square waves A, B, and Z. The phase difference between the A and B phase square waves is 90° (as shown in Figures 1 and 2). The Z phase is used for reference point positioning, and its logic level is 5V. When the A phase square wave leads the B phase square wave by 90°, it indicates that the displacement direction is in the positive direction, as shown in Figure 1; when the A phase square wave lags the B phase square wave by 90°, it indicates that the displacement direction is in the reverse direction, as shown in Figure 2. For every 2μm displacement of the scanning stage in the X and Y directions, the grating emits a cycle of square waves.

--- Therefore, the position detection of the XY two-dimensional scanning stage must first solve the problem of identifying the direction of the grating signal and identify the displacement direction of the X and Y directions; secondly, in order to ensure that the biochip scanning still has a high scanning quality when the highest scanning resolution is 5μm, the position detection accuracy of the X and Y directions should be higher than 2μm to reduce the positioning error of the scanning stage, so the grating signal must be further subdivided; in addition, it is also necessary to complete the conversion of the grating signal into position data that can be read by the controller. When the displacement direction of the X and Y directions is positive, this position data increases; when the displacement direction of the X and Y directions is negative, this position number decreases, and it is necessary to ensure that the X and Y position data are provided in real time, accurately and reliably, as the basis for the controller (such as a single-chip microcomputer, DSP) to accurately locate the position of the XY two-dimensional scanning stage.

--- The position detection in one direction of the XY two-dimensional scanning platform in the original biochip scanner uses a 4-fold frequency dedicated integrated circuit QA740210 to identify and subdivide the grating signal, and uses four 4-bit binary 74LS193 counters in cascade to achieve 16-bit counting of the subdivided grating signal. The count value (i.e., position data) is output to the controller through two 8-bit 74LS245 buffers. In this way, the position detection circuits in the X and Y directions are as many as 14 chips, which occupy a large amount of PCB space, and the wiring is complicated. The crosstalk between the signals on the board is easy to cause counting errors and false zeroing, affecting the precise positioning of the scanning platform. If only one FPGA is used to implement the position detection circuit, the input is the grating signal, and the output is the position data, which is directly sent to the controller to avoid signal crosstalk between PCB boards, and the counting error and false zeroing can be effectively eliminated.

2 FPGA Design Scheme for Position Detection of XY Two-dimensional Scanning Platform

Figure 3

--- Spartan-II series FPGA (XC2S15-5VQ100) is selected as the position detection circuit of the XY two-dimensional scanning platform, which identifies, subdivides and counts the X and Y grating signals in parallel, and provides an interface with the controller to transmit the X and Y position data to the controller in real time and reliably.

--- The internal module division of FPGA is shown in Figure 3: After the A and B two-phase square wave signals XA and XB from the X-axis grating are identified and subdivided by the X-axis identification and subdivision circuit, two pulse signals XCU and XCD are output. The 16-bit counting module counts the two pulse signals respectively, and subtracts the two count values XUPCNT and XDOWNCNT, and the difference is used as the 16-bit position data XCNT of the X direction. The interface circuit decodes the 3-bit address signal ADDR, clears the X and Y counters respectively through XCLR and YCLR, and selects the X or Y position data to be output to the controller.

--- The same is true for the Y direction. This paper only explains it in the X direction.

2.1 Direction identification subdivision design

--- As shown in Figures 1 and 2, when the grating moves in the forward direction, the level logic of phase A and phase B is expressed as a sequence of "00" → "10" → "11" → "01" → "00"; when the grating moves in the reverse direction, the level logic of phase A and phase B is expressed as a sequence of "00" → "01" → "11" → "10" → "00". Therefore, as long as these two sequences can be distinguished, direction identification can be achieved.

--- An external clock source with a frequency of 10MHz is introduced, and the rising edge of this clock is used to sample the phase A and phase B signals at the same time, as the current XA and XB values, and recorded as a two-dimensional vector AB_new. After AB_new passes through a first-level trigger, it is recorded as AB_old. AB_new and AB_old both change with the changes of the phase A and phase B square wave signals, but AB_old lags behind AB_new by one sampling clock cycle. In this way, AB_old and AB_new can be compared: when AB_old is "00", if AB_new is "10", that is, phase A is 90° ahead of phase B, XCU outputs a negative pulse, and XCD remains at a high level; if AB_new is "01", that is, phase A lags behind phase B by 90°, XCD outputs a negative pulse, and XCU remains at a high level. When the X-axis grating signal changes for one cycle, if phase A exceeds phase B by 90° (the displacement direction is positive), XCU will output four negative pulses, and if phase A lags behind phase B by 90° (the displacement direction is negative), XCD will output four negative pulses, realizing the direction identification and subdivision functions at the same time.

2.2 Reversible counter design

--- Use two 16-bit binary counters to count the two pulse signals XCU and XCD respectively, and then use a 16-bit subtractor to make a difference between the count values of the two counters. The minuend is the count value XUPCNT of XCU, and the subtrahend is the count value XDOWNCNT of XCD. The difference is used as the X-direction position data XCNT. In this way, when XCU has a counting pulse, XCNT will increase, and when XCD has a counting pulse, XCNT will decrease, realizing reversible counting. Combined with the previous direction identification subdivision circuit, the X-direction position data increases when the displacement is in the forward direction and decreases when the displacement is in the reverse direction. The change in position data truly reflects the displacement situation.

2.3 Interface circuit design

--- The interface circuit is the interface for the controller to read the X-direction and Y-direction position data or clear them in real time and reliably. The interface circuit consists of a decoding circuit and an output tri-state buffer. The 16-bit data line CNT of the interface circuit and the controller is used for FPGA to transmit position data to the controller. The 3-bit address line ADDR of the controller is used as the input of the decoding circuit: it can output the X and Y position data respectively, and clear the X and Y counters respectively. The decoding circuit can make the X and Y position data reuse the 16-bit data line, and efficiently use the port resources of the controller; the 3-bit address signal is decoded to generate a clear signal, which can effectively prevent the false clearing caused by interference when only one signal line is used.

3 Design simulation and implementation

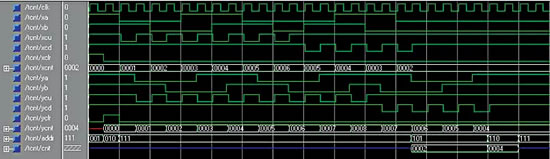

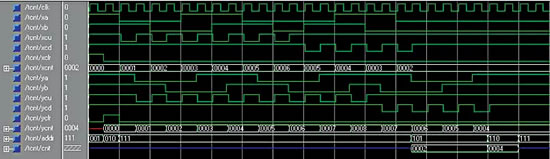

--- On the ISE6.1i development platform, the VHDL language is used to program the subdivision, counting and interface circuits. Figure 4 is the simulation waveform.

Figure 4

--- As can be seen from Figure 4, the X and Y directions can identify, subdivide and count the grating signals in parallel. The following only explains the X direction: the direction identification and subdivision circuit outputs counting pulses with a frequency of 4 times that of XA and XB on XCU and XCD respectively according to the phase difference of the two orthogonal square wave signals XA and XB, thereby realizing direction identification and subdivision; the reversible counter counts XA and XB respectively, and the difference XCNT of the count values increases or decreases with the change of the displacement direction of the X direction; when the address decoding signal ADDR of the controller is "101", the X-direction position data XCNT is output to the 16-bit data line CNT; when ADDR is "110", FPGA outputs the Y-direction position data YCNT to CNT; when the address line ADDR is "001", the X-direction position data XCNT is cleared, and CNT is in a high impedance state; when ADDR is "010", the Y-direction position data YCNT is cleared, CNT behaves in a high-impedance state; when ADDR is any other value, CNT behaves in a high-impedance state, allowing the controller to exchange data with other peripherals. After the code was downloaded to the XC2S15-5VQ100, it was used in a biochip scanner to accurately and reliably implement the position detection function.

4 Conclusion

--- Using FPGA to implement the position detection circuit of the XY two-dimensional scanning stage improves the system's integration and makes position detection fast and reliable. In addition, FPGA has a high operating frequency and flexible design, which can reduce the development time and cost of the biochip scanner to further improve the scanning speed and scanning resolution.

References

1 James R.Armstrong, F.Gail Gray. VHDL Design Representation and Synthesis. Prentice Hall PTR, Inc.2003

2 Xilinx DS001 September 3,2003

Keywords:FPGA

Reference address:Position detection of biochip scanner based on FPGA

--- Biochip is a high-tech technology that emerged with the research and development of the "Human Genome Project" at the end of the 20th century. It is an effective means for people to obtain biological information efficiently and on a large scale. At present, most biochips use fluorescent dyes to mark the sample molecules to be tested. The biochip scanner uses laser to excite the fluorescent dye, and detects a point by imaging the excitation point; combined with the movement of the XY two-dimensional precision scanning stage of the biochip, the entire chip is scanned. The position detection accuracy of the XY two-dimensional scanning stage directly affects the scanning resolution, which is a key parameter of the performance of the biochip scanner. The position detection circuit of the XY two-dimensional scanning stage in the biochip scanner based on the traditional digital circuit has counting errors and false zeroing problems. This article solves this problem with the position detection circuit designed based on FPGA. Replacing the traditional digital circuit with FPGA chips can not only improve the integration and reliability of the system, but also the maximum operating frequency of FPGA has exceeded 200MHz. By programming FPGA with hardware description language, the circuit design is more flexible, leaving more margin for the biochip scanner to further improve the scanning speed and scanning resolution.

1 XY two-dimensional scanning stage position detection principle

diagram 1 2

--- XY two-dimensional scanning stage X-axis and Y-axis position detection elements use open gratings, 50 lines/mm, and after being subdivided by a special subdivision ruler 10, the measurement resolution is 2μm. The open grating directly uses the principle of photoelectric conversion to output three-phase square waves A, B, and Z. The phase difference between the A and B phase square waves is 90° (as shown in Figures 1 and 2). The Z phase is used for reference point positioning, and its logic level is 5V. When the A phase square wave leads the B phase square wave by 90°, it indicates that the displacement direction is in the positive direction, as shown in Figure 1; when the A phase square wave lags the B phase square wave by 90°, it indicates that the displacement direction is in the reverse direction, as shown in Figure 2. For every 2μm displacement of the scanning stage in the X and Y directions, the grating emits a cycle of square waves.

--- Therefore, the position detection of the XY two-dimensional scanning stage must first solve the problem of identifying the direction of the grating signal and identify the displacement direction of the X and Y directions; secondly, in order to ensure that the biochip scanning still has a high scanning quality when the highest scanning resolution is 5μm, the position detection accuracy of the X and Y directions should be higher than 2μm to reduce the positioning error of the scanning stage, so the grating signal must be further subdivided; in addition, it is also necessary to complete the conversion of the grating signal into position data that can be read by the controller. When the displacement direction of the X and Y directions is positive, this position data increases; when the displacement direction of the X and Y directions is negative, this position number decreases, and it is necessary to ensure that the X and Y position data are provided in real time, accurately and reliably, as the basis for the controller (such as a single-chip microcomputer, DSP) to accurately locate the position of the XY two-dimensional scanning stage.

--- The position detection in one direction of the XY two-dimensional scanning platform in the original biochip scanner uses a 4-fold frequency dedicated integrated circuit QA740210 to identify and subdivide the grating signal, and uses four 4-bit binary 74LS193 counters in cascade to achieve 16-bit counting of the subdivided grating signal. The count value (i.e., position data) is output to the controller through two 8-bit 74LS245 buffers. In this way, the position detection circuits in the X and Y directions are as many as 14 chips, which occupy a large amount of PCB space, and the wiring is complicated. The crosstalk between the signals on the board is easy to cause counting errors and false zeroing, affecting the precise positioning of the scanning platform. If only one FPGA is used to implement the position detection circuit, the input is the grating signal, and the output is the position data, which is directly sent to the controller to avoid signal crosstalk between PCB boards, and the counting error and false zeroing can be effectively eliminated.

2 FPGA Design Scheme for Position Detection of XY Two-dimensional Scanning Platform

Figure 3

--- Spartan-II series FPGA (XC2S15-5VQ100) is selected as the position detection circuit of the XY two-dimensional scanning platform, which identifies, subdivides and counts the X and Y grating signals in parallel, and provides an interface with the controller to transmit the X and Y position data to the controller in real time and reliably.

--- The internal module division of FPGA is shown in Figure 3: After the A and B two-phase square wave signals XA and XB from the X-axis grating are identified and subdivided by the X-axis identification and subdivision circuit, two pulse signals XCU and XCD are output. The 16-bit counting module counts the two pulse signals respectively, and subtracts the two count values XUPCNT and XDOWNCNT, and the difference is used as the 16-bit position data XCNT of the X direction. The interface circuit decodes the 3-bit address signal ADDR, clears the X and Y counters respectively through XCLR and YCLR, and selects the X or Y position data to be output to the controller.

--- The same is true for the Y direction. This paper only explains it in the X direction.

2.1 Direction identification subdivision design

--- As shown in Figures 1 and 2, when the grating moves in the forward direction, the level logic of phase A and phase B is expressed as a sequence of "00" → "10" → "11" → "01" → "00"; when the grating moves in the reverse direction, the level logic of phase A and phase B is expressed as a sequence of "00" → "01" → "11" → "10" → "00". Therefore, as long as these two sequences can be distinguished, direction identification can be achieved.

--- An external clock source with a frequency of 10MHz is introduced, and the rising edge of this clock is used to sample the phase A and phase B signals at the same time, as the current XA and XB values, and recorded as a two-dimensional vector AB_new. After AB_new passes through a first-level trigger, it is recorded as AB_old. AB_new and AB_old both change with the changes of the phase A and phase B square wave signals, but AB_old lags behind AB_new by one sampling clock cycle. In this way, AB_old and AB_new can be compared: when AB_old is "00", if AB_new is "10", that is, phase A is 90° ahead of phase B, XCU outputs a negative pulse, and XCD remains at a high level; if AB_new is "01", that is, phase A lags behind phase B by 90°, XCD outputs a negative pulse, and XCU remains at a high level. When the X-axis grating signal changes for one cycle, if phase A exceeds phase B by 90° (the displacement direction is positive), XCU will output four negative pulses, and if phase A lags behind phase B by 90° (the displacement direction is negative), XCD will output four negative pulses, realizing the direction identification and subdivision functions at the same time.

2.2 Reversible counter design

--- Use two 16-bit binary counters to count the two pulse signals XCU and XCD respectively, and then use a 16-bit subtractor to make a difference between the count values of the two counters. The minuend is the count value XUPCNT of XCU, and the subtrahend is the count value XDOWNCNT of XCD. The difference is used as the X-direction position data XCNT. In this way, when XCU has a counting pulse, XCNT will increase, and when XCD has a counting pulse, XCNT will decrease, realizing reversible counting. Combined with the previous direction identification subdivision circuit, the X-direction position data increases when the displacement is in the forward direction and decreases when the displacement is in the reverse direction. The change in position data truly reflects the displacement situation.

2.3 Interface circuit design

--- The interface circuit is the interface for the controller to read the X-direction and Y-direction position data or clear them in real time and reliably. The interface circuit consists of a decoding circuit and an output tri-state buffer. The 16-bit data line CNT of the interface circuit and the controller is used for FPGA to transmit position data to the controller. The 3-bit address line ADDR of the controller is used as the input of the decoding circuit: it can output the X and Y position data respectively, and clear the X and Y counters respectively. The decoding circuit can make the X and Y position data reuse the 16-bit data line, and efficiently use the port resources of the controller; the 3-bit address signal is decoded to generate a clear signal, which can effectively prevent the false clearing caused by interference when only one signal line is used.

3 Design simulation and implementation

--- On the ISE6.1i development platform, the VHDL language is used to program the subdivision, counting and interface circuits. Figure 4 is the simulation waveform.

Figure 4

--- As can be seen from Figure 4, the X and Y directions can identify, subdivide and count the grating signals in parallel. The following only explains the X direction: the direction identification and subdivision circuit outputs counting pulses with a frequency of 4 times that of XA and XB on XCU and XCD respectively according to the phase difference of the two orthogonal square wave signals XA and XB, thereby realizing direction identification and subdivision; the reversible counter counts XA and XB respectively, and the difference XCNT of the count values increases or decreases with the change of the displacement direction of the X direction; when the address decoding signal ADDR of the controller is "101", the X-direction position data XCNT is output to the 16-bit data line CNT; when ADDR is "110", FPGA outputs the Y-direction position data YCNT to CNT; when the address line ADDR is "001", the X-direction position data XCNT is cleared, and CNT is in a high impedance state; when ADDR is "010", the Y-direction position data YCNT is cleared, CNT behaves in a high-impedance state; when ADDR is any other value, CNT behaves in a high-impedance state, allowing the controller to exchange data with other peripherals. After the code was downloaded to the XC2S15-5VQ100, it was used in a biochip scanner to accurately and reliably implement the position detection function.

4 Conclusion

--- Using FPGA to implement the position detection circuit of the XY two-dimensional scanning stage improves the system's integration and makes position detection fast and reliable. In addition, FPGA has a high operating frequency and flexible design, which can reduce the development time and cost of the biochip scanner to further improve the scanning speed and scanning resolution.

References

1 James R.Armstrong, F.Gail Gray. VHDL Design Representation and Synthesis. Prentice Hall PTR, Inc.2003

2 Xilinx DS001 September 3,2003

Previous article:Homemade Logic Detector

Next article:Design of Harmonic Detection Circuit in Active Power Filter

- Popular Resources

- Popular amplifiers

Recommended Content

Latest Test Measurement Articles

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- In what situations are non-contact temperature sensors widely used?

- How non-contact temperature sensors measure internal temperature

MoreSelected Circuit Diagrams

MorePopular Articles

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

MoreDaily News

- Wi-Fi 8 specification is on the way: 2.4/5/6GHz triple-band operation

- Wi-Fi 8 specification is on the way: 2.4/5/6GHz triple-band operation

- Vietnam's chip packaging and testing business is growing, and supply-side fragmentation is splitting the market

- Vietnam's chip packaging and testing business is growing, and supply-side fragmentation is splitting the market

- Three steps to govern hybrid multicloud environments

- Three steps to govern hybrid multicloud environments

- Microchip Accelerates Real-Time Edge AI Deployment with NVIDIA Holoscan Platform

- Microchip Accelerates Real-Time Edge AI Deployment with NVIDIA Holoscan Platform

- Melexis launches ultra-low power automotive contactless micro-power switch chip

- Melexis launches ultra-low power automotive contactless micro-power switch chip

Guess you like

- RK3288 Information

- FFT based on C2000 series DSP

- Occupy the posting position, ESP32---WS2812 16*16 dot matrix drawing points, lines and surfaces

- About the pitfalls of ADXL362 accelerometer

- SimpleLink Wi-Fi Devices

- Efficiency Programming of Single Chip Microcomputer Active Buzzer Driver

- TMS320F28335 project development record 9_28335 interrupt system

- About the problem of setting breakpoints in CCS

- About the ACP in the ARM Cortex-A9 multi-core MPcore

- Internet of Things Project Collection 1: Which one do you want to do?

ALD4701ASBXXXX

ALD4701ASBXXXX

京公网安备 11010802033920号

京公网安备 11010802033920号