Introduction

Aiming at the application requirements of aerospace test systems, a design scheme of a micro digital storage system based on FPGA is proposed. Based on the traditional storage test system, the system uses the programmable logic device FPGA to perform secondary integration of the unit circuit of the traditional storage test system, which greatly reduces the volume of the test system and sharply reduces the power consumption, thereby improving the system's high overload resistance performance and increasing the system's flexibility, versatility and reliability. FPGA not only completes the control storage and most of the related digital logic unit circuits, but also makes the entire storage system simpler and easier to wire. In addition, system FPGA programming is the process of connecting the fuses in the device according to the predetermined function so that it can complete a specific logical function. Once the programming is completed, the FPGA is equivalent to an integrated circuit that can complete a specific function, so there is no need to worry about errors in the program running path, which is essentially different from a single-chip microcomputer.

2 System Hardware Design

2.1 Device Selection

2.1.1 Power Converter TPS70358

In the system, the FPGA operating voltage is 3.3 V and 2.5 V, the USB interface device CY7C68013 operating voltage is 3.3 V, and the Flash operating voltage is 3.3 V. The system needs to convert the voltage to 3.3 V and 2.5 V through the power device TPS70358 to provide power for each device in the system. TPS70358 is a new generation of integrated voltage regulator, a micro-chip system with very low self-consumption, extremely low self-noise and high power ripple suppression performance. Therefore, this device is suitable for voltage conversion of a circuit board or an important device (such as FPGA, DSP).

2.1.2 Field Programmable Gate Array (FPGA) XC2S50

The system uses XC2S50 FPGA to control various interfaces. This device is a Sparran II series high-performance field programmable gate array (FPGA) produced by Xilinx. It has the following features: built-in standard JTAG interface, support for 3.3 V in-system programming (ISP); 3.3 V power supply, integration density of 50,000 available gates; pin-to-pin delay of 7.5 ns, and system frequency of up to 200 MHz. The use of a single-chip FPGA to implement logic control functions simplifies circuit design and improves system reliability. In addition, the XC2S50 system is programmable. Just connect a download cable to the target board and it can be repeatedly programmed, which is convenient for circuit debugging.

2.1.3 USB 2.0 controller CY7C68013

CY7C68013 is a USB 2.0 controller produced by Cypress. The device has the characteristics of fast operation speed, low power consumption and high cost performance. The clock cycle is as high as 40 MHz, and it takes 4 clock cycles to execute one instruction. It has integrated USB interface, I2C bus interface, etc. The actual data transmission speed of the system is designed to be up to 10 MHz.

2.2 Circuit Design Idea

Figure 1 is a block diagram of the system hardware structure. The computer controls the programmable logic device FPGA through the USB interface to implement block erase, page programming, data reading and other operations on the Flash memory.

During the block erase operation, the computer sends instructions to the FPGA through the USB interface. After receiving the instructions, the FPGA performs a block erase operation on the Flash memory and returns the status to the computer; during the page programming operation, the FPGA receives the instructions sent by the computer parallel interface and immediately performs page programming on the Flash memory, first writes the command, then writes the address to be programmed, and then sends the data to the Flash memory; during the data read operation, the FPGA first receives the instructions sent by the computer, and then performs a data read operation on the Flash memory, first writes the command, then writes the address to be read, and then starts to output data and returns the status to the computer parallel interface.

3 System Software Design

3.1 FPGA Read, Write and Erase Operations

on Flash FPGA performs read, write and erase operations on Flash by using the state machine of VHDL language. The state machine controls the timing circuit of Flash, which is simple and easy to operate, and the logical relationship is clear at a glance. XC2S50 receives the erase control command from CY7C68013 and immediately performs the erase operation. According to the timing, first write the automatic block erase setting command 60H, then write 2 row addresses and 1 column address in sequence for addressing, and then write the erase command D0H to start the erase operation. The

read operation is more complicated and requires XC2S50 and CY7C68013 to work together. Here we only give the operation process of the read signal. First write the read setting command 00H. Because one page is read at a time, the address written is 2 row addresses and 3 column addresses. Then write the read command. After waiting for rb to become high, the re signal can be sent to read the data from Flash. The writing process is similar to the reading process, but the writing process is completely controlled by XC2S50. After writing the command and address, the data is written until 2 KB of data is written, and finally the page programming command is input. It should be noted that after writing 2 KB of data, the waiting time for the status signal rb returned by Flash is relatively long, about 140μs. Figure 2 shows the process of page programming.

3.2 CY7C68013 control logic and firmware program design

CY7C68013 mainly completes two parts of work. The first is to realize the control switch command of erase, that is, the host computer sends the erase command through the USB interface. After receiving this command, CY7C68013 will send a low pulse of about 200 ms to notify FPGA to start the erase operation; the second is to cooperate with FPGA to complete the task of reading from Flash to the host computer through the GPIF interface of CY7C68013. The I/O used by CY7C68013 includes the control line USBCTR1, the status line US-BS0, the read signal line USBRD and 8 data lines. [page]

When reading, the microcontroller first sends a reading start command USBCTR1. After receiving the command, the FPGA starts initialization, including writing the reading setting command, address and reading command, waiting for rb to become high, USBS0 to be low, and when the microcontroller detects that USBS0 has become low, it starts to give a series of pulses GPIF (USBRD) to read out 2 KB data in sequence. At the same time, the FPGA sets USBS0 high after waiting for several hundred nanoseconds. After judging that USBS0 has become high, the microcontroller also pulls USBCTR1 high to prepare for the next page reading. The reading timing is shown in Figure 3.

According to the above control logic relationship, write the same program of CY7C68013. CY7C68013 has three available interface modes: port, GPIF master control and slave FI-FO. The "GPIF master control" interface mode uses PORTB and PORTD to form a 16-bit data interface to four FX2 endpoint FIFOs (EP2, EP4, EP6 and EP8). GPIF is directly connected to FIFO as the internal master controller. It has 6 programmable control output signals (CTR0~CTR5) and 6 general ready input signals (RDY0~RDY5). Users can set the output status of the control signal through programming, that is, the device will perform the corresponding operation after receiving the ready signal. The GPIF control code is stored in the waveform descriptor of the device's internal RAM. Based on the system requirements, CY7C68013 is set to FIFO Read mode, so that the Slave FIFO in GPIF can directly establish a connection with the endpoint buffer in USB communication, and data transmission does not require CPU participation. The

firmware program code design mainly designs the corresponding program framework diagram according to the system requirements, and then calls the functions of the same-piece function library (Ezusb.lib) for programming, initializes and re-enumerates the endpoints, and then sets the task in the task processor, and compiles the code in the Keil C51 environment. After the compilation is successful, the same-piece code is downloaded to the USB microcontroller to implement the GPIF multi-byte read operation.

4 System reliability verification

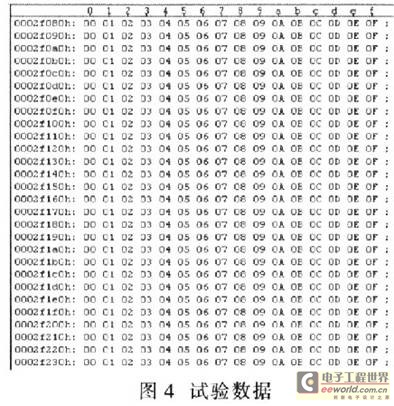

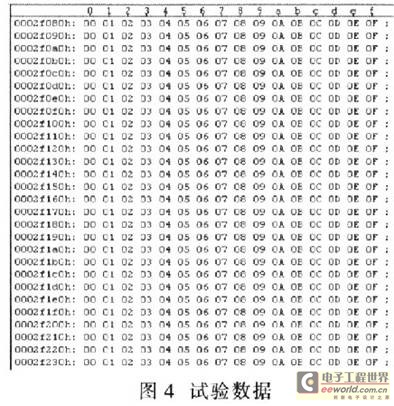

To verify the reliability of the system, 00~0F incrementing data is input cyclically at the data input end, and the data in the Flash is read and written by the host computer. Figure 4 shows the test data. The correctness and reliability of the data storage and readback of the system are verified by the read data.

5 Conclusion

FPGA is used to read, write and erase Flash, and the state machine is used to control the three operations in time-sharing, simplifying the program design. The capacity of Flash is increased from 32 MB to 1 GB by simply modifying the address, which improves the portability, scalability and versatility of the system, facilitates the maintenance of equipment, is conducive to the optimization and improvement of products, and shortens the development cycle. The USB microcontroller is used to establish a communication connection with the PC, which is well compatible with existing equipment. The data reading speed can reach 10 MB/s, and data can be read conveniently and quickly. After multiple verifications, the system works stably and reliably.

Keywords:FPGA

Reference address:Design of Micro Digital Storage System Based on FPGA

Aiming at the application requirements of aerospace test systems, a design scheme of a micro digital storage system based on FPGA is proposed. Based on the traditional storage test system, the system uses the programmable logic device FPGA to perform secondary integration of the unit circuit of the traditional storage test system, which greatly reduces the volume of the test system and sharply reduces the power consumption, thereby improving the system's high overload resistance performance and increasing the system's flexibility, versatility and reliability. FPGA not only completes the control storage and most of the related digital logic unit circuits, but also makes the entire storage system simpler and easier to wire. In addition, system FPGA programming is the process of connecting the fuses in the device according to the predetermined function so that it can complete a specific logical function. Once the programming is completed, the FPGA is equivalent to an integrated circuit that can complete a specific function, so there is no need to worry about errors in the program running path, which is essentially different from a single-chip microcomputer.

2 System Hardware Design

2.1 Device Selection

2.1.1 Power Converter TPS70358

In the system, the FPGA operating voltage is 3.3 V and 2.5 V, the USB interface device CY7C68013 operating voltage is 3.3 V, and the Flash operating voltage is 3.3 V. The system needs to convert the voltage to 3.3 V and 2.5 V through the power device TPS70358 to provide power for each device in the system. TPS70358 is a new generation of integrated voltage regulator, a micro-chip system with very low self-consumption, extremely low self-noise and high power ripple suppression performance. Therefore, this device is suitable for voltage conversion of a circuit board or an important device (such as FPGA, DSP).

2.1.2 Field Programmable Gate Array (FPGA) XC2S50

The system uses XC2S50 FPGA to control various interfaces. This device is a Sparran II series high-performance field programmable gate array (FPGA) produced by Xilinx. It has the following features: built-in standard JTAG interface, support for 3.3 V in-system programming (ISP); 3.3 V power supply, integration density of 50,000 available gates; pin-to-pin delay of 7.5 ns, and system frequency of up to 200 MHz. The use of a single-chip FPGA to implement logic control functions simplifies circuit design and improves system reliability. In addition, the XC2S50 system is programmable. Just connect a download cable to the target board and it can be repeatedly programmed, which is convenient for circuit debugging.

2.1.3 USB 2.0 controller CY7C68013

CY7C68013 is a USB 2.0 controller produced by Cypress. The device has the characteristics of fast operation speed, low power consumption and high cost performance. The clock cycle is as high as 40 MHz, and it takes 4 clock cycles to execute one instruction. It has integrated USB interface, I2C bus interface, etc. The actual data transmission speed of the system is designed to be up to 10 MHz.

2.2 Circuit Design Idea

Figure 1 is a block diagram of the system hardware structure. The computer controls the programmable logic device FPGA through the USB interface to implement block erase, page programming, data reading and other operations on the Flash memory.

During the block erase operation, the computer sends instructions to the FPGA through the USB interface. After receiving the instructions, the FPGA performs a block erase operation on the Flash memory and returns the status to the computer; during the page programming operation, the FPGA receives the instructions sent by the computer parallel interface and immediately performs page programming on the Flash memory, first writes the command, then writes the address to be programmed, and then sends the data to the Flash memory; during the data read operation, the FPGA first receives the instructions sent by the computer, and then performs a data read operation on the Flash memory, first writes the command, then writes the address to be read, and then starts to output data and returns the status to the computer parallel interface.

3 System Software Design

3.1 FPGA Read, Write and Erase Operations

on Flash FPGA performs read, write and erase operations on Flash by using the state machine of VHDL language. The state machine controls the timing circuit of Flash, which is simple and easy to operate, and the logical relationship is clear at a glance. XC2S50 receives the erase control command from CY7C68013 and immediately performs the erase operation. According to the timing, first write the automatic block erase setting command 60H, then write 2 row addresses and 1 column address in sequence for addressing, and then write the erase command D0H to start the erase operation. The

read operation is more complicated and requires XC2S50 and CY7C68013 to work together. Here we only give the operation process of the read signal. First write the read setting command 00H. Because one page is read at a time, the address written is 2 row addresses and 3 column addresses. Then write the read command. After waiting for rb to become high, the re signal can be sent to read the data from Flash. The writing process is similar to the reading process, but the writing process is completely controlled by XC2S50. After writing the command and address, the data is written until 2 KB of data is written, and finally the page programming command is input. It should be noted that after writing 2 KB of data, the waiting time for the status signal rb returned by Flash is relatively long, about 140μs. Figure 2 shows the process of page programming.

3.2 CY7C68013 control logic and firmware program design

CY7C68013 mainly completes two parts of work. The first is to realize the control switch command of erase, that is, the host computer sends the erase command through the USB interface. After receiving this command, CY7C68013 will send a low pulse of about 200 ms to notify FPGA to start the erase operation; the second is to cooperate with FPGA to complete the task of reading from Flash to the host computer through the GPIF interface of CY7C68013. The I/O used by CY7C68013 includes the control line USBCTR1, the status line US-BS0, the read signal line USBRD and 8 data lines. [page]

When reading, the microcontroller first sends a reading start command USBCTR1. After receiving the command, the FPGA starts initialization, including writing the reading setting command, address and reading command, waiting for rb to become high, USBS0 to be low, and when the microcontroller detects that USBS0 has become low, it starts to give a series of pulses GPIF (USBRD) to read out 2 KB data in sequence. At the same time, the FPGA sets USBS0 high after waiting for several hundred nanoseconds. After judging that USBS0 has become high, the microcontroller also pulls USBCTR1 high to prepare for the next page reading. The reading timing is shown in Figure 3.

According to the above control logic relationship, write the same program of CY7C68013. CY7C68013 has three available interface modes: port, GPIF master control and slave FI-FO. The "GPIF master control" interface mode uses PORTB and PORTD to form a 16-bit data interface to four FX2 endpoint FIFOs (EP2, EP4, EP6 and EP8). GPIF is directly connected to FIFO as the internal master controller. It has 6 programmable control output signals (CTR0~CTR5) and 6 general ready input signals (RDY0~RDY5). Users can set the output status of the control signal through programming, that is, the device will perform the corresponding operation after receiving the ready signal. The GPIF control code is stored in the waveform descriptor of the device's internal RAM. Based on the system requirements, CY7C68013 is set to FIFO Read mode, so that the Slave FIFO in GPIF can directly establish a connection with the endpoint buffer in USB communication, and data transmission does not require CPU participation. The

firmware program code design mainly designs the corresponding program framework diagram according to the system requirements, and then calls the functions of the same-piece function library (Ezusb.lib) for programming, initializes and re-enumerates the endpoints, and then sets the task in the task processor, and compiles the code in the Keil C51 environment. After the compilation is successful, the same-piece code is downloaded to the USB microcontroller to implement the GPIF multi-byte read operation.

4 System reliability verification

To verify the reliability of the system, 00~0F incrementing data is input cyclically at the data input end, and the data in the Flash is read and written by the host computer. Figure 4 shows the test data. The correctness and reliability of the data storage and readback of the system are verified by the read data.

5 Conclusion

FPGA is used to read, write and erase Flash, and the state machine is used to control the three operations in time-sharing, simplifying the program design. The capacity of Flash is increased from 32 MB to 1 GB by simply modifying the address, which improves the portability, scalability and versatility of the system, facilitates the maintenance of equipment, is conducive to the optimization and improvement of products, and shortens the development cycle. The USB microcontroller is used to establish a communication connection with the PC, which is well compatible with existing equipment. The data reading speed can reach 10 MB/s, and data can be read conveniently and quickly. After multiple verifications, the system works stably and reliably.

Previous article:Application of CPLD in Cable Rapid Testing Technology

Next article:Reliability Analysis of Pressure Sensor Testing Process

- Popular Resources

- Popular amplifiers

Recommended Content

Latest Test Measurement Articles

- Keysight Technologies Helps Samsung Electronics Successfully Validate FiRa® 2.0 Safe Distance Measurement Test Case

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

MoreSelected Circuit Diagrams

MorePopular Articles

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

MoreDaily News

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

Guess you like

- Another board unboxing! This time it's the GigaDevice GD32307E-START development board

- FPGA Introduction Course 2-Counter

- Introduction to TI battery failure modes and BMS related solutions

- 2008 transcripts - review

- Help with the feedback control loop of the flyback switching power supply

- LPWAN Alternatives for IoT

- Greenhouse automatic spraying system ---- H743temperature sensor

- Hongmeng Development Board Neptune (Part 1) - Unboxing

- Can you help me find out what type of diode this is? Thank you.

- Website controlled Christmas tree

935294081115

935294081115

京公网安备 11010802033920号

京公网安备 11010802033920号