1 Overview

TI's TMS320C6655/57 DSP can provide up to 2.5GHz cumulative DSP, making the platform energy-efficient and easy to use. In addition, it is fully backward compatible with all existing C6000 series, fixed-point and floating-point DSPs. Its KeyStone architecture provides a programmable platform that integrates various subsystems (C66x core, memory subsystem, peripherals and accelerators), and uses some innovative components and technologies to maximize the communication within and between devices, allowing multiple DSP resources to operate effectively and seamlessly.

This architecture has some key components, such as the multi-core navigator, which can efficiently manage data between various components. Teranet is a non-blocking switching structure that enables fast internal data movement. Its multi-core shared memory controller can directly access shared memory and external memory without affecting the performance of the switching structure.

For fixed-point use, the C66x core has the 4× multiple accumulation (MAC) capability of the C64x+ multi-core. In addition, the C66x core integrates floating-point computing capabilities and coarse computing performance per core, which is a good 40GMACS/core and 20GFLOPS/core (@1.25GHz operating frequency). It can perform 8 single-precision floating-point MAC operations (per cycle) and can perform double and mixed precision operations in accordance with the IEEE754 standard. This type of C66x core integrates 90 new instructions (relative to the C64x+ core) for floating-point and vector math processing. These enhancements have greatly improved the performance of DSP cores used in signal processing. This type of C66x core is backward code compatible with TI's previous C6000 fixed and floating-point DSP cores, ensuring software portability and shortening the software development cycle.

The C6655/57 DSP devices integrate a large amount of on-chip memory. In addition to the 32kB L1 program and data cache memory, there is 1024kB of dedicated memory on each core, which can be configured as mapped RAM or cache memory. The device also integrates 1024kB of multi-core shared memory, which can be used as shared L2 SRAM and/or shared L3 SRAM. All L2 memories have error detection and error correction capabilities. To facilitate fast access to external memory, the device also includes a 32-bit DDR-3 external memory interface (EMIF) that runs at 1333MHz and has ECC memory support.

The series supports a variety of high-speed standard interfaces, including RapidIOver2, second-generation PCI Express and Gigabit Ethernet. It also includes I2C, UART, multi-channel buffered serial port (McBSP), universal parallel port, a 16-bit asynchronous EMIF, and general CMOS IO. The device also uses a 40Gbaud full-duplex interface called Hyperlink for high-throughput, low-latency communication (between devices or FPGA).

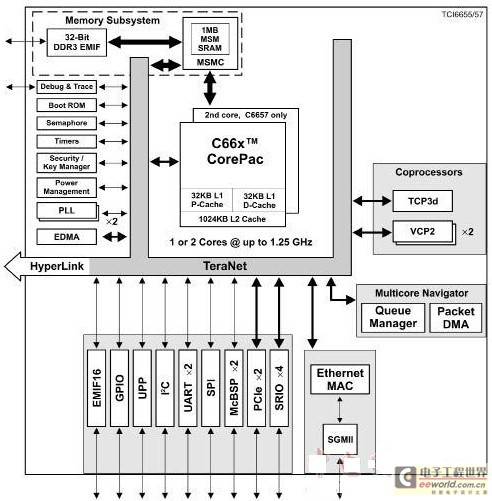

2 TMS320C6655/57 System Block Diagram

The C6655/57 devices have a complete set of development tools, including: an enhanced C compiler, an assembly optimizer (to simplify programming and scheduling) and a WindowsR debugger interface for monitoring source code execution.

1

Figure 1 TMS320C6655/57 block diagram

3 Main features of TMS320C6655/57

• One (C6655) or two (C6657) TMS320C66x DSP core subsystems (CorePacs), each core subsystem

- 850MHz (C6657), C66x fixed/floating point CPU cores at 1.0GHz or 1.25GHz 40GMAC/core for fixed point (1.25GHz) 20GFLOP/core for floating point (1.25GHz)

-Memory 32kB L1P per core 32kB L1D per core 1024kB local L2 per core

• Multicore Shared Memory Controller (MSMC)

- 1024kB MSM SRAM memory (shared by two DSP C66x CorePacs for C6657)

-Memory Protection Unit for MSM SRAM and DDR3_EMIF

• Multi-core Navigator

- 8192 multi-purpose hardware queue and queue manager

-Packet-based DMA for zero-overhead transfers

• Hardware accelerator

- Two Viterbi coprocessors

- A Turbo coprocessor decoder

• Peripherals

- Four-channel SRIO2.1 1.24/2.5/3.125/5Gbaud operation per channel supports direct I/O, information delivery supports four 1×, two 2×, one 4×, and two 1× + one 2× link configurations

- PCIe Gen2 single port supports 1 or 2 lanes up to 5Gbaud (per channel)

-Hyperlink supports connecting to other KeyStone architecture devices, providing scalability resources and supporting up to 40Gbaud

- Gigabit Ethernet (GbE) subsystem One SGMII port supports 10/100/1000Mbps operation

- 32-bit DDR3 interface DDR3-13338GB addressable memory space

-16-bit EMIF

- Universal parallel port 8-bit dual channel or 16-bit each supports SDR and DDR transfer

- Two UART interfaces

- Two Multichannel Buffered Serial Ports (McBSP)

- I2C interface

- 32 GPIO pins

- SPI interface

-Signal light module

- 8 64-bit timers

- Two on-chip phase-locked loops

- SoC security support

• Commercial temperature 0℃~85℃

• Extended temperature 40℃~100℃

• Extended low temperature 55℃~100℃

4 Evaluation Board Introduction

The C6657 Lite EVM is a high-performance, low-cost, stand-alone development platform that enables users to evaluate and develop products using the Texas Instruments TMS320C6657 digital signal processor (DSP). The evaluation module (EVM) can also be used as a hardware reference design platform for the TMS320C6657 DSP. The EVMs are in the form factor of a PICMG AMC.0 R2.0 AdvancedMC module. The TMDSEVM6657LE comes with an integrated, high-speed, XDS560V2 mezzanine simulator with system trace capability. Schematics, code examples, and application notes are also included to facilitate development and reduce time to market.

2

Figure 2 Block diagram of the evaluation board TMDXEVM6657L

5 Evaluation Board Main Features

• Texas Instruments' fixed-point DSP TMS320C6657

•512MB DDR3 memory (supports up to 1024Mbytes)

• 128MB NAND flash memory

• 16MB NOR flash memory

• One Gigabit Ethernet port, supporting

10/100/1000Mbps data rate -- switched between RJ-45 connector and AMC lookup

• 170-pin B+ style AMC connector

• Hyperlink high performance connector

Reference Solution of 1.25GHz DSP Based on TMS320C6657

TMS320C6657|DSP|Digital Signal Processor|Programmable Platform

China Power Grid

Introduction: TI's TMS320C6655/57 is a fixed-point/floating-point digital signal processor (DSP) based on the KeyStone multi-core architecture with a core speed of up to 1.25GHz. It integrates various subsystems including the C66x core, memory subsystem, peripherals and accelerators, and is suitable for high-performance, low-power programmable applications such as mission-critical, test and automation, medical imaging, and infrastructure equipment.

1 Overview

TI's TMS320C6655/57 DSP can provide up to 2.5GHz cumulative DSP, making the platform energy-efficient and easy to use. In addition, it is fully backward compatible with all existing C6000 series, fixed-point and floating-point DSPs. Its KeyStone architecture provides a programmable platform that integrates various subsystems (C66x core, memory subsystem, peripherals and accelerators), and uses some innovative components and technologies to maximize the communication within and between devices, allowing multiple DSP resources to operate effectively and seamlessly.

This architecture has some key components, such as the multi-core navigator, which can efficiently manage data between various components. Teranet is a non-blocking switching structure that enables fast internal data movement. Its multi-core shared memory controller can directly access shared memory and external memory without affecting the performance of the switching structure.

For fixed-point use, the C66x core has the 4× multiple accumulation (MAC) capability of the C64x+ multi-core. In addition, the C66x core integrates floating-point computing capabilities and coarse computing performance per core, which is a good 40GMACS/core and 20GFLOPS/core (@1.25GHz operating frequency). It can perform 8 single-precision floating-point MAC operations (per cycle) and can perform double and mixed precision operations in accordance with the IEEE754 standard. This type of C66x core integrates 90 new instructions (relative to the C64x+ core) for floating-point and vector math processing. These enhancements have greatly improved the performance of DSP cores used in signal processing. This type of C66x core is backward code compatible with TI's previous C6000 fixed and floating-point DSP cores, ensuring software portability and shortening the software development cycle.

The C6655/57 DSP devices integrate a large amount of on-chip memory. In addition to the 32kB L1 program and data cache memory, there is 1024kB of dedicated memory on each core, which can be configured as mapped RAM or cache memory. The device also integrates 1024kB of multi-core shared memory, which can be used as shared L2 SRAM and/or shared L3 SRAM. All L2 memories have error detection and error correction capabilities. To facilitate fast access to external memory, the device also includes a 32-bit DDR-3 external memory interface (EMIF) that runs at 1333MHz and has ECC memory support.

The series supports a variety of high-speed standard interfaces, including RapidIOver2, second-generation PCI Express and Gigabit Ethernet. It also includes I2C, UART, multi-channel buffered serial port (McBSP), universal parallel port, a 16-bit asynchronous EMIF, and general CMOS IO. The device also uses a 40Gbaud full-duplex interface called Hyperlink for high-throughput, low-latency communication (between devices or FPGA).

2 TMS320C6655/57 System Block Diagram

The C6655/57 devices have a complete set of development tools, including: an enhanced C compiler, an assembly optimizer (to simplify programming and scheduling) and a WindowsR debugger interface for monitoring source code execution.

Figure 1 TMS320C6655/57 block diagram

3 Main features of TMS320C6655/57

• One (C6655) or two (C6657) TMS320C66x DSP core subsystems (CorePacs), each core subsystem

- 850MHz (C6657), C66x fixed/floating point CPU cores at 1.0GHz or 1.25GHz 40GMAC/core for fixed point (1.25GHz) 20GFLOP/core for floating point (1.25GHz)

-Memory 32kB L1P per core 32kB L1D per core 1024kB local L2 per core

• Multicore Shared Memory Controller (MSMC)

- 1024kB MSM SRAM memory (shared by two DSP C66x CorePacs for C6657)

-Memory Protection Unit for MSM SRAM and DDR3_EMIF

• Multi-core Navigator

- 8192 multi-purpose hardware queue and queue manager

-Packet-based DMA for zero-overhead transfers

• Hardware accelerator

- Two Viterbi coprocessors

- A Turbo coprocessor decoder

• Peripherals

- Four-channel SRIO2.1 1.24/2.5/3.125/5Gbaud operation per channel supports direct I/O, information delivery supports four 1×, two 2×, one 4×, and two 1× + one 2× link configurations

- PCIe Gen2 single port supports 1 or 2 lanes up to 5Gbaud (per channel)

-Hyperlink supports connecting to other KeyStone architecture devices, providing scalability resources and supporting up to 40Gbaud

- Gigabit Ethernet (GbE) subsystem One SGMII port supports 10/100/1000Mbps operation

- 32-bit DDR3 interface DDR3-13338GB addressable memory space

-16-bit EMIF

- Universal parallel port 8-bit dual channel or 16-bit each supports SDR and DDR transfer

- Two UART interfaces

- Two Multichannel Buffered Serial Ports (McBSP)

- I2C interface

- 32 GPIO pins

- SPI interface

-Signal light module

- 8 64-bit timers

- Two on-chip phase-locked loops

- SoC security support

• Commercial temperature 0℃~85℃

• Extended temperature 40℃~100℃

• Extended low temperature 55℃~100℃

4 Evaluation Board Introduction

The C6657 Lite EVM is a high-performance, low-cost, stand-alone development platform that enables users to evaluate and develop products using the Texas Instruments TMS320C6657 digital signal processor (DSP). The evaluation module (EVM) can also be used as a hardware reference design platform for the TMS320C6657 DSP. The EVMs are in the form factor of a PICMG AMC.0 R2.0 AdvancedMC module. The TMDSEVM6657LE comes with an integrated, high-speed, XDS560V2 mezzanine simulator with system trace capability. Schematics, code examples, and application notes are also included to facilitate development and reduce time to market.

5 Evaluation Board Main Features

• Texas Instruments' fixed-point DSP TMS320C6657

•512MB DDR3 memory (supports up to 1024Mbytes)

• 128MB NAND flash memory

• 16MB NOR flash memory

• One Gigabit Ethernet port, supporting

10/100/1000Mbps data rate -- switched between RJ-45 connector and AMC lookup

• 170-pin B+ style AMC connector

• Hyperlink high performance connector

• 128B I2C EEPROM for booting

• 4 user LED indicators, 4 software controlled

6 LEDs and 3 user DIP switches

• RS232 serial interface via 3-pin header or UART via mini-USB connector

• UPP, timer, SPI, multi-channel buffered serial port, UART interface with 80-pin expansion connector

• USB2.0 interface XDS100 emulation type is used on board

•TI 60-pin JTAG header to support external emulators

• High-speed integrated XDS560V2 mezzanine simulator

• High-speed integrated XDS200 mezzanine simulator

• Intelligent Platform Management Interface (IPMI) for Module Management Controller (MMC)

• Use DC power brick adapter (12V/2.5A) or AMC telecom backplane

•PICMG AMC.0 R2.0 single width, full height

7 AdvancedMC Module

The C6657 Lite EVM contains dual TMS320C6657 fixed-point digital signal processors. The TMS320C6657 device was developed by Texas Instruments (TI) based on the third-generation high-performance, advanced VelociTI very long instruction word (VLIW) architecture, specifically for high-density wired/wireless media gateway infrastructure. This device is an ideal choice for IP border gateways, video transcoding and translation, video servers, intelligent voice, and video recognition applications. This type of C66x device is post-code compatible with previous C6000 DSP platform devices.

• 128B I2C EEPROM for booting

• 4 user LED indicators, 4 software controlled

6 LEDs and 3 user DIP switches

• RS232 serial interface via 3-pin header or UART via mini-USB connector

• UPP, timer, SPI, multi-channel buffered serial port, UART interface with 80-pin expansion connector

• USB2.0 interface XDS100 emulation type is used on board

•TI 60-pin JTAG header to support external emulators

• High-speed integrated XDS560V2 mezzanine simulator

• High-speed integrated XDS200 mezzanine simulator

• Intelligent Platform Management Interface (IPMI) for Module Management Controller (MMC)

• Use DC power brick adapter (12V/2.5A) or AMC telecom backplane

•PICMG AMC.0 R2.0 single width, full height

7 AdvancedMC Module

The C6657 Lite EVM contains dual TMS320C6657 fixed-point digital signal processors. The TMS320C6657 device was developed by Texas Instruments (TI) based on the third-generation high-performance, advanced VelociTI very long instruction word (VLIW) architecture, specifically for high-density wired/wireless media gateway infrastructure. This device is an ideal choice for IP border gateways, video transcoding and translation, video servers, intelligent voice, and video recognition applications. This type of C66x device is post-code compatible with previous C6000 DSP platform devices.

Previous article:The Importance of Architecture When Selecting the Right SoC FPGA

Next article:Implementation of frequency converter based on DSP and using SPWM control technology

- Popular Resources

- Popular amplifiers

- Red Hat announces definitive agreement to acquire Neural Magic

- 5G network speed is faster than 4G, but the perception is poor! Wu Hequan: 6G standard formulation should focus on user needs

- SEMI report: Global silicon wafer shipments increased by 6% in the third quarter of 2024

- OpenAI calls for a "North American Artificial Intelligence Alliance" to compete with China

- OpenAI is rumored to be launching a new intelligent body that can automatically perform tasks for users

- Arm: Focusing on efficient computing platforms, we work together to build a sustainable future

- AMD to cut 4% of its workforce to gain a stronger position in artificial intelligence chips

- NEC receives new supercomputer orders: Intel CPU + AMD accelerator + Nvidia switch

- RW61X: Wi-Fi 6 tri-band device in a secure i.MX RT MCU

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

- CGD and Qorvo to jointly revolutionize motor control solutions

- CGD and Qorvo to jointly revolutionize motor control solutions

- Keysight Technologies FieldFox handheld analyzer with VDI spread spectrum module to achieve millimeter wave analysis function

- Infineon's PASCO2V15 XENSIV PAS CO2 5V Sensor Now Available at Mouser for Accurate CO2 Level Measurement

- Advanced gameplay, Harting takes your PCB board connection to a new level!

- Advanced gameplay, Harting takes your PCB board connection to a new level!

- A new chapter in Great Wall Motors R&D: solid-state battery technology leads the future

- Naxin Micro provides full-scenario GaN driver IC solutions

- Interpreting Huawei’s new solid-state battery patent, will it challenge CATL in 2030?

- Are pure electric/plug-in hybrid vehicles going crazy? A Chinese company has launched the world's first -40℃ dischargeable hybrid battery that is not afraid of cold

- MSP430 Launchpad MSP430g2452 SHT10 Temperature and Humidity Sensor

- Establishment of RF chip/modem chip design team

- F28335 uses external SRAM for program simulation

- CCS Tips: Remove the prompt when burning DSP/BIOS

- Bidirectional thyristor circuit wiring problem

- CMS32F033SS24 wireless charging and security chip

- Selection and application of DCDC module power supply

- Basic Concepts of Wireless Communication

- Download: Qorvo "Basics of Power Management"

- [National Technology N32G457 Review] 4. Serial port 2 DMA interrupt reception and transmission

TC913ACOATR

TC913ACOATR

京公网安备 11010802033920号

京公网安备 11010802033920号