1 Hardware composition of the real-time image processing system

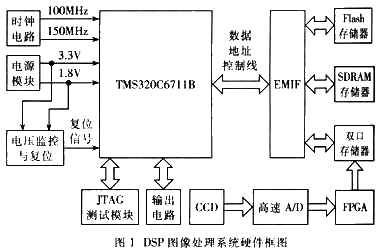

This system uses C6711 as the core, supplemented by field programmable gate array FPGA and high-speed A/D devices to form a real-time high-speed digital image processing system. The system hardware block diagram is shown in Figure 1. The working principle of the image processing system is: the analog image signal collected and output by the CCD is converted into a digital signal through a high-speed A/D. The digital image signal is controlled by the FPGA and the data is converted into a digital signal. Continuously input to dual-port RAM. Whenever a frame of image scanning ends, the FPGA provides an interrupt flag signal, triggering the DSP to move data, and moves a frame of image in the dual-port RAM to the SDRAM through the QDMA of the C6711. After QDMA moves the data, it checks whether the image data is valid. If it is valid, it triggers the DSP to execute the image processing program. Otherwise, it returns to wait for the next interrupt to arrive. The DSP processes the current frame of the image before the next interrupt arrives, and will obtain the attitude angle information. The multi-channel buffered serial port McBSP is output to the RS232 port of the computer and displayed, and then enters the interrupt waiting state, waiting for the interrupt to trigger QDMA again for data movement.

|

|---|

1.1 C6711 Digital Signal Processor

C6711 is a high-speed floating-point DSP chip from TI Company, with a main frequency of 150MHz and a peak computing power of up to 900MFLOSP. C6711 is composed of three parts: CPU core, on-chip peripherals and memory. The processing unit adopts high-speed Performance, advanced VelociTI structure, 8 functional units per clock cycle can work in parallel, C6711 has the characteristics particularly suitable for real-time image processing:

(1) Advanced VelociTI extraordinary instruction word C67XDSP core;

(2) Hardware supports IEEE standard single Precision and double-precision floating point instructions;

(3) 32-bit external memory interface (EMIF), providing seamless interface with synchronous and asynchronous memory;

(4) Two-level cache structure, including: 32Kbit program cache, 32Kbit data cache, two Level cache 512Kbit;

(5) Enhanced DMA controller, a total of 16 independent channels.

1.2 A/D conversion

The analog image signal output by the CCD is converted into a 10-bit digital image signal through high-speed A/D, and is stored in a dual-port SAM memory under the control of the FPGA for DSP processing.

1.3 Power module and monitoring reset circuit

C6000 series DSP requires two voltages, namely the CPU core voltage and the peripheral I/O interface voltage. C6711 requires two voltages, 3.3V and 1.8V, and requires the two power supplies to meet a certain power-on sequence. This system adopts the method of powering up both at the same time. According to the power consumption requirements of the system, the chips TPS54316 and TPS54314 are respectively used to directly generate two voltages of 3.3V and 1.8V. It can provide a maximum supply current of 3A. The power monitoring and reset circuit adopts Implemented by TI's TPS3307-33, it can monitor three independent voltages 3.3V/5V/1.8V at the same time, and when one of the three monitored voltages is lower than its threshold value, it can ensure that a valid RESET signal is output. , to reset the DSP. When their values are higher than the threshold value, the RESET signal becomes high level.

1.4 Clock module and JTAG interface

The 25MHz clock signal is multiplied by ICS501 to generate 150MHz and 100MHz clock signals. After being output by the tri-state gate bus buffer 74LVTH125, the CPU working clock and the working clock required for the synchronization interface are obtained. The 7 clock signals of C6711 JTAG simulation pins TRST, TMS, TDI, TDO, TCK, EMU1 and EMU0 are connected to a 14-pin double-row plug and can be connected to the emulator for system debugging and program downloading.

1.5 External memory design

C6711 must access external memory through EMIF. EMIF not only has a high data throughput rate, but also has strong interface capabilities and can directly interface with all types of current memories. The design uses three types of memories: Flash ROM, dual-port RAM and synchronous dynamic memory SDRAM, Flash ROM is a memory that can be erased on site and can retain data after power failure. It is used to solidify programs and save data that needs to be saved after power failure. Dual-port RAM is used to store one frame of image data; SDRAM runs fast and is used to store real-time data. To run programs and temporary data, the Flash ROM of this system uses SST39V040 and is configured in the CE1 space. The dual-port RAM uses IDT70V28 and is configured in the CE2 space. HY57V563220 is selected as the SDRAM and is configured in the CE0 space. This configuration matches the boot method.

1.6 The output circuit

system obtains satellite attitude angle information after processing by C6711 based on the input image. The attitude angle information is output by C6711 to the RS-232 port of the PC. Since the amount of communication information is small, C6711 can be used The multi-channel buffered serial port McBSP is used to implement asynchronous data transmission format without expanding other hardware. When sending, the sending conversion subroutine expands each data bit into a 16-bit UART word, and converts these converted The data block is put into the send buffer, and the start and end bits are added at the appropriate places (as shown in Figure 2). Then EDMA passes the data from the send buffer to McBSP, and the McBSP frame synchronization generator is responsible for continuous shifting out When receiving these data [4], EDMA reads the expanded data from McBSP, writes the data into the receiving buffer, and then calls the compression subroutine to convert the data into the original byte form. The advantages of this method The hardware interface is simple, just add a level conversion circuit between CMOS level and RS232 level.

|

|---|

2. Implementation of image processing algorithm.

The design of the center positioning image processing algorithm is based on the input image format of 320×240 pixels and 1024 gray levels/pixel. It includes filtering, judging whether the horizon circle enters the field of view, edge detection and precise determination. Several parts in the center.

2.1 The filter

detector may have less than 1% bad cells, whose gray value is mainly 0 or 1023, and the range of bad cells is less than 3×3. The existence of bad cells may bring errors to edge detection. In addition, the collected The signal-to-noise ratio of the image data is low, so two-dimensional median filtering is used [5]. The method is: for a frame of image, use the method from top to bottom and from left to right to move the 3×3 window. At each position, 9 image pixels will appear in the window. For these 9 pixels Sort the grayscale values, use the quick sort method to find the pixel value in the middle, and assign this value to the center pixel of the 3×3 window. This method can effectively filter out bursts in areas no larger than 2×2. interference, thereby improving algorithm accuracy.

2.2 Determine whether the horizon circle has entered the field of view.

When the satellite initially enters the orbit, the earth may not be detected in the initial state of the horizon. At this time, the search program needs to be started to control the deflection of the satellite to search for the earth. Therefore, a progressive scanning search method must be used on the obtained horizon image to determine whether the earth enters the field of view.

2.3 Edge detection Edge

extraction is to first detect the discontinuity of the local characteristics of the image, and then connect these discontinuous edge pixels into a complete boundary. The characteristics of the edge are that the pixels along the edge change gently, and the direction perpendicular to the edge The pixels change drastically. In this sense, the edge extraction algorithm is a mathematical operator that detects edge pixels that conform to edge characteristics.

Due to the unevenness of the earth's radiation, the horizon height is related to the horizon detection method used. The difference lies in the corresponding different horizon detection methods. The specific horizon height changes with the earth's radiation. This article uses the proportional threshold method to detect the horizon circle. The specific algorithm is as follows: starting from the rough center of the earth, taking 720 rays at intervals of 0.5 degrees. Considering that we only need to scan the Earth's radiation transition zone, the scanning starting point of each ray is 100 units from the rough geocenter, and sampling is performed at intervals of one unit. Since the coordinates of the sampling points are not integers, bilinear interpolation is used Obtain the grayscale value of the sampling point, judge the sampling points in turn, record the maximum grayscale value, and judge whether the grayscale value is less than half of the maximum value. When the condition is established, the scan stops, and the algorithm grayscale value is 50% of the maximum value. The corresponding coordinates are the horizon coordinates. After scanning 720 rays, all horizon points form a horizon circle. This algorithm performs bilinear interpolation on points close to the transition zone, which improves program execution efficiency. The detected horizon coordinates are floating point numbers, which improves the accuracy of horizon determination and helps reduce the error in measuring the geocenter.

2.4 Accurate center

determination Accurate center determination is the most critical part of the algorithm. The quality of the method directly affects the accuracy of the geocenter. Generally, there are Hall transform method, area integral and three-point mean method, etc. The area integral method is used for accurate positioning. According to According to calculus theory, for a closed area D, its center of gravity coordinates can be obtained by the following formula:

|

|---|

In the formula, x and y represent the coordinates of the unit point, ρ (x, y) represents the density of the unit point, and D represents the entire area.

When ρ (x, y) = 1, the center of gravity and the centroid of the region coincide, and S represents the area of the region. In order to use a computer to calculate the center position of the region, the above formula must be discretized. The discretized formula is:

|

|---|

In the formula, R(θ) represents the amplitude change rule corresponding to the range of θ i ~ θ i+1 .

3 Experimental results

The image data captured by the CCD are sent to the system for processing. After each frame of image is processed, an attitude angle information will be output from the serial port. Table 1 shows the processing results of the four frames of images. It can be seen from Table 1 that the accuracy of the algorithm is better than the index requirement of 0.1, and the algorithm processing time is about 0.49 seconds, which meets the real-time requirement of processing one frame per second.

|

|---|

The real-time image processing system composed of high-performance digital signal processor TMS320C6711B and FPGA realizes image acquisition, real-time data processing and output. The JTAG interface is used for online debugging of the system, making the system highly upgradable and scalable. The use of DSP processors enhances the system's processing capabilities, increases the system's processing speed, and ensures the real-time requirements of the work. The use of SMT devices not only reduces the size of the PCB board, but also increases the reliability of the system. Practice has proven that the center positioning algorithm greatly improves the measurement accuracy of the horizon by filtering the original image, determining whether the target enters the field of view, edge detection and precise centering.

Previous article:Sodar signal acquisition system based on ADSP-TS201S

Next article:Implementation of digital signal processor based on ADSP-Ts101

Recommended ReadingLatest update time:2024-11-16 16:34

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- [Xianji HPM6750 Review 10] Drawing a multi-function expansion board and verification

- About the distance of infrared obstacle avoidance circuit

- Repost - Tesla battery violent disassembly video

- Relationship between transformer and inductor

- How to port uCOS-II to LPC17XX

- X-NUCLEO-IKS01A3 sensor driver transplantation based on NUCLEO-L011K4

- Standard EIA RS-198

- TMS320C6678 power-on configuration and FPGA reset DSP

- IEC 61000-4-5 Phases of three-phase power supply systems

- [Chuanglong TLA40i-EVM development board] +04.USB-Camera test-abnormal (zmj)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号