Abstract:

This paper analyzes the data encoding and transmission mechanism of the infrared remote control system, and designs the hardware circuit of the infrared receiving module based on FPGA using VerilogHDL language. The simulation test is carried out in VCS and VirSim simulation tools; the synthesis, adaptation and FPGA device download test are carried out using Xilinx ISE 10.1 software. The results show that the circuit achieves the purpose of data reception and display, and complies with the infrared remote control data transmission protocol.

Keywords: infrared communication protocol; Verilog; FPGA

Infrared remote control technology has been widely used in daily household appliances. Its advantages of convenient use, low power consumption and strong anti-interference ability are increasingly valued in intelligent instrument systems. Various home appliance infrared remote control systems on the market are mature in technology and low in cost, but they are all for their respective remote control objects (color TV, refrigerator, air conditioner, etc.) and cannot be directly used for intelligent instruments. This paper discusses how to learn from the principles of home appliance infrared remote control systems and design decoding circuits to enable intelligent instruments to have remote control functions. This module is based on the HS622 1 chip used in the remote control. The infrared receiver head model is IRM3638, and the output is the IR pin. This module decodes the IR output signal, extracts the valid data in the infrared transmission packet, and then outputs 8-bit data and 8-bit remote control user code (address code) in parallel for other modules to call.

1 Design principle of infrared receiving control module

The signal transmitted by the remote control consists of a string of binary codes of 0 and 1. Different chips have different encodings for 0 and 1, usually Manchester encoding and pulse width encoding. HS6221's 0 and 1 are encoded using PWM method, that is, pulse width modulation. The 0 code is composed of 0.56ms low level and 0.565ms high level, and the pulse width is 1.125ms. The 1 code is composed of 0.56ms low level and 1.69ms high level, and the pulse width is 2.25ms. When writing the decoding program, 0 or 1 can be obtained by judging the width of the pulse. The data format of HS6221 and similar chips includes boot code (start code), user code (address code), user inverse code (address inverse code), data code, data inverse code, and the total encoding is 32 bits. The data inverse code is the encoding after the data code is inverted. The principle of user inverse code is the same and can be used for data error correction. The specific format is shown in Figure 1.

When the button of the remote control is pressed, the remote control will send out a string of binary codes as shown in Figure 1, which is called a frame of data. According to the functions of each part, they can be divided into 5 parts, namely, the guide code, user code, user inverse code, data code, and data inverse code. When the remote control transmits the code, the low bit is in front and the high bit is in the back. The infrared receiving head will reverse the high and low levels, so the actual level coming out of the IR end is the inverse of the waveform in the above format diagram, that is, the IR is high level in the stop state, and then enters the ready state after receiving a low level of about 9ms. From the analysis of the figure, it can be obtained that the high level of the guide code is 9ms and the low level is 4.5ms. When this code is received, it indicates the beginning of a frame of data, and the FPGA can prepare to receive the following data. The user code (address code) consists of 8 bits of binary, with a total of 256 types. The user inverse code (address inverse code) in the figure is mainly to enhance the reliability of the remote control. Different devices can have different user codes (address codes). Therefore, remote controls with the same encoding will not interfere with each other as long as the user codes (address codes) are set differently. In the same remote control, the address codes sent by all buttons are the same. The data code is 8 bits and can encode 256 states, representing the actual key pressed. The data inverse code is the inverse of each bit of the data code. By comparing the data code with the data inverse code, it can be determined whether the received data is correct. If the relationship between the data code and the data inverse code does not satisfy the opposite relationship, the remote control reception is incorrect and the data should be discarded. On the same remote control, the data codes of all buttons are different.

2 HDL design of infrared receiving control module

2.1 Introduction to the function of infrared receiving control module

The infrared receiving control module is based on the HS6221 chip used inside the remote control. In terms of infrared receiving control, it has strong anti-interference ability and flexible use. The functions of the infrared receiving control module include eliminating clock delay, frequency synthesis, clock phase adjustment and other system requirements. The main advantages of the infrared receiving control module are the following four points:

(1) Realize the infrared data decoding function, extract the valid content in the data packet and output it in parallel;

(2) Because the PWM protocol is used in the infrared transceiver protocol, the anti-interference ability of the data is further enhanced;

(3) The reception of transmitters with different addresses can be realized by changing the address parameters;

(4) Compare the data in the data packet with the data inverse code in the data packet to ensure that there is no error in the reception process.

For the infrared receiving control module, its key parameters are the start code, the high and low level pulse widths of data 1 and data 0, and the local address.

2.2 Composition of the infrared receiving control module

The infrared receiving control module consists of two parts, as shown in Figure 2. It mainly consists of a clock divider and an infrared receiving control module. The [15:0] Data in the figure consists of 8-bit data and 8-bit address.

2.3 Description of the components of the infrared receiving control module

Clock divider: It mainly divides the system clock (50MHz) into a 0.01MHz clock to drive the infrared receiving control module to work normally. The division period of the PERIOD clock division module, when it is 15'd2500, the division obtains the irda_clk clock signal with a period of 0.1ms; when 15'd2 is taken during simulation, it is to shorten the simulation period and reduce the workload, and generate an irda_clk clock signal with a period of 80ns [2,3].

Note: Only one value can be taken at a time, use 15'd2 for simulation, and use 15'd2500 when downloading to FPGA. Data processing module: This module is the core part of the infrared receiving control module and is mainly composed of a state machine (FSM), as shown in Figure 3.

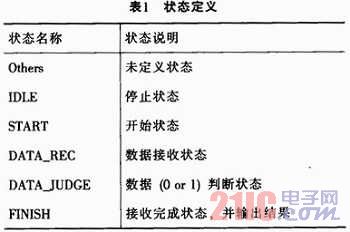

The description of each state of FSM is listed in Table 1.

3 Circuit simulation, FPGA implementation and application test

Write the test vector file, perform functional simulation in VCS and VirSim simulation tools, and it is fully in line with the design requirements after verification. The simulation result is shown in Figure 4. The implementation platform of this design uses Xilinx's SPARTANIII OFP package

XC3S400-4PQ208C

, with a total logic gate of 400k gates. After synthesis, adaptation, simulation, layout and routing, it only occupies relatively few device resources. After the entire system is downloaded to the FPGA, it can work normally at a clock frequency of 50MHz. Under the remote control of the RM-139C super version universal TV remote control, press different buttons, and

the LED

seven-segment four-digit digital tube will display different button remote control codes after decoding.

4 Conclusion

Designing digital systems with HDL and programmable logic devices (FPGA/CPLD) has incomparable advantages over traditional methods, and it has become the most effective means of large-scale integrated circuit design. This paper uses VerilogHDL to design the infrared remote control signal receiving module circuit. For simplicity, this design only decodes the data part of the remote control transmission without losing generality. The design scheme of the infrared remote control signal receiving module based on FPGA proposed in this paper has been verified by circuit simulation, FPGA implementation and application testing. The module fully meets the requirements of the infrared remote control communication protocol.

Previous article:FPGA high-speed data acquisition system based on USB communication

Next article:Design of Linear Array CCD Driver Based on FPGA

Recommended ReadingLatest update time:2024-11-16 23:44

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Op amp positive and negative power supply problem

- When using FIFO to send interrupt, how to configure FIFO depth in DSP SCI?

- Let's discuss: How to debug the appropriate parameters of this RC

- Simple MicroPython IoT Smart Home (ESP8266)

- Ultrasonic standing wave axial suspension mobile device word supplementary materials

- With the explosion of 5G, the future development of Wi-Fi is promising

- Questions about the two array forms of LSM6DSO FSM gesture recognition?

- What are the advantages and disadvantages of complementary push-pull H-bridge (2 NMOS + 2 PMOS) and totem pole H-bridge (4 NMOS), and their applications...

- The problem of turning frequency in LC filter circuit design

- Live broadcast at 10 am today [The rapid growth of Renesas RA MCU family members helps build safe and stable industrial control systems]

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号