2 Working Principle and Hardware Interface of AMBE-1000

2.1 Basic Workflow

Simply put, the working process of AMBE-1000 is shown in Figure 1. AMBE-1000 can be seen as consisting of two separate encoders and decoders. The encoder receives an 8kHz voice data sampling stream (such as 16-bit linear, 8-bit A-law or 8-bit U-law) and outputs a channel data stream at a desired baud rate. Conversely, the decoder receives a channel data stream and synthesizes a voice data stream. The interface timing of the encoder and decoder of AMBE-1000 is completely asynchronous.

2.2 Channel Interface

The channel interface is used to describe the compressed bit stream output from the encoder and the compressed bit stream input to the decoder. The interface can also output status information, for example, it can detect whether there is a dual-tone multi-frequency (DTMF) voice signal input. In addition, the interface performs more complex control operations on the encoder/decoder (usually during initialization). These control functions include the selection of voice and error correction code speed, and the equipment of A/DD/A chips. In most voice transmission systems, the actual encoded bit stream is extracted from the channel in a certain format and combined with system information to form a system transmission data stream, which is sent through the transmission channel; it is extracted at the receiving end and formed into a data stream in the format required by AMBE-1000 through the decoder.

AMBE-1000 has multiple working modes: parallel and serial, framed and non-framed formats, active and passive. Among them, the parallel passive frame mode is the most flexible and practical working mode. The corresponding working mode can be selected by connecting the pull-up resistor and the dip switch to the corresponding interface selection pin. By adopting the above method, the voice rate and error correction code rate can be freely selected between 2400~9600b/s and 50~4750b/s through the selection switch. In the serial active mode, the working clock of AMBE-1000 is 27MHz, and the clock of CHS_O_CLK is 4.5MHz (27MHz/6), that is, 1 bit of data needs to be read within 0.22μs. Even if the microcontroller works at 24MHz, it cannot read the data, so the passive mode must be adopted, so that the clock of CHS_O_CLK can be set by itself, but the clock also needs to meet the requirement of reading 34 bytes of data (i.e. 1 frame of data) within 20ms; at the same time, the parallel port occupies more interface resources, so the serial passive frame mode is adopted, and its hardware connection is shown in Figure 2.

2.3 Data Format

The data of AMBE-1000 is in frame format, and each frame consists of 17 words. The encoder outputs 17 words every 20ms, and the decoder receives 17 words. The first 5 words of each frame consist of frame flag (Header), identification flag (ID), status (output) or control (input) information, and the remaining 12 words constitute the encoded/decoded data. These 12 words, totaling 192 bits, are the maximum data rate of AMBE-1000 working in 9600b/s mode (192b/frame×50frame/s=9600b/s). When the encoding/decoding data rate is lower than 9600b/s, the insufficient bits are filled with 0. It should be noted that no matter what rate the AMBE-1000 works at, all 272 bits (17 words×16b=272b) of frame data (including any unused trailing zeros) must be output from the encoder or input to the decoder. The frameless format can only be used in serial mode.

2.4 AMBE-1000 and TLC32044 interface circuit

AMBE-1000 requires the voice data of A/D and D/A to be input and output in serial mode. The key to this interface circuit is the frame synchronization of the voice data. Its hardware interface circuit is shown in Figure 3. Among them, 5.184MHz is used as the working clock of TLC32044, and also as the trigger pulse of the D flip-flop. The shift pulse (SHIFT CLK) generated by TLC32044 is used to realize the synchronous transmission of bits. By setting C_SEL0-2 to 010, the TLC32044 chip is selected.

2.5 Clock and Reset

The working clock of AMBE-1000 is 26~30MHz. It has three input modes: direct input from TTL clock source, direct input from CMOS clock source or oscillator, and input using crystal oscillator circuit. In this system, the clock is input using crystal oscillator circuit. The effective reset signal is low level and must last for more than 6 clock cycles.

3 Peripheral interface circuit

3.1 Working Principle of TLC32044

The digital processing of speech signals cannot do without the A/D and D/A conversion of speech signals. In this design, a 14-bit dynamically adjustable high-precision programmable A/D and D/A TLC32044 chip produced by TI of the United States is selected. As shown in Figure 4, TLC32044 consists of anti-aliasing input filter, A/D, D/A, output reconstruction filter, etc. The separation of analog and digital ground, analog and digital power supply can reduce noise and ensure a wide dynamic range. The analog circuit part uses a differential circuit to minimize noise. TLC32044 also has programmable sampling frequency, and its sampling frequency can be controlled by software in the range of 7.2kHz to 19.2kHz. It can work in four working states: synchronous word, byte transmission and asynchronous word, byte transmission, respectively using 16-bit word or 8-bit byte serial communication mode, with a maximum conversion accuracy of 14 bits, and can work with only an external 5.184MHz clock. The chip can accommodate 2 analog signal inputs at the same time through programming. After the system is powered on (or reset), it works in its default working mode, that is, 16-bit word or 8-bit byte serial communication mode, with a maximum conversion accuracy of 14 bits, and only needs an external 5.184MHz clock to work. The chip can accommodate 2 analog signal inputs at the same time through programming. After the system is powered on (or reset), it works in its default working mode, that is, 16-bit word synchronous serial communication, with a sampling frequency of 8kHz. To change the working state of TLC32044, you can program and send the control word to TLC32044 through the DX pin.

In the DR timing, the D1 and D0 bits are empty, and the effective precision of A/D conversion is D15~D2; while the D1 and D0 bits in the DX timing are used as control bits. FSR and FSX are the receiving and sending frame synchronization signals, which are 8kHz. In the synchronous working mode, the two are exactly the same.

3.2 TLC32044 peripheral interface circuit

In order to realize the voice input and output of the system and ensure effective gain, the input and output voice signals must be amplified. The circuit is shown in Figure 5. In this system, a high-performance, low-noise LM1458 amplifier is used to adjust the gain of the input and output voice signals through a 20kΩ adjustable potentiometer. A -5V power supply is required in this circuit, while general circuits only provide a +5V power supply. Therefore, the MAX660 chip is used in the circuit design to achieve the conversion of +5V to -5V power supply. In this way, the entire circuit can be powered by a single power supply.

System Analysis

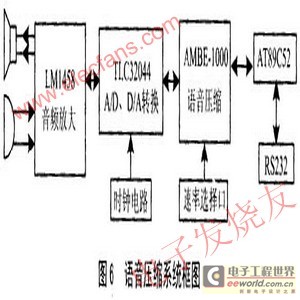

The block diagram of the voice compression system is shown in Figure 6. The system can select the working rate independently. In the serial active frame mode, the serial input and output pins of AMBE-1000 can be short-circuited to perform system self-test to confirm whether the system is normal. When designing the system, attention should be paid to the distinction between analog ground and digital ground to avoid the introduction of background noise. This circuit design has been used in the end voice compression of intelligent communication terminals, which can reduce the amount of voice data and increase the confidentiality of voice. At the same time, this circuit can also be used in solid-state interview machines, just add a rewritable Flash chip and control keys.

Previous article:The relationship and principle of series and parallel connection of speakers

Next article:How to reduce the noise of active speakers

- Popular Resources

- Popular amplifiers

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- Rambus Launches Industry's First HBM 4 Controller IP: What Are the Technical Details Behind It?

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- How much do you know about impedance matching?

- DLP Dynamic Floor Projection Technology for Automotive Exterior Lighting

- 16 PCB welding defects! What are their hazards?

- I saw a post next door and it seems okay since I work there every day.

- EEWORLD University ---- PCB Design Video - Learn PADS PCB Design in 1 Day

- 【NUCLEO-L552ZE Review】-3: Arduino vs. Mbed?

- What is the reason why IIC fails when the MSP430FR2311 power supply voltage rises to 3.5V? How to solve it?

- Signal linear transformation problem

- [GD32E231 DIY Contest] Part 4: Summary

- MSP430 microcontroller peripheral crystal oscillator design selection and reference solution

TC52N3730ECTRT

TC52N3730ECTRT

京公网安备 11010802033920号

京公网安备 11010802033920号