Green energy standards, lower costs, and the need for higher audio fidelity are driving the use of Class D amplifiers in high-power audio. Traditional analog implementations (such as Class AB topology) are complex and inefficient, but have dominated the high-end audio market due to their high-fidelity performance for audio. Class D systems are simpler to design, more efficient, and offer high-fidelity capabilities comparable to analog amplifiers, and are rapidly closing the gap in the high-end audio market.

A typical Class D audio system first converts the analog audio input signal into a digital PWM signal, performs power amplification in the digital domain, and then converts the digital signal into an analog audio signal for output. As shown in Figure 1, the input audio signal is sent to a pulse width modulator (PWM), which consists of an operational amplifier and a comparator. The modulator digitizes the audio by generating a modulated duty cycle signal that is proportional to the instantaneous value of the audio input signal.

Figure 1: Basic block diagram of a Class D amplifier

The PWM signal is appropriately level-shifted and sent to the gate driver, which controls a two-state power circuit consisting of MOSFETs (M1 and M2). The amplified signal then passes through an output filter (eliminating the PWM carrier frequency), and ultimately only the amplified analog audio signal drives the speaker. External loop filtering is performed by feeding the filter input signal back to the error amplifier input, reducing distortion and noise, further improving audio output fidelity.

Class D Amplifier Design

effect

Traditional analog power amplifiers rely on linear amplification circuits, which are prone to high power losses. In contrast, Class D amplifiers can achieve power efficiencies of 90% or more (depending on the design). This high efficiency benefit is inherent in Class D amplifier technology, where the amplification mechanism uses binary switches (usually power MOSFETs). These switches are either fully on or fully off, with only a small amount of time spent in state transitions. The discrete switching action and low MOSFET on-resistance reduce I2R losses and improve efficiency. However, in practice, the switch transition time (dead time) must be long enough to avoid a sharp drop in efficiency when both switches are running simultaneously.

High Fidelity

Audio fidelity can be defined as the integrity of sound after reproduction. For audio systems, fidelity has always been synonymous with sound quality. At the same time, other indicators are also used to measure fidelity, and the measurement of some indicators is particularly challenging for designers. The two most challenging indicators are: total harmonic distortion (THD) and noise (N), collectively referred to as THD+N.

THD is an accurate measurement of an audio system, much like hi-fi itself. Errors in the reproduced signal come from harmonics of the input frequency produced by other components, which are noticeably different from the pure output signal. THD is the ratio of all unwanted harmonic frequency energy to the fundamental input frequency energy, typically measured at half power for a given system. THD performance is typically less than 0.1% for most non-hi-fi audio applications, with discerning listeners often requiring THD levels as low as 0.05% or even lower.

The output noise level is a measure of the noise floor level of the amplifier output with no signal input. For most speakers, a noise floor of 100-500uV is inaudible at a normal listening distance, and a noise floor of 1mV is too loud, so THD+N is a good indicator of the audio fidelity of the amplifier.

Class D Driver ICs: Features and Benefits

Programmable dead time

The dead time of a Class D amplifier (i.e., the period of time when both switches are off) directly affects efficiency and THD. A dead time that is too short will cause shoot-through current and reduce efficiency, while a dead time that is too long will increase THD, which will adversely affect audio fidelity.

Dead time must be set precisely to find the "sweet spot" that optimizes both power efficiency and THD. Today's typical high voltage audio drivers have imprecise, overlapping dead time settings (i.e., 1/n delay values). As a result, most designers choose to handle dead time with discrete components, which is both expensive and time consuming. A simple and economical solution is to integrate a gate driver with a high-precision dead time generator.

Figure 2

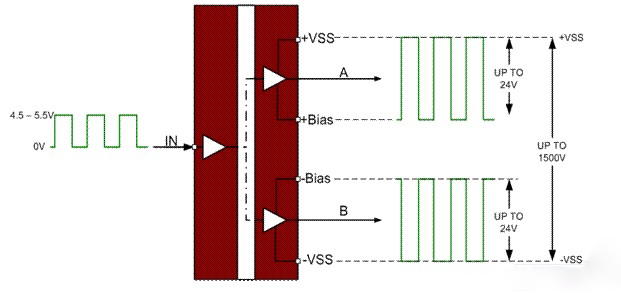

Level conversion

Implementing a dual-state Class D amplifier can be challenging due to the input level shifting requirements. In high power Class D amplifiers, it is best to provide a high voltage supply rail (±VSS) for the power MOSFET stage. In a practical Class D amplifier design, ±100Vdc voltages can produce up to 600W of audio power into an 8Ω load.

Most existing high voltage IC (HVIC) Class D drivers lack the ability to convert the low voltage modulation section to the high voltage supply section. Drivers that can provide level shifting have other deficiencies that make them less than ideal for Class D operation (e.g., the driver output ground terminal uses a negative voltage rail, requiring the input drive signal to be level shifted to the negative supply). Adding this functionality through discrete components is costly, difficult to design, and takes up a lot of space, so a level shifting solution with a high voltage bipolar supply interface is a significant advantage for Class D designs.

Typically, most driver solutions do not provide input-output isolation, nor isolation between drivers, so additional components are required to provide a level conversion mechanism.

Figure 3: Level translation required to interface between a low voltage digital modulator and a high voltage bipolar output supply

Reliability and noise suppression

Typical existing gate driver ICs are prone to latch-up on high voltage transients of 20V/ns or greater and typically have no suppression of high slew rate transient noise that couples from the power stage feedback to the precision digital inputs. This lack of noise suppression is a major disadvantage when trying to achieve the best audio fidelity while keeping the noise floor as low as possible.

High frequency operation

One of the best features of a Class D gate driver is the ability to operate at high switching frequencies with minimal propagation delay. These features allow the total loop delay in the feedback path to be very low, resulting in the best possible noise performance. Operating at a higher frequency also increases the "loop gain," improving the amplifier's distortion performance. Most existing HVIC drivers only support modulation frequencies up to 1MHz.

Integration

In today's competitive global market, a solution that integrates all of these features will provide Class D amplifier designers with great benefits, allowing them to get their products to market sooner by reducing design time, component count, insertion cost, and lower reliability due to higher device count.

summary

The characteristics of Class D amplifiers far exceed those of traditional analog amplifiers, including lower THD, smaller board space, higher power efficiency, and lower BOM cost. Highly integrated gate driver ICs have a significant positive effect on system architecture and audio performance. Silicon Labs' Si8241/8244 audio driver is the first high-power Class D amplifier solution to integrate all features into a single IC package. The advantages of these gate drivers include: high-precision dead time setting for lowest THD and best power efficiency; no need to increase the number of complex designs and components for input signal level conversion; isolated output drivers to simplify the implementation of dual-state switches; and high suppression of transient power supplies.

Previous article:125W Class D Subwoofer Power Amplifier Circuit Design

Next article:Design of a Fully Differential Operational Amplifier in 0.6μm CMOS Technology

Recommended ReadingLatest update time:2024-11-16 17:54

- Popular Resources

- Popular amplifiers

-

西门子S7-12001500 PLC SCL语言编程从入门到精通 (北岛李工)

西门子S7-12001500 PLC SCL语言编程从入门到精通 (北岛李工) -

Small AC Servo Motor Control Circuit Design (by Masaru Ishijima; translated by Xue Liang and Zhu Jianjun, by Masaru Ishijima, Xue Liang, and Zhu Jianjun)

Small AC Servo Motor Control Circuit Design (by Masaru Ishijima; translated by Xue Liang and Zhu Jianjun, by Masaru Ishijima, Xue Liang, and Zhu Jianjun) -

Intelligent Control Technology of Permanent Magnet Synchronous Motor (Written by Wang Jun)

Intelligent Control Technology of Permanent Magnet Synchronous Motor (Written by Wang Jun) -

100 Examples of Microcontroller C Language Applications (with CD-ROM, 3rd Edition) (Wang Huiliang, Wang Dongfeng, Dong Guanqiang)

100 Examples of Microcontroller C Language Applications (with CD-ROM, 3rd Edition) (Wang Huiliang, Wang Dongfeng, Dong Guanqiang)

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- TMS320F28335 Experimenter Board Kit

- OPA2369 Issues

- Share DSP281x read and write EEPROM 24C02 routines

- TouchGFX Design + Make a Rubik's Cube (5)

- [Summary] Let's get our hands dirty and do a "labor" transformation of old things

- [GD32L233C-START Review] 9. IAP program upgrade - based on YMODEM protocol

- What is it like to ask programmers to write code by hand with pen and paper after a power outage?

- [Sipeed LicheeRV 86 Panel Review] III. Building a cross-compilation environment: success and failure

- I need help from a master, diesel engine electronic throttle pedal signal synchronization failure

- In three minutes, let me show you what load is.

西门子S7-12001500 PLC SCL语言编程从入门到精通 (北岛李工)

西门子S7-12001500 PLC SCL语言编程从入门到精通 (北岛李工)

京公网安备 11010802033920号

京公网安备 11010802033920号