Introduction

This KWIK (Know-how With Integrated Knowledge) circuit application note provides step-by-step guidance for solving specific design challenges. This article will discuss the requirements associated with a specific application, how to utilize a common formula for conversion, and how to easily extend it to other relevant application specifications.

In applications such as electromagnetic flow meters or bioelectrical measurements, a small differential signal is in series with a much larger differential offset. These offsets often limit the gain you can get at the front end, reducing the overall dynamic range, especially on signal chains using lower supply voltages powered by batteries.

This guide will help you design a low-power, AC-coupled signal conditioning circuit that suppresses large offset voltages while amplifying small differential signals. Additionally, this guide will help with the division of gain stages around high-pass filters and noise considerations.

Design specification example

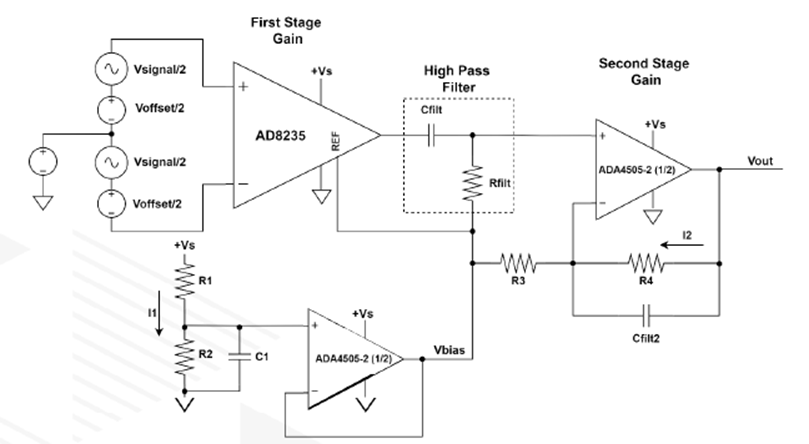

Design choices for the circuit shown in Figure 1 depend heavily on the amplitude range and frequency of the input signal and offset, as well as the supply voltage to avoid saturation. Power consumption and size are also critical for battery-powered applications. Example design specifications are shown in Table 1.

Figure 1. Battery-powered AC-coupled signal conditioning circuit

Table 1. Main design specifications of the circuit shown in Figure 1

Design description

design steps

1. Set Vbias:

To keep the supply current contribution less than 1uA, set R1 = R2 = 10MΩ.

Output of resistor divider before ADA4505:

Using R1 and R2 with less than 1% tolerance will keep the Vbias variation low, helping to maximize the output swing of the first and second gain stages. Vos combined with 1% resistor and ADA4505 buffer:

In order to eliminate the AC power interference and noise of the resistor, set C1 so that the cutoff frequency is at least 0.5Hz less than the lowest frequency of Vsignal. In this case, C1 is set to 0.1uF:

2. Set the first level gain

First, consider the limitations of the AD8235 output swing range on the supply rails. For a given supply voltage, these values can be found from the "High Output Voltage" and "Low Output Voltage" sections of the data sheet. There is no resistive load in this case, and to be conservative we use the worst case scenario with a 100kΩ swing:

Since the inputs are fully differential, this will be the worst case output swing in terms of Vbias.

For positive input signal (Vbias_max=1.67V):

For negative input signal (Vbias_min=1.63V):

Now to set the gain, calculate the total expected differential input signal and use the lower bounds of the positive and negative swing ranges to set the maximum swing range:

The minimum gain of the AD8235 without the external Rg resistor is 5, so we use this value to leave some margin for DC errors and other conditions. Additionally, the "diamond plot" for the selected gain must be examined. See the Design Simulation section for this operation.

3. Set the high-pass filter

Assuming that the component tolerances of Rfilt and Cfilt are ±10%, the fastest time constant should be less than the lowest frequency of Vsignal:

If you choose Rfilt=100kΩ and rearrange the equation:

Using the closest standard capacitor value and setting Cfilt = 4.7uF, the updated nominal cutoff frequency is:

If the design specifications require some minimum attenuation at the minimum signal frequency, it is easy to check the cutoff frequency of a given filter. See an example of this circuit:

Now to set the gain, calculate the total expected differential input signal at the input of the ADA4505 and use the lower limit of the positive and negative swing range to set the maximum swing range:

We use a gain of about 25x to leave some headroom for DC errors and other component tolerances, and choose R4 = 1MΩ to keep the supply current low at maximum signal swing.

Rounding R3 to the next typical resistor value gives us 43kΩ.

4. Set the second level gain

Using a similar approach to the first-stage gain, first determine the ADA4505 output swing range limits according to the data sheet. The resistive load is unknown, to be conservative we will use 10kΩ worst case:

Since the inputs are fully differential, this will be the worst case output swing in terms of Vbias.

For positive input signal (Vbias_max=1.67V):

For negative input signal (Vbias_min=1.63V):

5. Use Cfilt2 to set the low-pass filter

First use the gain-bandwidth product (GBP) to determine the bandwidth of the ADA4505 at a gain of 24.26x:

If the target bandwidth needs to be reduced further due to the expected maximum signal frequency, and/or if broadband noise needs to be limited, capacitor Cfilt2 can be used. Assuming the component tolerance of R4 and Cfilt2 is +/-10%, the slowest time constant should be greater than the Vsignal maximum frequency

Using R5 of 1MΩ, rearrange the equation:

This can then be rounded to the nearest standard capacitance value of 3.3nF, so the updated cutoff frequency is:

If the design specifications require some minimum attenuation of the maximum signal frequency, it is easy to check the cutoff frequency of a given filter.

See an example of this circuit:

Design Simulation

To examine an instrumentation amplifier's common-mode input range versus output voltage, or "diamond plot," you need to provide the supply voltage +Vs, reference voltage, gain, common-mode swing, and differential input swing. Analog Devices' Instrumentation Amplifier Diamond Plot tool can help understand whether the input swing is within the operating range of the device. Note that the output swing used by this tool uses worst-case load conditions (minimum resistive load). Therefore, if designed to the tool's limits, the system will have more margin for larger resistive loads.

Looking at the results in Figure 2, the green outline is the usable range of the AD8235 given the supply voltage, output swing, input common-mode range, and device reference voltage. The red outline shows how much of the available range you use for a given common-mode and differential input-mode swing. The goal is to keep the red contour within the green contour. If certain conditions violate this requirement, the tool will display an error and provide suggestions. To further understand what is happening inside the instrumentation amplifier, the Internal Circuitry tab displays the voltages at the internal nodes.

LTspice is an excellent simulation tool for checking the design process calculations performed above, including other meaningful specifications such as noise performance at the target signal band. The LTspice schematic is shown in Figure 3 below. The first simulation is a transient simulation with a DC offset of 300mV and an input signal of ±10mV (5Hz). Figure 4 shows the signals at various stages in the circuit. The green curve is the total differential input signal. The red curve is the amplified signal at the output of AD8235. The teal curve shows the high-pass filter output after removing the DC offset, and the final blue curve shows the final amplified 5Hz signal.

Figure 2. AD8235 Diamond Plot Tool Example

Figure 3. LTSPICE schematic diagram

Figure 4. Transient simulation at different stages of the circuit, Voffset=300mV, Vsignal=±10mV

Figure 5 uses a harsh 2Vp-p 60Hz Vcm input signal (green) without any differential signals applied. It's unlikely that a 60Hz signal would reach such high levels in a battery-powered application, but it's something to consider. Note that all signals in the diagram are at a DC voltage of Vbias = 1.65V. Most of the attenuation comes from the AD8235's CMRR, which is greater than 60dB at 60Hz (red and teal curves ~7.5mVp-p). The final output (blue curve ~110mVp-pk) is amplified and partially attenuated by a 48Hz low-pass filter.

Figure 6 shows what the signal will look like if both common-mode and differential-mode inputs are present. You can see that the 60Hz signal appears as ripple on top of the slower 5Hz signal that has been amplified. Figure 7 shows that for the simulation setup in Figure 4, the supply current from +Vs is less than 52uA.

Figure 5. Transient simulation at different stages of the circuit, Vcm=1.65V±1V

Figure 6. Transient simulation performed at different levels of the circuit, Voffset=300mV, Vsignal=±10mV, Vcm=1.65V±1V

Another simulation in Figure 8 shows the frequency response of the circuit in Figure 3. The peak amplitude was determined at a frequency of 5Hz, with cursors 1 and 2 placed at the -3dB points of the high-pass and low-pass filters respectively. The table below shows how the calculated results compare to the measured results.

Table 2 - Calculation results and simulation results

In the frequency response, it is worth mentioning that for the low-pass filter used in this circuit, when Cfilt2 is shorted, the gain of the second stage drops to 1. This means that the signal from the AD8235 and the high-pass filter will not continue to attenuate until it reaches the bandwidth of the AD8235. For further filtering, a low-pass filter can be placed at the output of the second gain stage, as is usually done before the ADC.

Another simulation in Figure 9 shows the voltage noise density versus frequency (referred to the input) for the circuit in Figure 3. This is done by dividing the output noise by the total gain of the solution (121.3). Use the rms noise calculator to calculate the integrated noise from 0.5Hz to 40Hz (i.e. the target Vsignal frequency range). To use this calculator, first right-click on the x-axis of the graph to set the target frequency range, then hold down the Ctrl key and left-click on the waveform name (V(onoise)/121.3). RMS noise can be easily converted to peak-to-peak noise using the following equation:

A quick check of the AD8235 noise determined that this was the dominant noise source. This makes sense because all other noise sources in the circuit are after the first gain stage, reducing the total input-referred noise contribution.

Previous article:STMicroelectronics’ low-temperature drift, high-accuracy op amp increases operating temperature to 175°C

Next article:Chongqing Dongwei Electronics launches high-performance anti-RF interference MEMS silicon microphone amplifier chip

- USB Type-C® and USB Power Delivery: Designed for extended power range and battery-powered systems

- ROHM develops the second generation of MUS-IC™ series audio DAC chips suitable for high-resolution audio playback

- ADALM2000 Experiment: Transformer-Coupled Amplifier

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Intel promotes AI with multi-dimensional efforts in technology, application, and ecology

- ChinaJoy Qualcomm Snapdragon Theme Pavilion takes you to experience the new changes in digital entertainment in the 5G era

- Infineon's latest generation IGBT technology platform enables precise control of speed and position

- Two test methods for LED lighting life

- Don't Let Lightning Induced Surges Scare You

- Application of brushless motor controller ML4425/4426

- Easy identification of LED power supply quality

- World's first integrated photovoltaic solar system completed in Israel

- Sliding window mean filter for avr microcontroller AD conversion

- What does call mean in the detailed explanation of ABB robot programming instructions?

- STMicroelectronics discloses its 2027-2028 financial model and path to achieve its 2030 goals

- 2024 China Automotive Charging and Battery Swapping Ecosystem Conference held in Taiyuan

- State-owned enterprises team up to invest in solid-state battery giant

- The evolution of electronic and electrical architecture is accelerating

- The first! National Automotive Chip Quality Inspection Center established

- BYD releases self-developed automotive chip using 4nm process, with a running score of up to 1.15 million

- GEODNET launches GEO-PULSE, a car GPS navigation device

- Should Chinese car companies develop their own high-computing chips?

- Infineon and Siemens combine embedded automotive software platform with microcontrollers to provide the necessary functions for next-generation SDVs

- Continental launches invisible biometric sensor display to monitor passengers' vital signs

- Multinational automotive electronics companies implement "China strategy"

- EETalk| How to design a good antenna?

- EEWORLD University Hall----Choosing the right oscilloscope probe

- Is it difficult to switch from security and industrial control electronics to medical electronics?

- Pengpaiwei PT32L033 series overview and features

- Holtek launches new IC with TinyPower technology

- Introduction to TI's fifth-generation DSP product TMS320C5X

- 51 Microcontroller timer 0 affects the normal operation of timer 1. How to solve it?

- Drone battery power monitoring system based on Gizwits IoT platform

- Linear power supply chips are hot? Problem analysis

【Follow me Season 2 Episode 1】-Mission Code (Adafruit Circuit Playground Express Development Board)

【Follow me Season 2 Episode 1】-Mission Code (Adafruit Circuit Playground Express Development Board) 【Follow me Season 2 Episode 1】Source code

【Follow me Season 2 Episode 1】Source code AD8642ARZ

AD8642ARZ

京公网安备 11010802033920号

京公网安备 11010802033920号