The purpose of a development tool is not only to debug complex problems, but also to improve development efficiency. Sometimes, achieving this goal depends more on the convenience and usability of standard product features than on effective power characteristics. A convenient feature in most professional debuggers is to display the memory-mapped SoC peripheral registers as register groups, including their names, bit fields, and descriptions, which are consistent with the peripheral documentation.

When developing for FPGAs, things get more complicated. FPGA vendors often provide FPGA hardware libraries, such as encryption/decryption modules, math algorithm acceleration modules, and peripheral controllers. However, it is up to the hardware developer to determine how many modules to synthesize into the FPGA and where they are located in the memory map of the processor, which means that the software debugger cannot immediately provide a view of the peripheral registers. Software developers can manually generate debugger peripheral description views, but manual editing is time-consuming and prone to errors. The solution requires communication between the FPGA synthesis tool and the software debugger. The Altera QSys system configuration tool generates peripheral register description files for the complete FPGA design, and the ARM DS-5 debugger can automatically import the files to display the FPGA IP registers as if they were part of the hard-core processor system.

Figure 1: Automatically generated peripheral register view and imported into the DS-5 debugger

System-level performance analysis

Today, product developers are more concerned with debugging performance issues, striving to implement more functionality on the same hardware, or reducing power consumption. As a result, tool vendors are increasingly focusing on performance and power analysis tools.

One of the main reasons for choosing an SoC device (one that integrates a processor and FPGA fabric) is the ability to use FPGA hardware blocks to accelerate software work. For example, you can use an FFT decoder or a DES decryption algorithm in the FPGA fabric to free up the processor to do other tasks, or put it to sleep to save power. For these devices, the tool should be able to see the relative resource utilization of the processor and FPGA IP blocks. Designers can then use this information to optimize the system.

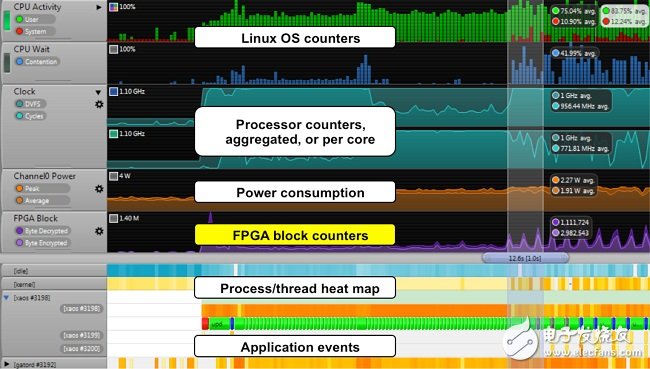

Although instruction tracing is used to optimize software codecs and other performance software, some specific analysis tools such as the ARM DS-5 streamlined performance analyzer are still needed for ARM application processors running operating systems such as Linux and Android. ARM DS-5 uses the Linux driver running in the target to sample information at certain intervals, and each time the event counter provides captured task switch information, such as:

● Operating system events such as processor load.

● Processor events such as branch mispredictions.

● System Events. These counters enable users to find system-level bottlenecks.

● Software annotations, used to report events of interest.

Seeing this information displayed on a timeline allows developers to understand the interaction between software and hardware.

For mixed processor and FPGA devices, the Streamline Analyzer can be used to optimize both the hardware and software. The only basic components required in the hardware are memory-mapped registers, and the utilization of each different IP block is calculated. The streamline can then be configured to access these new counters and display their values over time, correlating them with CPU utilization and other system-level counters.

Figure 2: Timeline view in ARM DS-5 Streamline.

Users with power requirements can extend the flow line through the ARM energy consumption probe to monitor and view the voltage and current consumption on certain power paths in the target. On the FPGA target, these power lines usually power the CPU subsystem, FPGA core and FPGA I/O, but they also monitor the main power supply of the entire product. By viewing the relationship between power consumption, software activity and system utilization, as well as being able to benchmark energy consumption, developers can optimize the system for power consumption and battery life.

in conclusion

New SoC devices, including ARM application processors and FPGA architectures, bring new opportunities for more efficient products. Innovations in on-chip debugging hardware, FPGA tools, and software debugging and analysis tools have matched hardware innovations, so developing for these devices and taking full advantage of their power characteristics has become as easy and efficient as developing software on fixed ASIC devices.

Previous article:What kind of environmental performance should a good connector have?

Next article:FPGA and multi-core CPU make embedded design more flexible

- Popular Resources

- Popular amplifiers

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

- Detailed explanation of intelligent car body perception system

- How to solve the problem that the servo drive is not enabled

- Why does the servo drive not power on?

- What point should I connect to when the servo is turned on?

- How to turn on the internal enable of Panasonic servo drive?

- What is the rigidity setting of Panasonic servo drive?

- How to change the inertia ratio of Panasonic servo drive

- What is the inertia ratio of the servo motor?

- Is it better for the motor to have a large or small moment of inertia?

- What is the difference between low inertia and high inertia of servo motors?

- Questions about op amp TIA circuit

- Deping Technology Shenzhen Co., Ltd.

- I have never understood several parameters of MOS tubes. Please help me explain them.

- Luminous flux of LED after aging

- Image storage and display system based on SDRAM——Study record

- The smallest Arduino board

- Wi-Fi 6E front-end module: Perfectly demonstrates all the performance of the 6GHz band

- Design of wireless intelligent air conditioning control system peripheral circuit using ZigBee technology

- The static digital tube display problem of 51 single chip microcomputer in Puzhong

- 【Application development based on NUCLEO-F746ZG motor】3. Hardware connection and motor identification

MCP601-I/P

MCP601-I/P

京公网安备 11010802033920号

京公网安备 11010802033920号