In the design of general digital/analog converters, the decoding structure usually adopts a segmented structure. In general designs, in order to reduce delay, latches are usually used, and complex current source structures are used at the same time. This structure usually requires large energy consumption, and the sampling rate is not high enough. In order to obtain a higher sampling rate and better linearity, a unit current unit matrix and a decoder circuit are designed based on the TG structure, and a simple current unit circuit design is adopted.

1 Structure selection

Here, a current steering DAC design is adopted. This is because the voltage type DAC requires more components and more switching layers, and is generally used in low-speed converters; the charge type DAC increases sharply with the increase of accuracy, and is sensitive to parasitic capacitance; the current type DAC has the advantage of high speed, but is not suitable for low-voltage circuits. The current steering DAC is an improvement on the current type DAC and is often used in segmented circuits.

The decoding methods of digital/analog converters are generally divided into binary, thermometer and segmented. The thermometer decoding method has great advantages in reducing DNL and INL compared to the binary decoding method, but its disadvantage is that the circuit structure is complex. Combining binary code and temperature code produces a segmented structure. Thermometer decoding is used for high bits with matching requirements and high precision; binary code is used for low bits to reduce area. This segmented structure has the advantages of simple binary code structure and good linear characteristics of temperature code. In this design, a high-speed 8-bit DAC composed of current source matrix logic circuit is proposed. According to Lin and Bult, the relationship between area and segment ratio is made (see Figure 1). In order to obtain a compromise result in terms of speed, resolution, power consumption, chip area, circuit performance and other aspects, the upper 6 bits of the segment use thermometer decoding structure and the lower 2 bits use binary decoding structure. The structure of the entire CS-DAC is shown in Figure 2.

Figure 2 is an example of the basic structure of an 8-bit segmented current rudder. The figure uses a 6+2 segmented structure, and the upper 6-bit digital signal is converted into a thermometer code through row decoders and column decoders, which control 26-1=63 unit current sources respectively to form an 8×8 current source matrix. The extra current source is used as a dummy device, and the sum of the currents of the 63 unit current sources and the lower 2-bit binary weighted current source forms the current of the overall current source in the array.

2 Decoding logic circuit

In DAC design, current source unit, decoder and glitch elimination (noise) structure are important parts, and the performance of DAC is determined by these parts. In order to improve the dynamic linearity at high frequency, a combinational logic decoding circuit composed of transmission gate and transistor is proposed here.

2.1 Transmission gate logic

Because NMOS tube can transmit through logical variable 0, and PMOS tube can transmit through logical variable 1, these two MOS are placed in parallel to form a complementary structure. Here, a transmission gate (TG) can be obtained, and for TG, logical variables 0 and 1 can be transmitted well. As we all know, the delay time between decoders is the main cause of glitch occurrence, and compared with the logic circuit using CMOS, the logic circuit designed with TG has better performance and smaller delay. It has been verified that all two-input logic gates can be composed of transmission gates and inverters. As an example, to realize NAND gate logic, all CMOS technology requires 6 transistors, but only 5 transistors are needed using TG structure. On the internal DAC chip, it has two signals and a flip signal, so there is no need for inverters, so two transistors are reduced. The experimental results show that the chip area and power consumption are greatly reduced.

2.2 Logic Decoding Circuit

In order to reduce power consumption and delay, the row and column decoding with the minimum logic level should be designed, and the TG logic circuit should be used to form a 3-8 bit row and column decoder. In this way, the row decoder is obtained from the upper 3 bits and the column decoder is obtained from the middle 3 bits. The row decoder circuit using TG is shown in Figure 3.

The row decoder structure is basically the same as the column decoder, but there is no power node. Another great benefit of using TG logic decoder is that it can reduce the number of transistors. In static logic, the decoder of reference [9] consists of 84 transistors, but the row and column decoders composed of TG structure have 30 transistors, and the total number is 60. This means that the chip area can also be reduced. Fewer transistor levels also help reduce delay. On the other hand, the maximum number of logic gates using TG structure can be reduced to 2 levels; the maximum number of gate levels of full CMOS structure without transmission gate structure is 3. The above fully demonstrates that the use of TG structure is more conducive to reducing delay and improving operating frequency. Table 1 gives the relevant parameter comparison.

2.3 Working Principle

There are three situations for the unit current source to be turned on or off when decoding with the row-column decoder. The first situation is that both the row and the next row are "1". In this case, the current source is selected regardless of whether the column control signal is "1". In other words, the corresponding current source switch state is on. The second situation is that the row control signal is "1", but the control signal of the next row is "0". At this time, whether the current source is selected depends on the column control signal. If the column control signal is "1", the current source is selected; if the column control signal is "0", the current source is not selected and is in the off state. The third situation is that the control signals of the row and the next row are both "0". In this case, no matter how much the control signal of the column is, this current source will not be selected and is in the off state. The switch circuit composed of TG is shown in Figure 4.

3 Current source circuit and glitch reduction circuit

The current source circuit is an important part of DAC. At the same time, in order to reduce the glitch reaction, the circuit for reducing glitch will be introduced below.

3.1 Current unit

Commonly used designs all adopt complex structures that reduce circuit noise and reduce current sources. For example, differential circuits, bias circuits, reference currents, etc. require a large number of transistors. In this design, a simple current unit structure is used, and the current source adopts a current source unit composed of two transistors. Compared with other chips, the area of the circuit can be greatly reduced, as shown in Figure 5.

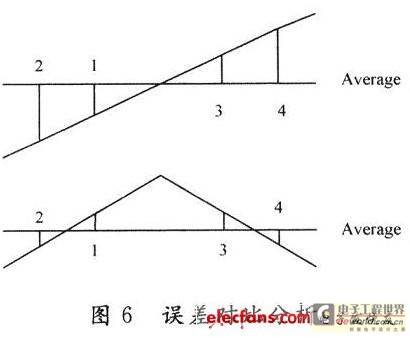

According to the comparison between the gradient error and the symmetric error shown in FIG6 , the error is well reduced by adopting a hierarchical symmetric switch sequence layout in the unit current source matrix.

3.2 Glitch Reduction Circuit

In the basic current source unit, the output signal will be relatively stable. In this design, the current source is controlled by the output signal of the switching circuit, but the output signal is not accurate enough. Therefore, in order to compensate for this shortcoming and improve the SNR of the circuit, a glitch reduction circuit is needed, as shown in Figure 7.

4 Experimental results

The DAC designed in this paper is based on 0.25 μm CMOS technology. The 8-bit high-speed DAC is suitable for high-definition video. The number of TG transistors and circuit levels can be significantly reduced. At the same time, the use of TG structure can effectively reduce the circuit delay time and greatly reduce the burrs. The results show that this design can achieve a 1.5 GHz sampling rate and 21 mW low power consumption.

The specific parameter indicators are shown in Table 2.

5 Conclusion

This paper proposes a current source unit matrix based on a new transmission gate (TG) structure, a decoding logic circuit and a high-speed 8-bit CMOS current-steering digital-to-analog converter (CS-DAC) suitable for high-definition video.

Previous article:How to use amplifiers to design robust and cost-effective solutions

Next article:Design of Sample-and-Hold Circuit in 13-bit 40MS/s Pipeline ADC

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- GD32307E-START IO analog SPI control RGBLED (03)

- 【GD32E503 Review】+ cJSON Porting Test

- Is one of the two MOS tubes in the step-down switching power supply chip used to replace the diode?

- The NiMH battery charging circuit is relatively complex, and some SMD components cannot be found in the specification sheet.

- Is there any plugin or function in KEIL or other compilation environment that can help check if there is an error like if ( a=1 )

- [RVB2601 Creative Application Development] + Indoor Environment Monitoring Platform

- Simple explanation of the principle of DDS in FPGA

- Problems with dsp2812 downloading using C2Prog

- EEWORLD University Hall----Computer Vision (Lu Peng, Beijing University of Posts and Telecommunications)

- Why do the 2D lines in the DXF exported from PADS become very thick after opening it in CAD?

Electronic Engineers from Entry to Mastery

Electronic Engineers from Entry to Mastery

京公网安备 11010802033920号

京公网安备 11010802033920号