1 Introduction

With the emergence of the Internet and the rapid development of Ethernet, more and more devices are controlled based on Ethernet. Currently, most Ethernet controllers on the market use packages with more than 80 pins, such as RTL8019AS, DM9008, CS8900A, etc. These devices are not only complex in structure and large in area, but also have high system overhead. Recently, Microchip launched the world's first 28-pin independent Ethernet controller ENC28J60, which can provide low-pin count, low-cost, streamlined remote communication solutions for embedded systems.

The Ethernet interface implementation scheme with ENC28J60 as the core is designed, and the design method of the hardware architecture of the system is described. On the basis of briefly introducing the structure, function and peripheral circuit of the Ethernet controller ENC28J60, the SPI communication between ENC28J60 and Atmega16 is explained. This scheme is not only low-cost, but also can achieve a transmission rate of more than 500Kbps, meeting the Internet control requirements of embedded systems.

2 ENC28J60 Network Interface Architecture

ENC28J60 is an independent Ethernet controller with an industry-standard serial peripheral interface (Serial PeripheralInterface, SPI). It complies with all IEEE 802.3 specifications and uses a series of packet filtering mechanisms to limit incoming data packets. It also provides an internal DMA module to achieve fast data throughput and hardware-supported IP checksum calculations. Communication with the host controller is achieved through two interrupt pins (INT and WOL) and SPI pins (SO, SI, SCK, CS), with a data transfer rate of up to 10Mb/s. Two dedicated pins (LEDA, LEDB) are used to connect LEDs for network activity status indication. Figure 1 shows a typical application circuit of ENC28J60.

ENC28J60 consists of 7 main functional modules: SPI interface, which acts as a communication channel between the main controller and ENC28J60; control registers, which are used to control and monitor ENC28J60; dual-port RAM buffer, which is used to receive and send data packets; arbiter, which controls the access to RAM buffer when DMA, transmit and receive modules issue requests; bus interface, which parses data and commands received through SPI; MAC module: implements MAC logic that complies with the IEEE 802.3 standard; PHY module, which encodes and decodes analog data on twisted pair. ENC28J60 also includes other supporting modules, such as oscillators, on-chip regulators, level converters (providing I/O pins that can accept 5V voltage) and system control logic.

According to the above description, ENC28J60 is very suitable for application in embedded network interface and has broad application development prospects.

3 Application of ENC28J60 in Embedded Network Interface

3.1 Hardware Circuit Design

ENC28J60 can be used to form network terminal nodes with different functions, such as network servers, devices with Internet functions, remote monitoring (data acquisition, diagnosis) equipment, etc. Figure 2 shows the hardware circuit schematic diagram of the embedded network interface based on ENC28J60. The circuit has: 2 LED status indicators are mainly used to display the network connection status, including whether PHY conflicts, whether the connection is established, whether data is received, connection speed, duplex mode, etc.; required bias resistor R3 (2kΩ, accuracy is 1%); high-speed LAN electromagnetic isolation module (i.e. RJ45 Ethernet interface). In the application, the physical port of ENC28J60 must be connected to the isolation transformer HR901170A in accordance with the requirements of IEEE802.3 for the physical layer specification, such as the spacing between the RJ45 jack and the isolation transformer should be as small as possible, and the routing of the output and input differential signal pairs should be well isolated.

The main controller in the circuit uses Atmel's ATmega16 microcontroller, which has an advanced RISC (Reduced Instruction Set Computer) structure, 16 kB programmable Flash memory, 512 B EEPROM and 1 kB on-chip SRAM, and has a wealth of peripheral interfaces. Its SPI interface allows ATmega16 to perform high-speed synchronous data transmission with peripherals. In this design, ATmega16 SPI is configured as a master mode, and ENC28J60 is a slave device. The SPI working mode of ATmega16 is set by CPOL and CPHA. According to the SPI read and write timing of ENC28J60, the SPI working mode of ATmega16 should be set to mode 0. ATmega16 synchronizes with ENC28J60 by setting the CS pin of ENC28J60 low. The SPI clock is started by the data written to the SPI transmit buffer register. The data transmission order on the SPI MOSI (PB5) pin is controlled by the DORD bit of the register SPCR. When it is set, the LSB (least significant bit) of the data is sent first, otherwise the MSB (most significant bit) of the data is sent first. We choose to send the MSB first, and at the same time, the received data is transferred to the receive buffer register. The CPU reads the received data from the receive buffer by right alignment. It should be noted that when multiple data need to be read from the ENC28J60, even if the ENC28J60 does not need the data serially output by the ATmega16, a data must be written to the SPI transmit buffer before each data is read to start the SPI interface clock. Since the SPI system has only one buffer in the transmit direction and two buffers in the receive direction, it is necessary to wait until the shift process is completed before writing to the SPI data register when sending; and when receiving data, it is necessary to read the currently received data by accessing the SPI data register before the next byte shift process is completed, otherwise the first data will be lost.

3.2 ENC28J60 Software Initialization

Before using ENC28J60 to send and receive data packets, the device must be initialized. Depending on the application, some configuration options may need to be changed. The initialization settings include the receive and transmit buffers, receive filters, crystal start time, MAC registers, and PHY registers. Before initializing the chip, turn off the interrupt input of the microcontroller, give a continuous low-level reset signal to the RESET pin, and then set the corresponding registers. After setting all the required registers, determine whether the clock start flag in the Ethernet status is set, and then turn on the interrupt.

After the system is initialized, it enters the main program loop, including the control function of the microcontroller and network data transmission. For the Ethernet transmission part, there are two main functions: one is to encapsulate and send the data to be sent according to the Ethernet data frame format; the other is to unpack the received Ethernet data frame for use by the application.

3.3 ENC28J60 sends data packets

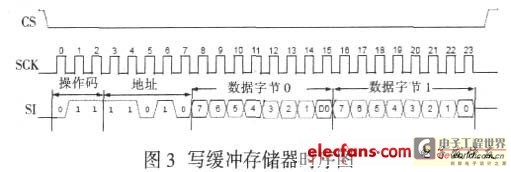

When sending or receiving data packets, you must first master the Write Buffer Memory (WBM) command. WBM allows the host controller to write bytes to the 8KB transmit and receive buffer memory. If the AUTOINC position in the ECON2 register is 1, then after writing the last bit of each byte, the EWRPT pointer will automatically increment to point to the next address (current address plus 1).

If the address 1FFF is written and AUTOINC is set to 1, the write pointer is incremented by 1 to point to 0000h. Pulling the CS pin low initiates the WBM command. The WBM opcode followed by the 5-bit constant 1Ah is then sent to the ENC28J60. After sending the WBM command and constant, the data in the memory pointed to by EWRPT is shifted into the ENC28J60, the highest bit first. After receiving 8 data bits, if AUTOINC is set to 1, the write pointer will automatically increment. The master controller can continue to provide the timing signal on the SCK pin and send data on the SI pin while keeping /CS low, so that the memory can be written continuously. When AUTOINC is enabled, bytes can be written to the buffer memory continuously in this way without redundant SPI commands. Pulling the CS pin high ends the WBM command. During the WBM operation, the SO pin is always in a high impedance state. See Figure 3 for the timing of the WBM operation.

The MAC in the ENC28J60 automatically generates the preamble and start-of-frame delimiter when transmitting. In addition, the MAC can generate padding (if required) and CRC fields according to the configuration. The host controller must generate all other frame fields and write them to the buffer memory to be transmitted. In addition, the ENC28J60 requires a packet control byte to be added to the front of the data packet to be transmitted. The host controller should: 1. Correctly program the ETXST pointer to point to an unused location in memory. It will point to the packet control byte, and in this design, the pointer should be programmed to 0120h; 2. Use the WBM SPI command to write the packet control byte, destination address, source MAC address, type/length, and data payload; 3. Correctly program the ETXND pointer. It should point to the last byte of the data payload. In this design, the pointer should be programmed to 0156h. 4. Clear the EIR.TXIF bit, set the EIE.TXIE bit and the EIE.INTIE bit to enable an interrupt after the transmission is completed (if necessary). 5. Set the ECON1.TXRTS bit to start the transmission. If a DMA operation is in progress when the TXRTS bit is set, the ENC28J60 will wait for the DMA operation to complete before transmitting. This wait is necessary because the DMA and transmit engines share the same memory access port. Also, if the DMAST bit in ECON1 is set after TXRTS has been set, the DMA will not take any action until the TXRTS bit is cleared. If a transmission is in progress, any bytes to be transmitted should not be read or written via the SPI. The master controller can cancel the transmission by clearing the TXRTS bit. If the data packet is sent successfully or the transmission is aborted due to an error cancellation, the ECON1.TXRTS bit will be cleared, a 7-byte transmit status vector will be written to the location pointed to by ETXND + 1, EIR.TXIF will be set to 1 and an interrupt will be generated (if enabled). To verify whether the data packet is successfully sent, the ESTAT.TXABRT bit should be read. If this bit is set, the host controller should query the ESTAT.LATECOL bit in addition to querying the various fields of the transmit status vector to determine the cause of the failure. The source code for writing a data packet is given below:

3.3 ENC28J60 receives data packets

Assuming the receive buffer has been initialized, the MAC has been configured correctly, and the receive filter has been configured to receive Ethernet packets, the host controller should: 1. If an interrupt is required when a packet is received, set the EIE.PKTIE bit and the EIE.INTIE bit; 2. If an interrupt is required when a packet is lost due to insufficient buffer space, clear the EIR.RXERIF bit and set the EIE.RXERIE bit and the EIE.INTIE bit; 3. Enable reception by setting the ECON1.RXEN bit. After setting RXEN, the duplex mode and the receive buffer start and end pointers cannot be modified. In addition, to prevent unwanted packets, it is recommended to clear RXEN before changing the receive filter configuration register (ERXFCON) and the MAC address. After enabling reception, packets that are not filtered out will be written to the circular receive buffer. Any packets that do not meet the filter criteria will be discarded, but the host controller will not be able to recognize that a packet has been discarded. When a packet is received and completely written to the buffer, the EPKTCNT register is incremented, the EIR.PKTIF bit is set, an interrupt is generated (if enabled), and the hardware write pointer ERXWRPT is automatically incremented.

4 Conclusion

The author's innovation: The embedded network interface designed by the ENC28J60 chip can be used in a variety of environments, can be configured as needed to complete system functions, and has obvious advantages in cost, size, power consumption, flexibility, etc., and can open up new application prospects for intelligent instruments and equipment, information appliances, etc.

Previous article:Classic case sharing: Comparative analysis of two keyboard scanning methods

Next article:Discussion on the Structure and Cooperation of Embedded Systems

Recommended ReadingLatest update time:2024-11-16 15:30

- Popular Resources

- Popular amplifiers

-

Semantic Segmentation for Autonomous Driving: Model Evaluation, Dataset Generation, Viewpoint Comparison, and Real-time Performance

Semantic Segmentation for Autonomous Driving: Model Evaluation, Dataset Generation, Viewpoint Comparison, and Real-time Performance -

Machine Learning and Embedded Computing in Advanced Driver Assistance Systems (ADAS)

Machine Learning and Embedded Computing in Advanced Driver Assistance Systems (ADAS) -

Intelligent program synthesis framework and key scientific problems for embedded software

Intelligent program synthesis framework and key scientific problems for embedded software -

arm_embedded_machine_learning_design_dummies_guide

arm_embedded_machine_learning_design_dummies_guide

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Sinlinx A64 Linux writes LED driver through device tree (with reference code, not tested)

- EEWORLD University Hall--Analysis of rules and techniques for high-speed PCB design

- LMV321 power supply range problem

- [SAMR21 New Gameplay] 29. WS2812 Application - Rainbow

- Several filtering methods for single chip microcomputer to resist interference by software

- What do you think of Huawei HiSilicon's operation?

- Problems encountered when LCD1602 scroll screen display

- Summary of the differences between SPMSM and IPMSM

- How did I get 296g of energy from Alipay Ant Forest?

- FAQ_How to use external low-speed clock in BlueNRG-x

Semantic Segmentation for Autonomous Driving: Model Evaluation, Dataset Generation, Viewpoint Comparison, and Real-time Performance

Semantic Segmentation for Autonomous Driving: Model Evaluation, Dataset Generation, Viewpoint Comparison, and Real-time Performance

京公网安备 11010802033920号

京公网安备 11010802033920号