The difference between CPU and MCU

When it comes to embedded development, the concept we come into contact with in daily life is MCU. The difference between MCU and CPU is that MCU integrates on-chip peripheral devices, while CPU does not. A simple example is that MCU integrates Flash and RAM in the chip to store programs and data. The corresponding embodiment in our personal PC is the hard disk and memory stick. Therefore, the difference between the two is only whether the peripheral devices are integrated or not. The most essential working principle of the two is interoperable.

Components of a CPU

The CPU is an electronic component composed of many transistors. From a functional point of view, the CPU consists of four parts: registers, controllers, arithmetic units, and clocks. Their respective functions are as follows:

Register: can be used to temporarily store instructions, data and other processing objects.

Controller: responsible for reading instructions from memory into registers and controlling the entire system based on the execution results of the instructions.

Arithmetic unit: The arithmetic unit is responsible for calculating the data sent to the arithmetic unit.

Clock: Responsible for sending the clock signal that starts the CPU timing. The CPU can only work under the drive of the clock signal.

How programs are executed by the CPU

When we are developing embedded software, a common language is C language, which is also called high-level language. Before the high-level language we write actually enters the CPU for execution, there are still many steps to complete. A rough division is that it needs to go through three steps: compile -> link -> generate executable files. A more detailed division is the process shown in the figure below:

According to the above flowchart, we can know that before the program enters the CPU for execution, it will get an executable program, and this executable file contains a collection of instructions and data. So the program we write is essentially in the form of instructions + data. Since there are instructions and data that can be recognized by the CPU, the written program can also run in the CPU.

CPU workflow

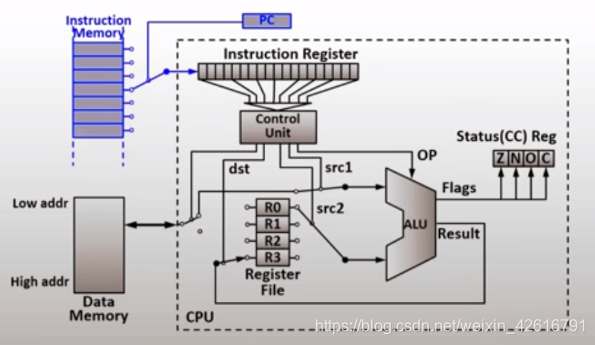

Before explaining in detail how the CPU works, let's first look at a CPU workflow diagram, as shown below:

In the picture shown above, we can see the following information: instruction memory and data memory outside the dotted box, instruction register, control unit, register group, logic operation unit and status register inside the dotted box. Next, we will explain how each of them operates and how they coordinate with each other to complete a program.

Logical operation unit and register group

Let's start with the logical operation unit. As the name suggests, its function is to perform operations. Since it is an operation, it requires operands and instructions, as shown in the following figure:

The OP shown in the above figure represents the operation to be performed by the instruction. It can also be seen from the figure that the operands of the logic operation unit come from the register group. Of course, the operands of the logic operation unit do not always come from the register group. Only when performing simple operations will the operands be obtained from the register group for operation. After the operation, there must be a result, so the logic operation unit will output two data, one is the result after the operation, and the other is the flag bit. The flag bit here represents whether the result of the operation after the two operands are operated is 0, whether there is a carry, whether it is a negative number, or whether there is an overflow.

On the other hand, in addition to providing operands to the logic operation unit, the register group also serves as a storage function for the operation results. The schematic diagram is as follows:

That is to say, in addition to providing operands to the logic operation unit, the register group also stores the operation results of the logic operation unit.

Logic unit and data memory

As mentioned above, when performing simple operations, the logic operation unit will obtain operands from the register group. What should we do when performing complex operations? At this time, the data memory will play its role. The schematic diagram is as follows:

From the above picture, we can see that the operands of the logic operation unit come from the data memory and the register group. When fetching operands from the data memory, it should be noted that the data memory is not part of the CPU, so the speed of accessing the memory is much slower than the speed of accessing the register.

When explaining the register group, we said that the register group can provide operands and can also store the operation results of the logic operation unit. The same is true for the data memory, which can also store the operation results of the logic operation unit. The schematic diagram is as follows:

The register group and the data memory can both store the operation results of the logic operation unit, so what is the difference between the two? The most popular explanation I have heard is: storing the operation results of the logic operation unit in the register group is like when we do math fill-in-the-blank questions in an exam, we will get some intermediate results, that is, these results are not to be filled in the answer on the test paper, but as the conditions for the next step of operation, then we first record this result on the draft paper, this draft paper is equivalent to our register group, when we calculate the final answer, then fill this answer on our test paper, the test paper is equivalent to our data memory here. So, in a word, that is, the register group is used to store intermediate results, and the data memory is used to store the final result.

control unit

We said above that the operand source of the logic operation unit may be the register group or the data memory, and the storage location of the operation result may be the register group or the data memory. So when the actual program is running, which method should be used? At this time, the control unit is needed to coordinate. The schematic diagram is as follows:

From the above picture, we can see that the lines from the control unit downwards point to each switch. The empty circle here represents a switch node, which means where the controller controls the switch to close, thereby determining whether to obtain the operand from the register or the data memory.

Looking at the part above the control unit in the figure, we can see that the data source of the data control unit is the instruction register, so the control unit receives instructions. Then we can summarize the functions of the controller as follows:

Instruction parsing: Analyze what operations the instruction needs to perform

Determine the data flow: determine the source of the operands used by the instruction and the destination of the results

Get Instructions

As mentioned above, the control unit obtains instructions from the instruction register. So where do the instructions in the instruction register come from? Let's go back to the diagram we gave at the beginning:

From the figure, we can see that instructions are obtained from the instruction memory. At the same time, if we want the program to run correctly, we need to make the instructions run in order, rather than sending them to the instruction register randomly. So how can the CPU ensure that the instructions can be run in order? Here we need to use the CPU's PC pointer register. The function of the PC pointer register is to store the address of the next instruction to be executed. After the address is taken out, the PC pointer register will be updated to point to the next instruction to be executed. Therefore, the existence of the PC pointer register ensures the orderly execution of instructions.

Summarize

Above, we have separately explained the components involved in the work of the CPU. Now we will integrate them. The CPU's workflow is to store the address of the next instruction to be executed in the PC pointer register, so that the instructions in the instruction memory can enter the instruction register in order. Then, the control unit obtains the corresponding instruction from the instruction register, parses the instruction, determines the operation to be performed by the current instruction, and controls the source of the logic operation unit operand and the storage location of the logic operation unit operation result according to the content of the instruction analysis, thereby completing the operation required by the instruction to be performed by the CPU.

Previous article:How does a program run in the CPU (Part 2)

Next article:Summary of Assembly Language Phase 1

Recommended ReadingLatest update time:2024-11-22 21:15

- Popular Resources

- Popular amplifiers

-

Siemens PLC Programming Technology and Application Cases (Edited by Liu Zhenquan, Wang Hanzhi, Yang Kun, etc.)

Siemens PLC Programming Technology and Application Cases (Edited by Liu Zhenquan, Wang Hanzhi, Yang Kun, etc.) -

Siemens PLC from Beginner to Mastery with Color Illustrations (Yang Rui)

Siemens PLC from Beginner to Mastery with Color Illustrations (Yang Rui) -

Experience and skills in using Siemens S7-200PLC (Shang Baoxing)

Experience and skills in using Siemens S7-200PLC (Shang Baoxing) -

Siemens S7-1200-PLC Programming and Application Tutorial (3rd Edition) (Edited by Shi Shouyong)

Siemens S7-1200-PLC Programming and Application Tutorial (3rd Edition) (Edited by Shi Shouyong)

- Naxin Micro and Xinxian jointly launched the NS800RT series of real-time control MCUs

- How to learn embedded systems based on ARM platform

- Summary of jffs2_scan_eraseblock issues

- Application of SPCOMM Control in Serial Communication of Delphi7.0

- Using TComm component to realize serial communication in Delphi environment

- Bar chart code for embedded development practices

- Embedded Development Learning (10)

- Embedded Development Learning (8)

- Embedded Development Learning (6)

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Intel promotes AI with multi-dimensional efforts in technology, application, and ecology

- ChinaJoy Qualcomm Snapdragon Theme Pavilion takes you to experience the new changes in digital entertainment in the 5G era

- Infineon's latest generation IGBT technology platform enables precise control of speed and position

- Two test methods for LED lighting life

- Don't Let Lightning Induced Surges Scare You

- Application of brushless motor controller ML4425/4426

- Easy identification of LED power supply quality

- World's first integrated photovoltaic solar system completed in Israel

- Sliding window mean filter for avr microcontroller AD conversion

- What does call mean in the detailed explanation of ABB robot programming instructions?

- STMicroelectronics discloses its 2027-2028 financial model and path to achieve its 2030 goals

- 2024 China Automotive Charging and Battery Swapping Ecosystem Conference held in Taiyuan

- State-owned enterprises team up to invest in solid-state battery giant

- The evolution of electronic and electrical architecture is accelerating

- The first! National Automotive Chip Quality Inspection Center established

- BYD releases self-developed automotive chip using 4nm process, with a running score of up to 1.15 million

- GEODNET launches GEO-PULSE, a car GPS navigation device

- Should Chinese car companies develop their own high-computing chips?

- Infineon and Siemens combine embedded automotive software platform with microcontrollers to provide the necessary functions for next-generation SDVs

- Continental launches invisible biometric sensor display to monitor passengers' vital signs

- [GD32L233C-START Review] - 8. Driving a 1.5-inch OLED screen using ordinary GPIO

- High-speed acquisition module

- What does USB_OTG_FS and USB_OTG_HS mean?

- I2C Master Mode for TI BLE CC2541

- Where can I find the PHI EVM Controller information for the TI ADC acquisition board?

- Loto Practical Tips (8) Application of Loto Oscilloscope in Repairing LED Desk Lamp Dimming Problems

- [NXP Rapid IoT Review] W2-Sensor Data Collection Test

- Today at 10:00 AM, live broadcast with prizes: [Introduction to the Industrial Open Source Platform based on TI Sitara AM5708]

- A complete collection of commonly used electronic components, including graphic symbols/nomenclature/technical parameters

- [15th Anniversary Celebration] Let your strength speak for you, and prove that you are an EEWorlder in one sentence!

Siemens PLC Programming Technology and Application Cases (Edited by Liu Zhenquan, Wang Hanzhi, Yang Kun, etc.)

Siemens PLC Programming Technology and Application Cases (Edited by Liu Zhenquan, Wang Hanzhi, Yang Kun, etc.) Siemens S7-1200-PLC Programming and Application Tutorial (3rd Edition) (Edited by Shi Shouyong)

Siemens S7-1200-PLC Programming and Application Tutorial (3rd Edition) (Edited by Shi Shouyong)

京公网安备 11010802033920号

京公网安备 11010802033920号