1. The difference between LCD and OLED

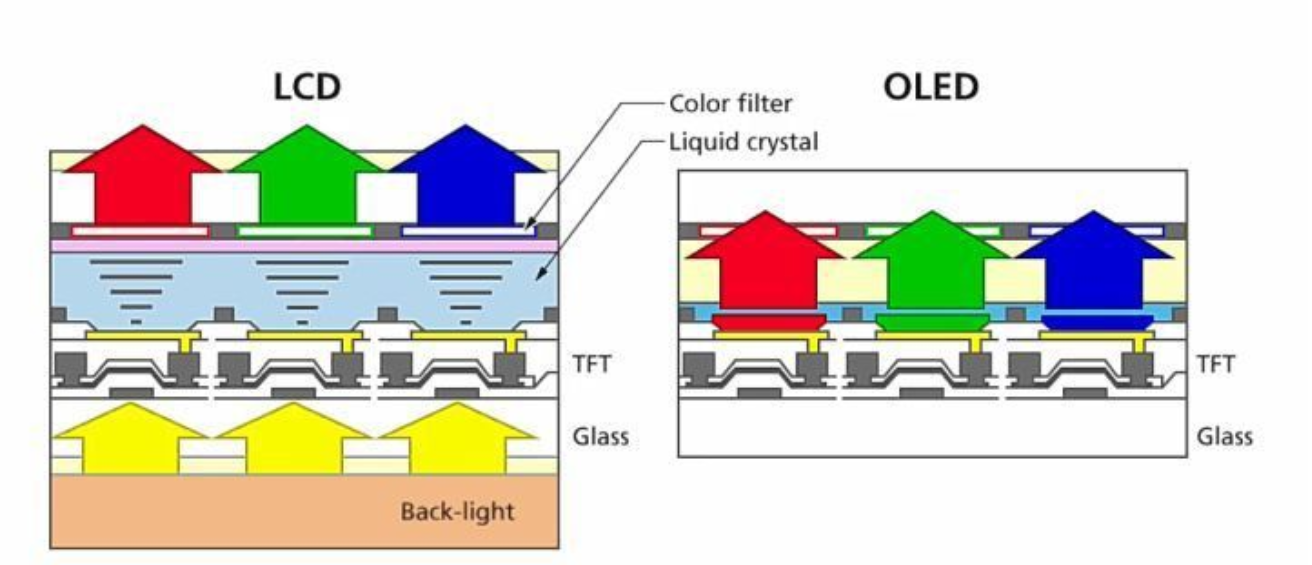

LCD backlight and OLED self-luminescence

LCD is made of inorganic materials, so it has a longer lifespan. OLED has the advantages of wide viewing angle, almost infinite contrast, bendability, and low power consumption.

2. LCD principle

Each point on the screen is called a pixel

Each pixel is composed of three primary colors: RGB.

2.1 How to determine the color?

Consists of three groups of RGB signal lines

From the following schematic diagram, we can see that: R5, G6, B5, that is, RGB565 (color mode, one pixel occupies two bytes)

Therefore, the number of bits per pixel (BBP: bit per pixel) is 2 bytes.

2.2 How does LCD perform “line scanning”?

There is a CLK clock line connected to the LCD. Every time CLK (high or low level) is sent, one pixel is moved.

2.3 How to jump to the next line for "line scanning"?

There is a HSYNC (horizontal synchronization signal) signal line connected to the LCD. Every time a pulse (high or low level) is sent, the line scan jumps to the starting position of the next line.

2.4 How to perform the next “field scan”?

There is a VSYNC (vertical synchronization signal) signal line connected to the LCD, and each time a pulse (high or low level) is sent, it jumps to the origin.

Note: Where does the data on the RGB data line come from?

A video memory (FrameBuffer) is manually allocated in the memory, which stores the data to be displayed. The LCD controller reads the data from it, transmits it to the LCD through three groups of RGB lines, and then displays it on the display screen in sequence.

3. LCD timing

Resolution = Number of Hsyncs * Effective CLK in a row

Complete timing diagram:

Image timing diagram:

The above two pictures can explain the coordination of Hsync and Vsync in LCD control timing (it can be understood that one frame is a vertical synchronization signal and one line is a horizontal synchronization signal)

1. First, there are several rows (Hsync) in a frame (Vsync), set to y, and Vsync sends a frame pulse width Tvp

2. After Tvb time, a frame of data can be sent, starting from the first line

3. Next, there are several clock signals (CLK) in one row (Hsync), which are effectively set to x. Hsync sends a pulse width Thp

4. After Thb time, a line of data can be sent

5. The next horizontal synchronization signal (Hsync) will not be sent until the last pixel in a row has passed Thf time.

6. The next vertical synchronization signal (Vsync) will not be sent until the last line has passed the Tvf time.

From the above, we can know several important signal pins: Hsync, Vsync, CLK, Dn

From the above, we can know several important time parameters: Tvp, Tvb, Thp, Thb, Thf, Tvf

4. LCD controller

Ideas:

1. Get data: tell the LCD controller the address, bpp, and resolution of the FrameBuffer

2. Send data: tell the LCD controller the timing and set the polarity of the pin (this model takes data on the falling edge, but some LCDs take data on the rising edge, so the polarity needs to be set)

4.1 Pixel Data Format

The pixel number format used is as follows: 16BPP

565 data format pin connection diagram:

4.2 Color Palette

1 pixel should be represented by 16 bits in FrameBuffer, but 8 bits can be used to store it in FrameBuffer to save space

8 bits store the index of the color in the palette (a total of 256 16-bit colors)

When the pixel depth is 8pp, the pixel depth is inconsistent with our bandwidth, and our color must be represented by 16 bits. If we use it directly, it is definitely impossible. Then we can choose to use a palette, which stores 256 16bpp colors. At this time, our color is not stored in the real color value, but in the index of the 256 colors in the palette, which corresponds linearly one by one, so we greatly reduce the burden on the system. Whether to use 16bpp or 8bpp depends on the actual situation. 16bpp is definitely clearer than 8pp, but it also brings a heavier load.

Color palette working diagram

5. Programming Framework

Object-Oriented Programming

Parameter layer:

1. Abstract the common parameter structure (for different devices)

2. The upper device structure pointer points to the required parameter structure

Driver layer

1. Abstract LCD controller structures for different platforms

2. The upper layer LCD controller structure pointer points to the required structure

6. Structure parameters

6.1 Pin Polarity Structure

From the above 3. LCD timing, we can know several important signal pins: Hsync, Vsync, CLK, Dn: Hsync, Vsync, CLK, Dn

/* Pin polarity structure

* NORMAL: Normal polarity

* INVERT: Invert polarity

*/

typedef struct pins_polarity{

int vclk; /* normal: get data on falling edge*/

int rgb; /* normal: high level means 1 */

int hsync; /* normal: high pulse */

int vsync; /* normal: high pulse */

}pins_polarity, *p_pins_polarity;

6.2 Timing Structure

From the above 3. LCD timing, we can know several important time parameters: Tvp, Tvb, Thp, Thb, Thf, Tvf

/* Timing structure

* NORMAL: Normal polarity

* INVERT: Invert polarity

*/

typedef struct time_sequence{

/* Vertical direction */

int tvp; /* Vsync pulse width*/

int tvb; /* Vertical Back porch with black frame */

int tvf; /* Bottom black frame Vertical Front porch */

/* horizontal direction*/

int thp; /* Hsync pulse width*/

int thb; /* Left black frame Horizontal Back porch*/

int tvf; /* Horizontal Front porch on the right black frame */

}time_sequence,*p_time_sequence;

6.3 LCD Controller Structure

Contains initialization, enable, and disable functions

/* Abstract LCD controller structure

* Upward: Receive different LCD parameters

* Down: Use these parameters to set the corresponding LCD Controller

*/

typedef struct lcd_controller{

void (*init)(p_lcd_params plcdparams); //initialization

void (*enable)(void); //enable

void (*disable)(void); //disable

}lcd_controller,*p_lcd_controller;

7. Initialize LCD pins

Initial LCD dedicated pins, configure its mode: LCD Data and LCD Control

/* Initialize LCD pins */

void jz2440_pin_init(void)

{

/* Initialize backlight pin: GPB0 */

GPBCON &= ~0x03;

GPBCON |= 0x01; //Output mode

/* Initialize LCD dedicated pins */

GPCCON = 0xAAAAAAAA;

GPDCON = 0xAAAAAAAA;

/* Power pin LCD_PWRDN */

GPGCON |= (3<<8);

}

For the convenience of GPC and GPD, both are set to LCD dedicated pins 0xAAAAAAAA

From the timing sequence of the S3C2440 LCD controller shown below, we can see that when setting the register, we need to -1 on the time parameter.

8. LCD controller initialization

8.1 LCDCON1

/* LCDCON1[17:8] : CLKVAL, vclk = HCLK/[(CLKVAL+1)*2]

* = 100M/[(CLKVAL+1)*2]

* CLKVAL = 100/vclk/2 - 1 , vclk

* [6:5]: 0b11, TFT LCD

* [4:1]: bpp mode

* [0] :LCD video output and the logic enable(1)/disable(0)

*/

int clkval = (double)100/plcdparams->time_seq.vclk/2 - 1 + 0.5;

int bppmode = (plcdparams == 8) ? 0x0B : //8bpp

(plcdparams == 16) ? 0x0C : //16bpp

0x0D; //24bpp

LCDCON1 = (clkval << 8) | (3 << 5) | (bppmode << 1);

8.2 LCDCON2

/* Vertical

* [31:24] :VBPD = Tvb - 1

* [23:14] : LINEVAL = line - 1 line value

* [13:6] :VFPD = Tvf - 1

* [5:0] :VSPW = Tvp -1

*/

LCDCON2 = ((plcdparams->time_seq.tvb -1) << 24) |

((plcdparams->yres -1) << 14) |

((plcdparams->time_seq.tvf -1) << 6 ) |

((plcdparams->time_seq.tvp -1) << 0 );

8.3 LCDCON3

/* level

* [31:19] :HBPD = Thb - 1

* [18:8] : HOZVAL = columns - 1 horizontal pixel

* [7:0] :HFPD = Thf - 1

*/

LCDCON3 = ((plcdparams->time_seq.thb -1) << 19) |

((plcdparams->xres -1) << 8) |

((plcdparams->time_seq.thf -1) << 0 );

8.4 LCDCON4

/* [23:14] :HSPW = thp - 1 line pulse width

*/

LCDCON4 = ((plcdparams->time_seq.thp -1) << 0 );

8.5 LCDCON5

/* Used to set pin polarity, set 16bpp data format, and set the format of pixel storage in memory

* [12] : BPP24BL,This bit determines the order of 24 bpp video memory.

* [11] : FRM565, 1-565

* [10] : INVVCLK, 0 = The video data is fetched at VCLK falling edge

* [9] : Whether HSYNC is inverted

* [8] : Is VSYNC inverted?

* [7] : INVVD, whether rgb is inverted

* [6] : INVVDEN

* [5] : INVPWREN

* [4] : INVLEND

* [3] : PWREN, LCD_PWREN output signal enable/disable

* [2] : ENLEND

* [1] : BSWP

* [0] : HWSWP

*/

pixelformat = plcdparams->pins_pol.bpp == 24 ? (1<<12) : //24bpp

plcdparams->pins_pol.bpp == 16 ? (1) : //16bpp

(1<<1);//8ppp

LCDCON5 = (plcdparams->pins_pol.vclk<<10) |

(plcdparams->pins_pol.hsync<<9) |

(plcdparams->pins_pol.vsync<<8) |

(plcdparams->pins_pol.rgb<<7) |

(plcdparams->pins_pol.de<<6) |

(plcdparams->pins_pol.pwren<<5) |

(1<<11) | pixelformat;

8.6 LCDSADDR

As shown in the figure below: fb_base[30:1] is directly written into LCDSADDR1 register

initial address

End address = start address + x * y * bpp/8

That is: starting address + space occupied by one frame

9. Construct LCD parameter structure

Parameter settings for this 4.3-inch LCD

/* This 4.3-inch LCD parameter structure*/

lcd_params lcd_4_3_params{

.name = "lcd4.3",

.pins_pol = {

vclk = NORMAL, /* normal: get data on falling edge*/

hsync = INVERT, /* normal: high pulse */

vsync = INVERT, /* normal: high pulse */

rgb = NORMAL, /* normal: high level means 1 */

de = NORMAL, /* normal: high level enables data enable */

pwren = NORMAL, /* normal: high level enables power enable */

},

.time_seq = {

/* Vertical direction */

tvp = 10, /* Vsync pulse width*/

tvb = 2, /* Vertical Back porch */

tvf = 2, /* Bottom black frame Vertical Front porch */

/* horizontal direction*/

thp = 41, /* Hsync pulse width*/

thb = 2, /* Left black frame Horizontal Back porch*/

thf = 2, /* Horizontal Front porch on the right side */

vlck = 9,/* MHz */

}.

.xres = 480,

.yres = 272,

.bpp = 16, /* 16bit */

.fb_base,

};

Previous article:Design of embedded temperature control system based on ARM microprocessor

Next article:【ARM bare board】Nand Flash programming

- Popular Resources

- Popular amplifiers

- Learn ARM development(16)

- Learn ARM development(17)

- Learn ARM development(18)

- Embedded system debugging simulation tool

- A small question that has been bothering me recently has finally been solved~~

- Learn ARM development (1)

- Learn ARM development (2)

- Learn ARM development (4)

- Learn ARM development (6)

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

- CGD and Qorvo to jointly revolutionize motor control solutions

- CGD and Qorvo to jointly revolutionize motor control solutions

- Keysight Technologies FieldFox handheld analyzer with VDI spread spectrum module to achieve millimeter wave analysis function

- Infineon's PASCO2V15 XENSIV PAS CO2 5V Sensor Now Available at Mouser for Accurate CO2 Level Measurement

- Advanced gameplay, Harting takes your PCB board connection to a new level!

- Advanced gameplay, Harting takes your PCB board connection to a new level!

- A new chapter in Great Wall Motors R&D: solid-state battery technology leads the future

- Naxin Micro provides full-scenario GaN driver IC solutions

- Interpreting Huawei’s new solid-state battery patent, will it challenge CATL in 2030?

- Are pure electric/plug-in hybrid vehicles going crazy? A Chinese company has launched the world's first -40℃ dischargeable hybrid battery that is not afraid of cold

- EEWorld invites you to dismantle (fifth issue) - Gosund CP5 Pro smart power strip dismantling report

- Is the vibration direction and wave propagation direction similar to the rhythm of the Humen Bridge?

- How to get started with Renesas MCU?

- Shanghai ACM32F070 Development Board Review 1. Unboxing

- Strange crash problem of STM32G series timer TIM7!

- Watch the video to win a JD card | Taixiang's actual test of Shui Ge's secrets [Second issue]

- How to choose MCU in applications running at high temperature

- EEWORLD University Hall ---- 2019UDE on-site report: Appotronics leads laser display to a new peak

- SK Hynix only pays 17 months' salary as year-end bonus, sparking employee dissatisfaction

- Microcontroller Program Outsourcing: Urgently need help to write an MCU to control the RF chip to send and receive

LTC6910-2ITS8#TRM

LTC6910-2ITS8#TRM

京公网安备 11010802033920号

京公网安备 11010802033920号