I2S Audio Bus Learning (Part 3) S3C2440 I2S Controller

1. I2S controller structure diagram

The Inter-IC Sound (IIS) bus interface of the S3C2440A is used as a codec interface to connect external 8/16-bit stereo audio decoder ICs for minidisc and portable applications. The IIS bus interface supports the IIS bus data format and the MSB-justified data format. The interface uses DMA mode to access the FIFO instead of interrupts. It can receive and send data at the same time.

Figure 1 Structure diagram

1. Bus interface, register set and state machine (BRFC): The bus interface logic and FIFO access are controlled by the state machine.

2. 5-bit dual prescaler (IPSR): One prescaler is used as the master clock generator for the IIS bus interface, and the other is used as the external codec clock generator.

3. 64-bit FIFO (TxFIFO and RxFIFO): When sending data, data is written to TxFIFO; when receiving data, data is read from RxFIFO.

4. Master IISCLK Generator (SCLKG): In master mode, the serial bit clock is generated from the master clock.

5. Channel generator and state machine (CHNC): IISCLK and iislrck are generated and controlled by the channel state machine.

6. 15-bit shift register (SFTR): In transmit mode, parallel data is shifted into serial data output, and in receive mode, serial data input is shifted into parallel data.

2. Send and receive mode

1. Normal transmission

The IIS control register has a FIFO ready flag for the transmit/receive FIFO. When the FIFO is ready to send data, if the FIFO is not empty, the FIFO ready flag is set to 1. If the FIFO is empty, the FIFO ready flag is set to 0. When the receive FIFO is not full, the FIFO ready flag for the receive FIFO is set to 1. It indicates that the FIFO is ready to receive data. If the receive FIFO is full, the FIFO ready flag is set to 0. These flags are used to determine the time when the CPU reads and writes the FIFO. In this way, serial data can be sent and received while the CPU is accessing the transmit/receive FIFO.

2.DMA transfer

In this mode, the transmit or receive FIFO is accessible to the DMA controller. DMA service requests in transmit or receive mode are automatically performed by the FIFO ready flag.

3. Send and receive mode

In this mode the IIS bus interface can receive and send data simultaneously.

3. Audio Serial Interface Format

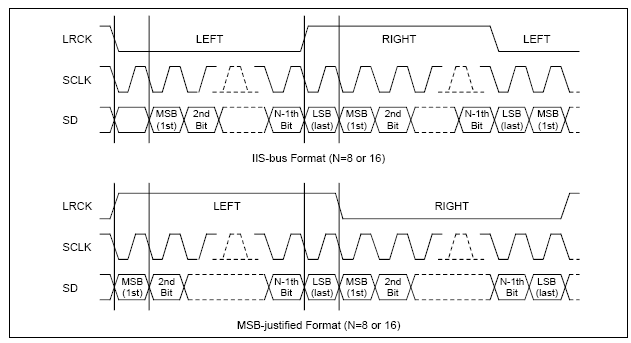

1.IIS bus format

The IIS bus has four wires including serial data input (IISDI), serial data output (IISDO), left and right channel select (IISLRCK) and serial bit clock (IISCLK). The device that generates IISLRCK and IISCLK is the master device. Serial data is sent in 2's complement, with the MSB (Most Significant Bit) first. Because the transmitter and receiver may have different word lengths, the MSB (most significant bit) is sent first. The transmitter does not have to know how many bits the receiver can handle, and the receiver does not have to know how many bits will be received. When the system word length is greater than the generator's word length, the word is truncated (the least significant bit is set to 0) for data transmission. If the receiver receives bits greater than its word length, the bits after the LSB (least significant bit) are ignored. In addition, if the receiver receives less than its word length, the missing bits are set to 0. Therefore, the MSB has a fixed position, while the position of the LSB depends on the word length. As long as the IISLRCK signal changes, the transmitter sends the MSB of the next word within one clock cycle. The serial data sent by the transmitter can be synchronized with the falling edge and the rising edge of the clock signal. However, the serial data must be latched into the receiver on the rising edge of the serial clock signal. Therefore there are some restrictions when synchronous rising edge data is transmitted. The left and right channel select lines indicate which channel is transmitting. IISLRCK can be changed on the falling or rising edge of the serial clock, but it does not need to be symmetrical. At the slave device, the signal is latched on the falling or rising edge of the serial clock. Before the MSB is transmitted, the IISLRCK line changes one clock cycle. This allows the transmitter to derive the synchronous timing for establishing the serial data for transmission. In addition, it enables the receiver to store the previous word and clear the input for reception of the next word.

2.MSB JUSTIFIED format

The MSB JUSTIFIED bus format is similar in structure to the IIS bus format. The only difference from the IIS bus format is that the MSB JUSTIFIED format implements that the transmitter always sends the MSB of the next word as long as IISLRCK changes.

Figure 2 IIS format and MSB JUSTIFIED data format

4. IIS acquisition frequency and main device clock

The I2S master clock frequency can be selected by the sampling frequency. This is because the I2S master clock frequency is generated by the I2S divider (master clock frequency = PCLK/prescaler value). Therefore, the appropriate prescaler value and CODECLK sampling frequency type (256fs or 384fs) must be selected to obtain the appropriate I2SLRCK frequency (I2SLRCK frequency = master clock frequency/CODECLK).

The serial bit sampling frequency type (16/32/48fs) can be completed by configuring the serial bit number of the channel and the CODECLK sampling frequency type (serial bit clock frequency type = CODECLK sampling type/serial data bit number).

5. IIS bus interface special registers

I2S related registers include I2S control register I2SCON, I2S mode register I2SMOD, I2S frequency division register I2SPSR, I2SFCON register and FIFO register.

1) I2SCON control register

The physical address of the I2SCON control register is 0x55000000, which is readable/writable. The value after reset is 0x100. The meaning of each bit of the register is as follows:

[8] Left and right channel flags, 0 = left channel, 1 = right channel;

[7] Send FIFO ready flag, 0 means not ready, 1 means FIFO ready;

[6] Receive FIFO ready flag, 0 means not ready, 1 means FIFO ready;

[5] Send DMA request enable, when it is 0, the request is disabled, and when it is 1, the request is enabled;

[4] Receive DMA request enable, when set to 0, the request is disabled, and when set to 1, the request is enabled;

[3] Send channel idle command. In idle state (suspend transmission), I2SLRCK is inactive. 0 means I2SLRCK is generated, 1 means it is not generated.

[2] Receive channel idle command. In idle state (suspend transmission), I2SLRCK is inactive. 0 means I2SLRCK is generated, 1 means it is not generated.

[1] I2S prescaler enable, when 0 is set, the prescaler is disabled, when 1 is set, the prescaler is enabled;

[0] I2S interface enable. When 0 is set, I2S is disabled. When 1 is set, I2S is enabled.

2) I2SMOD mode register

The physical address of the I2SMOD mode register is 0x55000004, which is readable/writable. The value after reset is 0x000. The meaning of each bit of the register is as follows:

[8] Master-slave mode selection, 0 for master mode, 1 for slave mode;

[7:6] Transmit/receive mode selection, 00 = none, 01 = receive mode, 10 = transmit mode, 11 = transmit/receive mode;

[5] Priority of left and right channels. When the value is 0, the right channel is high and the left channel is low. When the value is 1, the right channel is low and the left channel is high.

[4] Serial interface format, when it is 0, it is I2S compatible format, when it is 1, it is MSB adjustable format;

[3] Each channel serial data bit, 8 bits when 0, 16 bits when 1;

[2] Master clock frequency selection, when it is 0, the master clock is 256fs (sampling frequency), when it is 1, it is 384fs;

[1:0] Serial bit clock frequency selection, 00 = bit clock is 16fs, 01 = bit clock is 32fs, 10 = bit clock is 48fs, 11 = undefined.

3) I2S frequency division register I2SPSR

The physical address of the I2S frequency divider register is 0x55000008, which is readable/writable. The value after reset is 0x000. The meaning of each bit of the register is as follows:

[9:5] A prescaler value, the division factor of prescaler A, I2S bus interface main clock = MCLK/A prescaler factor;

[4:0] B prescaler value, division factor of prescaler B, external CODEC clock = MCKL/B prescaler factor.

4) I2SFCON register

The physical address of the I2SFCON register is 0x5500000C, which is readable/writable. The value after reset is 0x000. The meaning of each bit of the register is as follows:

[15] Transmit FIFO access mode selection, when it is 0, it works in normal mode, when it is 1, it works in DMA mode;

[14] Receive FIFO access mode selection, when it is 0, it works in normal mode, when it is 1, it works in DMA mode;

[13] Control the transmit FIFO enable, set to 1 to enable, set to 0 to disable;

[12] Control the receive FIFO enable, set to 1 to enable, set to 0 to disable;

[11:6] Transmitter FIFO data count, count value 0 to 32;

[5:0] Receiver FIFO data count, count value 0 to 32.

5) FIFO register I2SFIF

The physical address of the FIFO register is 0x55000010, which is readable/writable. The value after reset is 0x000. The meaning of each bit of the register is as follows: The I2S bus interface has two 64-byte FIFOs in the send/receive mode. Each FIFO consists of a table with a width of 16 and a depth of 32, and each FIFO unit can operate the high byte or low byte respectively. The send and receive FIFOs are accessed through the FIFO entry, and the entry address is 0x55000010.

Previous article:IIS of s3c2440 (3) I2S bus protocol

Next article:S3C2440 Study Notes 1.1 Installation of ADS Software

- Popular Resources

- Popular amplifiers

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Download from the Internet--ARM Getting Started Notes

- Learn ARM development(22)

- Learn ARM development(21)

- Learn ARM development(20)

- Learn ARM development(19)

- Learn ARM development(14)

- Learn ARM development(15)

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- 51 drives ST7920 to display custom size characters at any position. I don't know why it flashes when refreshing. Please guide me

- How to flash the customized version of the Saida card machine

- Multitasking in Circuit Python

- Guess the idiom

- CCS variable observer problem

- Creative Collection | The CH246 & CH241 wireless charging kit is ready, what are you going to DIY with it?

- Electromagnetic interference is no small matter, EMI prize survey is launched!

- Compile and run the button routine for the i.MX6ULL development board

- [GD32L233C-START Review] On-chip temperature detection and display

- What should we do when there is a large-scale power outage?

5962-8778001CX

5962-8778001CX

京公网安备 11010802033920号

京公网安备 11010802033920号