Can concurrent engineering (CE) techniques provide a development team using FPGA devices in their projects with a way to quickly and easily find and achieve the most effective balance between processing performance, bill of materials (BOM) cost, and efficiency for the current design? Understanding how concurrent engineering affects a team's design work and how it affects the development team's ability to address the power requirements of the FPGA and the rest of the system from the beginning of the project can help answer this question (refer to the subtitle "Concurrent Engineering").

Concurrent engineering is a mechanism that helps design teams more quickly discover and resolve assumption disconnects between the various disciplines that work together to produce the final design. It is essentially impossible for any development team to get all the requirements of a complex system completely correct at the beginning of the design - so it is more efficient to discover, judge and abandon disconnects in assumptions and design decisions as early as possible, and replace them with conditions and decisions that can guide the project closer to the ideal result at the lowest possible cost.

Are the complexity and potential consequences of FPGA power system design sufficient to justify a concurrent engineering approach in late design stages and worst-case scenarios? To answer this question, we need to understand: What are the sources of design complexity and uncertainty facing FPGA power system designers, and how do these sources affect the trade-off decisions they must make when designing a power supply?

Complexity and uncertainty

Every member of a design team is experiencing increased complexity and uncertainty—fortunately, increasing levels of integration and abstraction can reduce some of this complexity and uncertainty and help keep overall complexity within the range that human designers can understand and cope with. As with any subject that increases its influence late in the design process, upstream design assumptions and decisions can create additional sources of complexity and uncertainty that can be minimized if coordinated and communicated early.

Power supply design is one of these potential downstream subjects in systems that are increasing in complexity. In this example, let's look at the sources of complexity and uncertainty from the perspective of a power supply designer

FPGA voltage requirement trends are driving up complexity as they require an increasing number of power rails. Today’s high-end FPGAs no longer require just two power rails for the core and I/O cells and perhaps a third for auxiliary functions, but require more than ten externally driven power rails.

Why does the number of required power rails increase so dramatically? An SRAM cell may require a slightly higher voltage than the internal logic gates to ensure reliable full-speed operation, while also requiring a lower voltage for standby mode. Industry standards prevent different I/O cells from sharing the same power rail, increasing the number of required power rails because they may lock different I/O cells and physical transceiver interfaces to different supplies with different power supply noise limits and voltage values. For example, Ethernet may operate at a different I/O voltage than the I2C bus. One is an on-board bus and the other is an external bus, but both can be implemented with an FPGA. Reducing jitter or improving the noise margin of sensitive circuits such as low-noise amplifiers, phase-locked loops, transceivers, and precision analog circuits may also increase the need for more power rails because they cannot share the same power rail with higher-noise components, even if they operate at the same voltage.

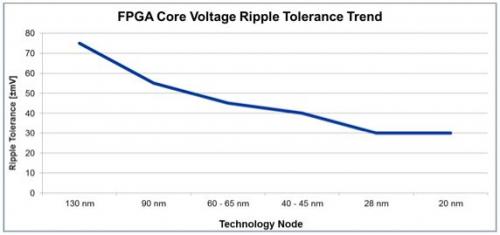

In addition to requiring an increasing number of power rails, today’s FPGAs also operate at lower voltages than previous FPGAs, which helps reduce power consumption and increase integration, but also increases complexity because the power supply must be able to maintain increasingly tight voltage tolerance requirements (see Figure 1). For example, the published tolerance of core voltage ripple in FPGAs based on the 28nm technology node has been reduced by more than half since FPGAs were produced using the 130nm process. The error budget percentage has dropped from 5% to 3% and is moving towards 2%. Maintaining voltage tolerance requirements is related to understanding and meeting the FPGA current requirements.

Figure 1: Over four process technology node generations, average voltage ripple tolerance has dropped by more than half, which is why it’s adding complexity to power designers.

FPGA current signature trends are driving complexity because higher density and the number of peripheral/functional/IP blocks contained in FPGAs is growing at Moore’s Law—roughly doubling the number of blocks in the same silicon footprint every two process node generations. While the voltage supplied to the FPGA is fixed, the operating current at each voltage is not fixed and can fluctuate based on how the FPGA logic is implemented.

When internal logic gate blocks or I/O cells switch between high utilization and low utilization, current fluctuations are extremely severe. As the FPGA switches to a higher processing rate, the current consumption will increase and the voltage will tend to drop. A good power supply design will prevent the voltage drop from exceeding the voltage instantaneous threshold. Similarly, when the FPGA switches to a lower processing rate, the current consumption will decrease and the voltage will tend to increase, and the power supply design should prevent it from exceeding the corresponding threshold. In summary, a lot of uncertainty that can actually affect the power supply design comes from how the FPGA designer implements the system on the FPGA.

This type of uncertainty particularly affects FPGA systems, in part because one of the key features of using FPGAs is that designers can create processing resources of any size and any number of redundant processing resources to solve their problems in a shorter time and/or with lower power than software programmable processors. Thus, while software programmable processors have limited processing resources that can operate simultaneously, FPGAs offer the opportunity to create specialized, optimized, and customized processing resources, albeit with the requirement for customized power supply design.

powered by

Understanding and managing how FPGA designers implement transitions between high and low processing states on the FPGA early in the design cycle will significantly impact the options available to power designers to optimize power design and meet system power requirements. It is not required or necessary to use separate power supplies for each power rail in the FPGA, as this increases cost and takes up too much valuable board space. Instead, power designers can use a distributed power network with buck regulators stepping down the system power and then distributing it to individual point-of-load regulators to provide each voltage rail. Each regulator is designed to provide a constant output voltage, as long as the input voltage and output load current are within the design range.

There are two basic types of regulators: linear and switching. Compared with switching regulators, linear regulators are easier to implement, can provide a more stable output with less noise or voltage ripple, and are less expensive to use and occupy less board area. However, their power conversion efficiency is much lower than that of switching regulators, especially when the input-output voltage difference is large. For example, using a linear regulator to generate 1V from 5V, its conversion efficiency is only 20%, which is much lower than the nearly 85% conversion efficiency of a switching regulator.

Conversion efficiency refers to the ratio of output power to input power. Lower efficiency means that the regulator is consuming power, not the FPGA. Therefore, for FPGA applications with large operating currents, switching regulators are more suitable than linear regulators. The fast I/O node current of some high-end FPGA systems can reach 80A. In addition, the temperature rise caused by wasted power consumption will affect the space required for heat sinks or air convection to maintain the performance of system components. Generally speaking, if there is no air convection, a power dissipation of 1W per square inch of copper will cause a temperature increase of 10°C.

Although switching regulators are much more efficient than linear regulators, they have noise issues, that is, they have larger voltage ripple, which increases the challenge of tightening tolerance thresholds for power supply designers. Proper placement of switching regulator devices on the circuit board is key to minimizing electrical noise, and their slightly larger size increases this challenge.

Therefore, having the right knowledge about the power budget early enough in the design process can help the power supply designer to properly arrange the correct board location and board space to use a more efficient switching regulator, or better yet, use a less efficient linear regulator.

Early planning

Most FPGA power consumption is determined by the FPGA designer's implementation choices in terms of system switching frequency, output load, supply voltage, number of interconnects, percentage of interconnect switches, and logic and interconnect block structure. These choices, in turn, affect the power designer's judgment and trade-offs in system design, which in turn may affect the final system performance.

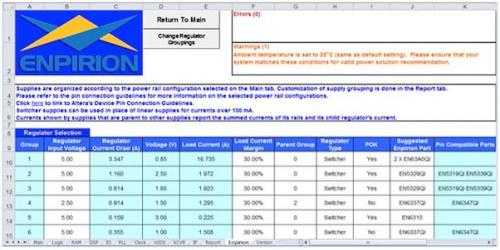

Fortunately, FPGA power designers have a variety of tools and techniques that can be used to analyze power issues early in the design process. For example, most FPGA vendors provide early power estimators and power analyzers to help designers establish power budgets. Designers can use software-based early power estimators—basically glorified or text-based spreadsheets—early in the design process to collect values and assumptions about logic size and operating speed, and then estimate how much power each part of the system will use (see Figure 2).

Figure 2: The worksheets shown in this software-based early power estimator provide suggested components for each power rail based on the planned FPGA usage (Courtesy of Altera).

The early power estimator helps the power designer enter utilization estimates for different subsystems on the FPGA . In the tool example, the worksheets provided in the bottom bar of the snapshot are used to capture power values for each resource type, including logic, memory, various I/O, and hardware signal processing resources. These values can also be used in other worksheets in the tool.

However, simply estimating power is not enough— the power designer needs to design the power tree to support how the FPGA designer intends to use the FPGA . By estimating the total static and dynamic power consumption of the FPGA design, these tools can help the power designer translate the power requirements into an appropriate power tree while ensuring that the design complies with the design team's system trade-off decisions and meets current and voltage requirements. Some tools, including the example shown in Figure 2, may suggest power management devices that will meet the design's needs. Estimators reflect years of experience from FPGA vendors and designers and are useful until numbers based on actual design implementations are available.

As FPGA designs progressed, power designers began using power analysis tools to more accurately understand power consumption and power requirements based on detailed information, such as the netlist output from the FPGA design tool and how the design was implemented in the FPGA.

The purpose of power estimation and analysis tools is to help designers establish early power budget guidelines. With early power estimation, the design team can carry out board design and construction and FPGA design at the same time, which not only saves time, but also forms a more decisive board design once the FPGA design is completed, thus helping the team to complete more efficient testing and optimization.

Power designers need to measure and verify actual FPGA performance during system hardware integration because FPGAs are very sensitive to actual design and environmental operating conditions and may differ from the results of estimation and analysis tools.

About Negotiation

The final disclaimer that estimated and system integration power figures may differ does not give us a lot of confidence. Even using these figures, power designers are still faced with a great deal of uncertainty. We have come full circle to the question of whether FPGA power design is ready for concurrent engineering techniques.

Similar to the examples of how the aerospace and microprocessor teams were able to understand how upstream design decisions impacted downstream design requirements, understanding how power design requirements are impacted by early choices by board and FPGA designers provides a mechanism and opportunity for each team member to begin communicating and negotiating how to optimize the entire system, not just one portion of the system, before costs are fixed into the design.

The primary value of early coordination and communication with every member of the development team from the beginning of the project is to uncover the disconnect between assumptions among different subject matter experts—in this case, the power designer, FPGA designer, and board designer, as well as the designers of other system components that reside on or affect the board, FPGA, and power system—as early in the design process as possible. At this point, the affected group members can discuss, debate, and even argue with each other, ultimately starting and completing the process of finding and negotiating solutions at a lower cost because they need to avoid all the expensive rework and requirement changes in the late design stages.

Being able to selectively use a more efficient switching regulator requires fairly accurate foresight about the system power requirements so that the right amount of board space can be allocated to the power regulator and components in the right locations to meet the power requirements, including the voltage ripple tolerance requirements. A poor or inaccurate power prediction result may mean using a less efficient regulator to meet the voltage ripple requirement, but this "ripple" places additional demands on the rest of the design, such as requiring a larger power supply, needing to dissipate more heat, or even running the FPGA at a slower speed.

One of the key values of power estimation and analysis tools is to get everyone focused on power early. In contemporary designs, FPGAs can be a major factor in system performance and power consumption—and therefore a major consideration in power design. Working with power designers from the beginning of the design process can help discuss system trade-off decisions and how to use FPGAs, and then use tools to get earlier and more accurate power estimates.

Success is not getting all the system requirements correct before you start, but rather identifying and discarding bad decisions as early as possible, and replacing them at the lowest possible cost with decisions that will guide the project closer to the ideal output. The result is that you reap the benefits of earlier, easier, and more accurate power predictions in subsequent projects.

When I worked on some aerospace integrated product team projects (our version of concurrent engineering), we used a variation of the 80-20 rule: 80% of the project cost is determined by the first 20% of the design work. After that, the best you can hope to do is deal with the remaining 20%. When we know the smallest part has the greatest impact on the final cost of the project, we can make decisions efficiently.

This expression may not be completely accurate, but it seems to contain some wisdom. More importantly, it provides a warning and reminder to ask questions before you get stuck on 80% and to work with team members who have experts in different fields as much as possible, so as not to regret it when the project reaches the final development stage.

Previous article:Analysis of isolation and non-isolation of drive power supply

Next article:Design of a high-performance intelligently controlled LED street lamp driver

Recommended ReadingLatest update time:2024-11-25 05:15

- Popular Resources

- Popular amplifiers

- RAQ #223: How to measure and determine soft-start timing without a soft-start equation?

- Vicor high-performance power modules enable the development of low-altitude avionics and EVTOL

- Bourns Launches Two Thick Film Resistor Series with High Power Dissipation Capabilities in Compact TO-220 and DPAK Package Designs

- Bourns Launches New High-Pulse Brake Resistor Series with Superior Energy Dissipation Capabilities

- Nexperia launches new 120 V/4 A half-bridge gate driver to further improve robustness and efficiency in industrial and automotive applications

- Vishay's New 150 V MOSFETs Offer Industry-Leading Power Loss Performance

- The first generation of SGT MOSFET series from Qiangmao: innovative trench technology, automotive-grade 60 VN channel, breakthrough in high-efficiency performance of automotive electronics

- DC/DC Power Supplies for Automotive Applications

- MathWorks and NXP Collaborate to Launch Model-Based Design Toolbox for Battery Management Systems

- Intel promotes AI with multi-dimensional efforts in technology, application, and ecology

- ChinaJoy Qualcomm Snapdragon Theme Pavilion takes you to experience the new changes in digital entertainment in the 5G era

- Infineon's latest generation IGBT technology platform enables precise control of speed and position

- Two test methods for LED lighting life

- Don't Let Lightning Induced Surges Scare You

- Application of brushless motor controller ML4425/4426

- Easy identification of LED power supply quality

- World's first integrated photovoltaic solar system completed in Israel

- Sliding window mean filter for avr microcontroller AD conversion

- What does call mean in the detailed explanation of ABB robot programming instructions?

- CATL releases October battle report

- Battery industry in October 2024: growth momentum remains unabated!

- Mercedes-Benz will launch the eCitaro equipped with NMC4 batteries to provide high energy density and long life

- Many companies have announced progress on solid-state batteries. When will solid-state batteries go into mass production?

- Xsens Sirius Series Inertial Sensors Enable 3D Inertial Navigation in Harsh Environments

- Infineon's Automotive Landscape: From Hardware to Systems

- STMicroelectronics discloses its 2027-2028 financial model and path to achieve its 2030 goals

- 2024 China Automotive Charging and Battery Swapping Ecosystem Conference held in Taiyuan

- State-owned enterprises team up to invest in solid-state battery giant

- The evolution of electronic and electrical architecture is accelerating

- Please help, what kind of sensor is needed to complete this function?

- How does the STM32 interrupt behavior jump to the EXTI9_5_IRQHandler function?

- An Engineer's Guide to EMI - Noise Propagation and Filtering

- How to configure GPIO interrupts for TI C6000?

- TI combines Bluetooth solution with MSP430 microcontroller

- About the DSP/BIOS transplantation of F28335

- A 1Ω resistor and a 1Ω capacitor are connected in series. What percentage of the AC signal is on the capacitor?

- [Xingkong Board Python Programming Learning Main Control Board] Unboxing Experience - A Python Programming Learning Board Worth Playing With

- Detailed explanation of Bluetooth GattCallback usage and BLE data transmission

- TPS5430 negative voltage output -18V ripple 30mvpp, is there any way to make the ripple smaller?

FPGA implementation of FIR filter

FPGA implementation of FIR filter Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号