This paper introduces a 16-channel portable logic analyzer. It samples and caches high-speed data through FPGA, and uses USB control chip and FPCA to control the data through USB interface to send it to the host computer for display. It simplifies the hardware circuit part of the previous logic analyzer, reduces the cost of the logic analyzer and is easy to carry. The design of the hardware circuit part is emphasized.

The logic analyzer is a widely used tool in the process of digital design verification and debugging. It can check whether the digital circuit is working properly and help users find and troubleshoot faults. It can capture and display multiple signals each time, and analyze the time relationship and logical relationship of these signals. According to the differences in hardware device design, the current logic analyzer can be roughly divided into stand-alone and card-type virtual logic analyzers that need to be combined with computers. Stand-alone logic analyzers have excellent performance, but they are expensive and are rarely used by general users. The portable logic analyzer implemented in this project provides corresponding performance at a lower cost. Although the performance has declined, it can fully meet the general logic signal analysis and greatly reduce the cost. The instrument is small in size and easy to carry, which is suitable for ordinary users.

1 Overall system design

This logic analyzer can realize 16-channel logic analysis. The input signal can be an analog signal or a digital signal. It can measure a wide range of input levels and support 1.8-5 V level sampling. The chip CY7C68013A is used as the main control chip. It is connected to the computer through USB 2.0 to transmit data information. FPGA is used to achieve high sampling rate. Each channel supports 12 Mbit.s-1 high-speed sampling. The sampled signals are stored in the memory in sequence. The sampling information is organized in the memory according to the principle of "first in, first out". After receiving the display command, the information is read out one by one in the order of precedence, and the measured value is displayed according to the set display mode. In this way, the required digital waveform can be observed in the software interface, and the trigger mode can be set to display the required waveform.

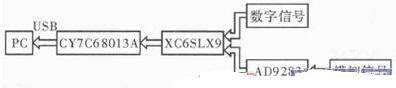

This project uses CY7C68013A as the USB acquisition main control chip, and uses XC6SLX9 as the selection device of the data channel to select whether the data input to CY7C68013A comes from the digital signal or the digital signal after the analog signal passes through the ADC module. Since the logic analyzer is connected to USB, an ESD chip is added to the USB connection port. And add 16 kB of EEPROM on the board as the program memory of CY7C68013A. Figure 1 is the basic block diagram of the logic analyzer. Figure 1 Basic block diagram of the logic analyzer The CY7C68013A chip used in the project is a low-power chip. The core of the chip is an enhanced 51 core, with a 16 kB program data area inside. The main frequency of the chip is 48 MHz, and it meets the 480 Mbit.s-1 high-speed transmission protocol standard, complies with the USB2.0 specification, and is backward compatible with the USB1.1 specification, which can basically meet the data requirements of the project. XC6SLX9 is a Spartan6 series FPGA produced by Xilinx, with 9 152 logic units. The Spartan6 series products are based on the recognized low-power 45 nm, 9-metal copper layer, dual gate oxide process technology, providing advanced power management technology, 150,000 logic units, integrated PCI Express modules, advanced memory support, 250 MHz DSP Slice and 3.125Gbit.s-1 low-power transceiver. The chip selected for this project is a 144-pin packaged chip, and its IO can meet the requirements of high-speed data communication. Adding an ESD chip to the USB connection end can better prevent electrostatic interference, making the logic analyzer safer and more reliable to use. 2 Hardware Circuit Design The system hardware design mainly includes the computer interface part and the data acquisition part. The trigger setting, high-speed data capture and cache control are completed through FPGA. CY7C68013A is used as the USB master chip to complete the communication with the host computer, send data to the computer host computer, and receive the trigger control word and other control information sent back by the host computer, and work with FPGA. The circuit is divided into five modules: USB host module, FPGA slave module, data acquisition module, data cache module, and power supply module. 2.1 USB host control module The USB host control chip model is CY7C68013A-56PVXC, which integrates USB 2.0 transceiver and enhanced 8051 microprocessor. Its applicability, appearance and function are compatible with FX2. It has 16 kB on-chip code/data RAM, 4 programmable BULK/INTERRUPT/ISOCHRONOUS endpoints, 8-bit or 16-bit external data interface, and its programmable interface can be directly connected to most parallel interfaces, the waveform is defined by programmable waveform descriptors and configuration registers, and multiple RDY and CTL outputs are supported. The operating voltage of the chip is 3.3 V, the tolerance voltage is 5 V, and an I2C controller is integrated. The USB host control chip is connected to a 24 MHz crystal oscillator, the PB port receives FIFO data from the FPGA, and the 15th and 16th pins are connected to the D+ and D- of the USB_B type interface to send data to the host computer and receive control information from the host computer. An AT24C64 (EEPROM) is connected to the I2C bus as a USB program memory. The remaining pins are used to read the current state of the FPGA and send trigger information to the FPGA to determine when to read data. 2.2 FPGA slave control module The FPGA uses the Xilinx Spartan-6 series XC6SLX9-4TQ144C, connected to a 100 MHz crystal oscillator. The 16 IO pins set in the chip receive data from the 16-bit three-state bus transceiver of the 74ALVC164245. The three pins of FPGA.VS[2:0] are all pulled high and configured to fast read and write mode, which can increase the sampling rate. In the Spartan-6 series FPGA, the configuration mode pin is M[1:0]. Unlike the Spartan-3 series, there are 3 configuration pins M[2:0]. Here it is configured as "10", that is, the master serial mode. At this time, the INIT_B pin needs to be pulled high to prevent the chip from entering the chip initialization again after the configuration is completed. The DONE pin must also be pulled high. The JTAG interface is configured for downloading programs. The remaining pins are used to connect two 4 MB RAMs to cache the collected data into the RAM first. 2.3 Data Acquisition Module The data acquisition chip uses SN74LVC16245ADGGR, which is a 16-bit three-state bus transceiver. When the OE pin is connected to a high level, the output is in a high impedance state. When OE is low, if the DIR pin is low, the data is transmitted from port B to port A, and when DIR is high, the data is transmitted from port A to port B. In the figure, port B is used to collect external data, and an external 1MΩ resistor is connected to increase the input impedance. Therefore, the DIR and OE pins are connected to pull-up resistors, and the default power-on output from A to B is invalid. 2.4 Data Cache Module The expansion RAM chip uses a 256×16 kbit high-speed asynchronous CMOS static RAM chip IS61LV25616. Directly connecting the three pins nCE, nLB, and nUB to CND can facilitate reading and writing data. The read and write control signals nOE and nWE are connected to the FPGA to control the reading of external acquisition data into the RAM cache or the reading of data and transmitting it to the host computer through the USB control chip. Its control logic is: when nWE is high and nOE is low, data is read from RAM; when nWE is low, data is written to RAM. 2.5 Power supply module The power supply chip selected is the LM1117 series voltage regulator chip, which has 3.3 V and 1.2 V. The power input uses the headphone jack power supply, with an input of 5 V and 1 A. If powered by USB, since the maximum output current of USB is 500 mA, the current may not be enough during high-speed sampling, so an external power supply is selected.

3 Design and Verification of Logic Analyzer

The host computer software of the logic analyzer adopts Saleae Logic1.1.16. After installing the software and driver, the firmware program must be burned into the USB host chip CY7C68013A. Saleae provides an iic file for communication with the Saleae Logic host computer software. The logic code of the FPGA includes the USB cooperative control part, the SRAM cache part, the trigger setting selection part, and the FIFO data acquisition part. After comprehensive compilation, a bit file is generated and burned into the FPGA Flash using Xilinx Impact software. The FPGA can automatically complete the power-on configuration process without downloading. Figure 2 is a test screenshot. It can be seen that the sampling rate and depth can be selected at the upper left end of the software, and the trigger setting can be performed at the left end. After setting, click Start to collect data, and the right end can display detailed measurement information. Figure 2 Software Design Verification Figure 4 Conclusion The designed portable logic analyzer is low-cost and can achieve 16-channel data sampling and trigger setting. It can achieve a maximum sampling rate of 90 MHz for 3 channels, 50 MHz for 6 channels, 30 MHz for 9 channels, and 12 MHz for 16 channels. The software interface is simple and easy to understand, easy to use, and can meet general scientific research and teaching requirements.

Previous article:Signal Source Analyzer Transient Test Application - Frequency Hopping Measurement of Phase-Locked Loop

Next article:Keysight Technologies Launches New Series of Single-Slot PXI Vector Network Analyzers

Recommended ReadingLatest update time:2024-11-16 21:03

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- Keysight Technologies Helps Samsung Electronics Successfully Validate FiRa® 2.0 Safe Distance Measurement Test Case

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- How to implement remote monitoring of wind turbines in wind farms?

- The difference between USART, USI, USCI and eUSCI serial communication modules in MSP430 microcontroller (updated on March 4, 2019)

- Answer questions to win prizes | ADI Technology Express - Industrial Automation Control and Edge Computing

- MSP432P401R MSP432P4xx: Falcon Series

- Motor drive development exchange 2: R&D process of motor drive products

- Polarity of EPWMA pulse

- [TI recommended course] #Live replay: TI mmWave millimeter wave radar application in automobiles#

- Try out the new features

- Sign up as MPS Plus member and win great prizes!

- MSP430F5529 Unified Clock System UCS

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号