The ADRV9002 also provides the user with the ability to fine-tune the PLL loop filter bandwidth. When the PLL loop filter bandwidth is configured to 1200 kHz, the performance shown in Table 3 can be achieved. A larger PLL filter bandwidth can reduce the PLL re-tuning time and ensure that the PLL is fully locked before the dwell time begins. It is recommended that users further evaluate the required phase noise performance in their application to select the most appropriate loop filter bandwidth.

Load frequency hopping tables up to 128 different frequencies using static and dynamic methods

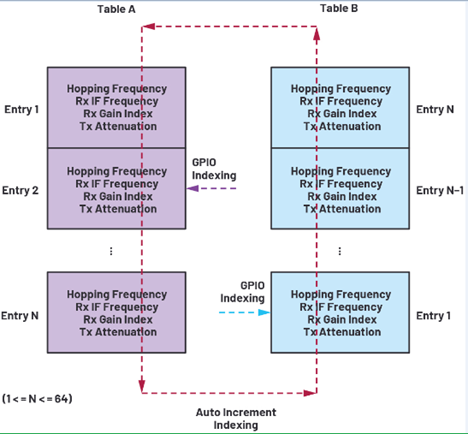

The ADRV9002 uses a frequency hopping table concept for all frequency hopping modes. Each entry in the frequency hopping table contains the frequency and other operating parameters for the hopping frame. The frequency hopping table can be loaded statically, which means that it is loaded during initialization and does not allow for on-the-fly changes thereafter. It can also be loaded dynamically, which is loaded during the execution of frequency hopping; in this case, the user can change the contents of the table on the fly. In addition, a ping-pong-like concept is used so that the user can selectively load two different tables, each containing a minimum of 1 and a maximum of 64 entries. While one table is in use for the current hopping frame, the other table is loaded and ready for the next hopping frame. Each entry informs the ADRV9002 about the configuration of a particular hopping frame. The frequency hopping table can be indexed at any time by auto-incrementing indexing (starting from the first entry of the first table, to the last entry of the second table, and then back to the first entry of the first table in the case of two hopping tables, or continuously looping in the case of one hopping table) or by a specific entry indicated by a digital GPIO.

Figure 7 shows the frequency hopping tables A and B, each containing N entries (1 ≤ N ≤ 64). Each entry in the table contains four important parameters: hopping frequency, intermediate frequency (only for receive IF mode), index to the receive gain table, and transmit attenuation. In TDD operation, the user must inform the ADRV9002 which channel (transmit or receive) is enabled for each hop frame through dedicated channel setup signals (one for each transmit channel and one for each receive channel). Therefore, although each entry in the frequency hopping table contains both receive and transmit parameters, only the relevant parameters are used.

Figure 7. ADRV9002 frequency hopping table contents and indexing method

Before we go further into how to use the frequency hopping table in frequency hopping mode, we need to understand the general communication between the ADRV9002 and the baseband integrated circuit (BBIC).

As shown in Figure 8, BBIC, as the main part of the frequency hopping operation, sets the frequency hopping mode, channel setting signals (Rx1_ENBALE, Rx2_ENABLE, Tx1_ENABLE, and Tx2_ENABLE), HOP signals (HOP1 and HOP2), and static or dynamic frequency hopping tables (including hopping frequency, receive IF frequency, index of receive gain table, and transmit attenuation). BBIC communicates with ADRV9002 through SPI interface or DGPIO. ADRV9002, as a node, receives the signal from BBIC and then configures the data path and LO accordingly for frequency hopping.

Figure 9 shows an example of a dynamic table where only one frequency is loaded into each frequency hopping table A and B. This is an extreme case that allows the user to change the frequency hopping on the fly for each frame. This example uses the PLL multiplexing mode. As shown in Figure 8, the rising and falling edges of the frequency hopping signal define the timing boundaries of the hopping frame, and as mentioned earlier, each hopping frame consists of a transition time and a dwell time. The rising edge of the channel setting signal defines the hopping frame type after a frame delay (this delay is necessary in PLL multiplexing mode).

Figure 8. Approximate block diagram of how the ADRV9002 and BBIC communicate with each other during frequency hopping.

Note that the channel setup signal can represent either a transmit setup signal or a receive setup signal. Figure 9 shows a simplified version of this signal. Since TDD operation involves both transmit and receive, the user needs to configure the transmit setup signal and receive setup signal separately. In addition to indicating the frame hopping type, the channel setup signal can also be used to trigger the BBIC to load the frequency hopping table. The frequency hopping table loading should be completed before the frequency hopping signal edge after the falling edge of the channel setup signal, and then the PLL starts tuning to the frequency on the same frequency hopping signal edge and prepares for the next frame hopping indicated by the next frequency hopping edge. Table A and Table B operate in ping-pong mode, so that after loading, the frequency of one table is used for frequency hopping operation while the frequency of the other table is tuned.

Figure 9. Example of dynamically loading a frequency using the frequency hopping table in PLL multiplexing mode

Figure 10 shows the transmit output frequency vs. time when the frequency hopping table is dynamically loaded with 4 and 8 entries at a time. The transmit input has 4 frames of 0 kHz, –100 kHz, –200 kHz, and –300 kHz frequencies and is fed to the ADRV9002 by continuously looping through these frames. It is perfectly matched and synchronized with the hopping frames, so the 0 kHz input frame corresponds to the 3.1 GHz LO. During frequency hopping, when the LO changes to the next frequency, the transmit input frequency also changes to the next frequency.

When frequency hopping is performed, Table A and Table B are dynamically loaded (for simplicity and ease of observation, the table contents do not change each time they are loaded). For each load of 4 items, four consecutive transmit output frames are seen at the 3.1 GHz output frequency, and then four consecutive transmit output frames are seen at the 3.1004 GHz output frequency, and then this pattern repeats. For each load of 8 items, four consecutive transmit output frames are seen at the 3.1 GHz output frequency, four consecutive frames at the 3.1004 GHz output frequency, four consecutive frames at the 3.1008 Hz output frequency, and four consecutive frames at the 3.1012 GHz output frequency, and then this pattern repeats. The transmit output shown in Figure 8 confirms that the dynamic table loading operation is exactly as expected.

Use dual channels to achieve channel diversity and channel multiplexing

As shown in Figure 2, the ADRV9002 supports dual transmit and receive channels. Frequency hopping can be applied to the two channels to achieve channel diversity or channel multiplexing.

To achieve diversity, both channels are frequency hopping simultaneously using the same PLL (one or two), the same frequency hopping table, and TDD timing configuration. The user can enable the MCS feature provided by the ADRV9002 to ensure that multiple channels on the same or different ADRV9002 devices are fully synchronized with each other to guarantee deterministic latency. Phase synchronization can also be achieved through MCS, but this must be performed each time the PLL re-tunes the frequency. MCS allows synchronization of multiple channels during frequency hopping, making the ADRV9002 a very attractive solution for MIMO diversity applications involving frequency hopping. For more detailed information on the requirements and limitations of using MCS during frequency hopping, refer to the ADRV9001 System Development User Guide. 2

For channel multiplexing, each transmit and receive channel pair uses one PLL to perform frequency hopping independently of each other. One limitation is that very fast frequency hopping (which requires two PLLs for one transmit and receive channel pair) cannot be used to multiplex two pairs of channels in one ADRV9002 device.

In addition to the 2T2R mode, it is also worth mentioning that the ADRV9002 also supports 1T2R and 2T1R frequency hopping operations, thus being able to more flexibly meet the user's specific requirements.

Supports frequency hopping and DPD operation simultaneously

The ADRV9002 also supports DPD operation for both narrowband and wideband applications. It achieves standard-compliant adjacent channel power leakage ratio (ACPR) performance while correcting the nonlinearity of the power amplifier (PA), significantly improving the efficiency of the PA.

An advanced feature of the ADRV9002 is that DPD can be performed in conjunction with frequency hopping. In this case, the ADRV9002 allows the user to configure up to eight frequency regions, and the DPD algorithm creates an optimized solution for each frequency region. For each region, the DPD solution is presented as a set of coefficients that can be stored and loaded at the beginning and end of the transmission, respectively. This ensures that PA linearity is maintained throughout the frequency hopping range.

Since DPD is an adaptive filtering process, a set of samples must be captured periodically for coefficient calculation, so the frame skipping length needs to be long enough to meet the DPD capture length requirement. However, if the user only uses the initially loaded DPD coefficients and does not need to perform DPD updates, there is no such limitation.

Tracking calibration of the ADRV9002 is not typically performed during rapid frequency hopping. However, an initial calibration is performed over multiple frequency regions to achieve optimal performance, depending on the user's frequency hopping configuration.

Frequency Hopping Performance Evaluation Using the ADRV9002 Transceiver Evaluation Software (TES)

Previous article:Native apps, web apps, hybrid apps, and progressive web apps: the best app is the one that suits your needs

Next article:Qualcomm launches next-generation power line communications products to meet growing demand for smart grid communications from vehicle to charging station

Recommended ReadingLatest update time:2024-11-16 16:39

- Popular Resources

- Popular amplifiers

-

New concept analog circuit 1-5

New concept analog circuit 1-5 -

Convex Optimization in Signal Processing and Communications: From Foundations to Applications (Qi Zhongyong, Li Weichang, Lin Jiaxiang)

Convex Optimization in Signal Processing and Communications: From Foundations to Applications (Qi Zhongyong, Li Weichang, Lin Jiaxiang) -

\"New Concept Analog Circuit\" - Transistor [Text Version] (Yang Jianguo)

\"New Concept Analog Circuit\" - Transistor [Text Version] (Yang Jianguo) -

ADI Technical Tutorial Collection - Circuit Simulation and PCB Design

ADI Technical Tutorial Collection - Circuit Simulation and PCB Design

- Wi-Fi 8 specification is on the way: 2.4/5/6GHz triple-band operation

- Three steps to govern hybrid multicloud environments

- Microchip Accelerates Real-Time Edge AI Deployment with NVIDIA Holoscan Platform

- Keysight Technologies FieldFox handheld analyzer with VDI spread spectrum module to achieve millimeter wave analysis function

- Qualcomm launches its first RISC-V architecture programmable connectivity module QCC74xM, supporting Wi-Fi 6 and other protocols

- Microchip Launches Broadest Portfolio of IGBT 7 Power Devices Designed for Sustainable Development, E-Mobility and Data Center Applications

- Infineon Technologies Launches New High-Performance Microcontroller AURIX™ TC4Dx

- Rambus Announces Industry’s First HBM4 Controller IP to Accelerate Next-Generation AI Workloads

- NXP FRDM platform promotes wireless connectivity

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- RISC-V MCU Application Development Series Tutorial CH32V103

- Communication between Yitong Chuanglian MODBUS to PROFIBUS gateway and Honeywell DCS system

- Let's take a look

- 【TI Wireless】Micro Dual-Mode Wireless Receiver

- PWM and PFM

- Let’s talk about whether Huawei can survive in the end.

- Can the network cable be directly soldered to the PCB without a crystal plug or can the network cable be plugged into the circuit board with terminals?

- [Revenge RVB2601 creative application development] helloworld_beginner's guide to debugging methods and processes

- What changes will occur if RFID technology is applied to clothing production?

- EEWORLD University Hall----30 Case Studies of MATLAB Intelligent Algorithms

New concept analog circuit 1-5

New concept analog circuit 1-5 Convex Optimization in Signal Processing and Communications: From Foundations to Applications (Qi Zhongyong, Li Weichang, Lin Jiaxiang)

Convex Optimization in Signal Processing and Communications: From Foundations to Applications (Qi Zhongyong, Li Weichang, Lin Jiaxiang)

京公网安备 11010802033920号

京公网安备 11010802033920号