At present, the Waveform Measurement and Analysis Association has proposed the technical standard IEEE Std.1057 for DAC testing. The terms and test methods in it provide more references for DAC testing. Traditional standard testing is only suitable for test instruments such as signal generators and oscilloscopes, but the test accuracy is not high; large-scale chip testing uses automatic test equipment (ATE), but the cost is very high; recently proposed DAC test methods, such as combining V777 digital test system to perform DAC testing, applying analog filters to perform audio DAC testing, using digital-analog mixed signal test system Quartet to test high-speed DAC, etc. [5], these methods cannot meet the requirements of versatility, accuracy and cost at the same time. In order to meet the above requirements, a high-performance DAC chip loop test method based on FPGA is proposed.

1 DAC main technical parameters

The main technical parameters of DAC can basically be divided into static characteristic parameters and dynamic characteristic parameters. The static characteristic parameters of DAC are used to determine the accuracy of its conversion, mainly including offset error (Offset Error), gain error (Gain Error), integral nonlinear error (INL) and differential nonlinear error (DNL). The dynamic characteristic parameters of DAC are used to determine its performance under AC conditions, mainly including signal-to-noise ratio (SNR), signal-to-noise and distortion ratio (SINAD), effective number of bits (ENOB), total harmonic distortion (THD), and spurious-free dynamic range (SFDR).

2 Test plan

2.1 Design Principles

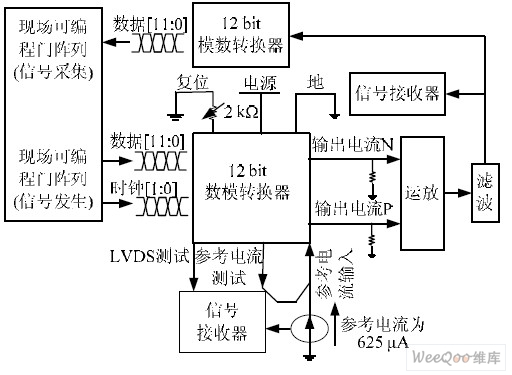

The DAC chip parameter loop test method is to form a complete signal loop with the signal to be tested. First, the signal to be tested is generated by FPGA, which is converted into an analog signal after passing through the DAC chip, and then converted into a digital signal after filtering, amplification circuit and ADC chip, and stored in the RAM of FPGA. Then, the data is taken out using the QuartusII software Signal tap II tool. After importing it into Matlab software, the digital signal can be analyzed and calculated to obtain the technical parameters of DAC [6]. Before ADC sampling, an analog signal receiver, such as an oscilloscope, spectrum analyzer, etc., can be used to compare and analyze with the back-end test results. The design principle is shown in Figure 1.

Since FPGA is very flexible to use, different circuit functions can be generated by configuring different programming data, and parameter tests can be performed on DAC chips with different resolutions and sampling speeds; filtering and operational amplifier circuits reduce the noise of signals during conversion and transmission as much as possible; digital signals are more accurate than analog signals in analysis and calculation, ensuring the accuracy of the test system; compared with other DAC test systems, this test solution uses fewer components and has a lower cost.

Figure 1 Design principle

2.2 Hardware Implementation

The DAC uses a DAC chip with 12-bit resolution and 250 Ms/s sampling speed. The chip adopts key technologies such as LVDS differential circuit, PTAT reference source and 4+4+4 current source array, which can meet the requirements of high-speed and high-resolution conversion circuit processing. The FPGA is the EP3C25Q240C8 chip of the Cyclone III series of Altera Company. It has low power consumption, strong system integration capability and low price. It contains 24* logic units, 594 Kbit memory space and 4 phase-locked loops. The hardware resources can fully meet the test requirements [8]. The ADC is the LTC2242-12 chip of LINEAR Company. It has very good AC characteristics and reduces the error caused by the test system. The operational amplifier is the AD8008 chip of ADI Company. The very good driving characteristics ensure the quality of the output signal of the DAC chip and improve the driving ability of the DAC.

2.3 Software Design

The software code is implemented in the hardware description language Verilog. The signals to be tested generated by FPGA include Test (all zeros, all ones, etc.), Ladder (step wave) and Sin (sine wave). The Test signal is used to test the static characteristic parameters of the DAC chip, the offset error and gain error, the Ladder signal is used to test DNL and INL, and the Sin signal is used to test the dynamic characteristic parameters SNR, SINAD, ENOB, THD and SFDR.

The data analysis and calculation process is mainly realized by Matlab software. The DAC chip inputs all-zero and all-one signals to calculate the offset error and gain error; when using step wave signals to test INL and DNL, in order to test the accuracy, the 12-bit input data is divided into four bits of high, medium and low for testing. The dynamic characteristic parameter test of DAC adopts the fast Fourier transform method. The data taken out by the Signal tap II tool is subjected to FFT and other operations to obtain dynamic characteristic parameters such as SNR, SINAD, ENOB, THD and SFDR, which can fully reflect the dynamic characteristics of DAC, here accurate to the 14th order harmonic.

3 Test Results

Test signal test: The output voltage of the DAC in the all-one input state is 760 mV, and the output voltage in the all-zero input state is 276 uV. After Matlab calculation, the offset error is 0.036% and the gain error is 3.63%.

Ladder signal test: When calculating INL and DNL, the test principle of the four bits of DAC input, high, medium and low is the same. The middle four bits are used as an example. n=12, i changes from 24 to 28 bits, represented by 1LSB, and the 15-step ladder wave output is measured and converted into voltage values. Some data are shown in Table 1. Each column of data represents the order, the minimum test value, the maximum test value, the average test value, the ideal value, and the final voltage value after considering the influence of small current. After using Matlab software to analyze the data, the INL and DNL curves are shown in Figures 2 and 3.

Table 1 15-step wave voltage value

Figure 2 INL analysis curve

Figure 3 DNL analysis curve

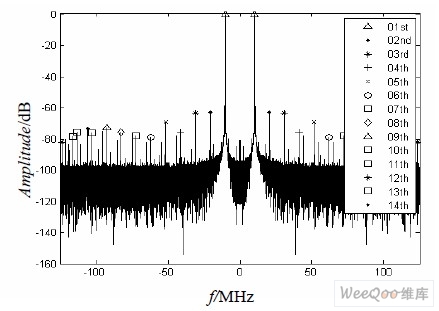

Sin signal test: The input sine wave frequency is 25 kHz, the AD sampling rate is 100 MHz/s, and the output digital signal is analyzed and calculated by Matlab. The measured SNR is 58 dB, SINAD is 57.75 dB, SFDR is 62.84 dB, THD is 58.62 dB, and ENOB is 9.3 bits. The time domain waveform and the spectrum of the 14th order harmonic after FFT transformation are shown in Figures 4 and 5.

Figure 4 Sin signal output time domain waveform

Figure 5 Sin signal output frequency domain waveform

4 Conclusion

Taking a 12-bit, 250 Ms/s DAC chip as an example, the loop test method based on FPGA was used to test its static characteristic parameters and dynamic characteristic parameters. The experimental results show that the static characteristic parameters and dynamic characteristic parameters of the DAC chip can be effectively tested. At the same time, DAC chips with different resolutions and sampling speeds can be tested. The test results are more accurate than those of ordinary analog test instruments, and the test system is less expensive than dedicated DAC automatic test equipment.

Previous article:Design of Partial Response CPM Signal Demodulator Based on FPGA

Next article:Design of IEEE-1394b Bidirectional Data Transmission System Based on FPGA

Recommended ReadingLatest update time:2024-11-16 21:53

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- What is the input voltage of the power chip that steps down the 24V battery to 5V?

- Why can't the segment code LCD screen be lit up when driving with STML152?

- Disassembling Nokia Bluetooth Headset BH501 from over 10 years ago

- Analysis of the types of pads and design standards in PCB design

- The pitfalls encountered when playing with TMS320F28379D

- Why should the power supply be set to +3.3V?

- Analysis of the composition and working principle of the radio frequency identification system

- Add RTT log output to common projects. Simple configuration. It is very easy to use.

- Arduino Bluetooth Obstacle Avoidance Car

- AC Current Sensor = AC Current Transducer = AC Current Transducer

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号