Buttons are often used in digital circuit design. The bouncing phenomenon of buttons is an objective problem in digital system design. Buttons are mechanical contacts, and jitter will occur when the contact point is open or closed. In order to make each button respond only once, the jitter must be removed. This article analyzes the jitter signal of the button and completes the design of the jitter elimination circuit module by means of a counter. The module is applied to the system of button-controlled LCD display, and the system is implemented on the Virtex-4 MB system experiment board represented by Memec. The effect of the de-jitter circuit is good, and the button-controlled LCD display result is normal.

The key switch is one of the main components of human-computer interaction in electronic devices. Most keys are mechanical switch structures. Since the core component of the mechanical switch is an elastic metal reed, the contact point will bounce back and forth at the moment of switching. For circuits with relatively high sensitivity, the signal jitter caused by this bouncing phenomenon will cause false operation and affect the correctness of the system. Therefore, we need to design a key bounce elimination circuit to remove the jitter.

1. Principle and function of bounce elimination circuit

The typical connection of a push button switch is divided into low-level valid and high-level valid. The one in this article is low-level valid.

There are three types of jitter in mechanical switches: jitter when pressed and jitter when released; jitter when pressed and no jitter when released; no jitter when pressed and jitter when released. The jitter waveform, jitter frequency, and jitter time of a mechanical switch are all random, and jitter does not occur every time.

The maximum jitter time of different switches is also different. The length of the jitter time is related to the mechanical switch characteristics, generally 5ms to 10ms. However, the jitter time of some switches is as long as 20ms or even longer. Therefore, in the specific design, specific analysis should be made and the design should be adjusted according to the actual situation.

The bounce phenomenon and bounce elimination are shown in Figure 1. Although the key is only pressed once and then released, multiple segment pulses appear after the key signal stabilizes. If such a signal is directly sent to a timing circuit such as a counter, it may result in a false operation of counting more than once, thus mistakenly thinking that the keyboard has been pressed multiple times. Therefore, a bounce elimination circuit must be added to remove short pulses and avoid erroneous operations.

[page]

[page]

2. Implementation of the button bounce elimination module

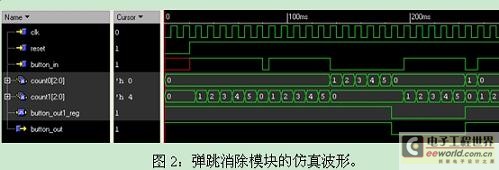

In order to make the key bounce elimination module more concise and portable, a counter is used here to implement the function of eliminating key jitter.

2.1 Calculation of counter modulus value

Determining the counter modulus value is the key issue in eliminating key bounce. If the value is too large, that is, the sampling time is too long, the correct signal will be missed; if the value is too small, the sampling time is too short, the burr will be mistaken for the input signal.

The module value n of the counter is determined by the pulse width of the jitter signal and the period of the sampling signal clk. Since the speed of a general person pressing a key is less than 10Hz (less than 10 times per second), the key press time is greater than 100ms. Calculated at a duty cycle of 50%, the pressing time is greater than 50ms. According to this convention, we believe that the pressing time less than 50ms is a jitter signal, and the pressing time greater than 50ms is a key signal. That is, n=50ms/sampling pulse signal period, so the jitter signal with a pressing time less than 50ms can be filtered out.

Here, the actual required modulus is determined based on the system clock provided by the experimental board. The system clock provided by the experimental board is 100mHz, and a 25mHz clock is obtained by frequency division. The modulus of count obtained by 50ms*25mHz is 21'h1312D0. The debounce time obtained by using this modulus is about 50ms, which meets the requirements.

2.2 Programming

Design a high pulse counter count1 and a low pulse counter conut0. Introduce a sampling pulse signal clk, sample the input signal button_in, and count clk. If button_in is high, count1 counts up until all bits of count1 are 1, stops counting, returns to zero, and makes the output signal button_out output 1 after debounce. If button_in is low, count0 counts up until all bits of count0 are 1, stops counting, returns to zero, and makes the output signal button_out output 0 after debounce.

Some of the procedures are as follows:

[page]

[page]

3 Practical application of the key bounce elimination module

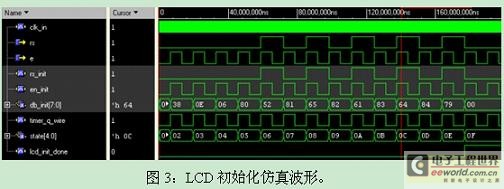

Using the Memec virtex-4 development board, the 8-bit 01 control code is input through the button on the development board, and the state control bit is input with the switch on the development board, thereby controlling the display mode and content of the 1602 C-type character LCD module on the board.

LCD control signal generation module: Generates an 8-bit control signal for controlling the display module based on the button input. The 1-bit (0/1) signal sent to the module by the button is saved and converted so that every 8 inputs form an 8-bit signal. If the input is less than 8 bits or needs to be re-entered, the last result is cancelled; if the input result is determined to be correct, the 8-bit signal is saved and output.

LCD display control module: completes the initialization of the 1602 C-type character LCD module and completes the state conversion according to the control signal.

The overall system design is shown in Figure 4:

Conclusion

This paper conducts modular design and realizes the specific functions of the system composed of bounce elimination circuit module, LCD control signal generation module and LCD display control module, which runs well on the Memec experimental board. And when debugging the circuit with FPGA, the system can be embedded in other circuits to add the required test points and observation points. By controlling the display through buttons, the circuit can be tested dynamically to find out the problems, making the debugging more intuitive, thereby improving the observability of the internal signals of FPGA and improving the verification efficiency.

Previous article:Design of Sine Signal Generator Based on FPGA and DDS Technology

Next article:Design and Implementation of Digital Video Conversion Interface Based on FPGA

Recommended ReadingLatest update time:2024-11-16 16:35

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- SERDES interface circuit design

- TMS320C55x DSP Library

- Antenna Basics and Introduction to 40+ Antennas

- Brief analysis: RF power meter principle, classification, index and application

- How much do you know about the advantages of Wi-Fi 6 and 6E?

- [RVB2601 Creative Application Development] 4. RVB2601 Key Test (with Anti-shake Processing)

- DSP system design issues

- Zhongke Bluexun [RT-Thread RISC-V Evaluation Board] DS18B20 Temperature Measurement

- [2022 Digi-Key Innovation Design Competition] - Intelligent Electronic Weighing System

- Open source vacuum cleaner CircuitRoomba

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号