1 Introduction

Data acquisition systems often require asynchronous serial data transmission. The widely used RS232 asynchronous serial interface, such as 8250, NS16450 and other dedicated integrated devices, is simple to use, but has disadvantages such as occupying circuit board area and complex wiring. System on Chip (SoC) is a design method that integrates software and hardware with embedded systems as the core and IP reuse technology as the basis. Using IP reuse technology to integrate UART into FPGA devices can increase system reliability and reduce PCB board area; secondly, due to the characteristics of IP cores, using IP cores can make the entire system more flexible, and can also achieve functional upgrades, expansions and reductions as needed. Here, the UART module is written in VHDL language, integrated into the FPGA, and constitutes a system on chip SoC with other functional modules of the device.

2 Design and implementation of asynchronous serial port module

2.1 UART Structure

Figure 1 shows a complete UART interface, including a transmit module (txmit) consisting of a transmit latch, a transmit shift register, and logic control, and a receive module (rxcver) consisting of a receive latch, a receive shift register, and logic control. In addition to sharing a reset signal, a clock signal, and parallel data lines, the transmit module and the receive module each have input and output and a logic control unit.

2.2 UART frame format

Figure 2 shows the frame format of UART. The frame format includes line idle state (idie, high level), start bit (start bit, low level), 5 to 8 data bits (databit), check bit (parity bit, optional) and stop bit (stop bit, the number of bits can be 1, 1.5, 2 bits). This format uses the start bit and stop bit to achieve character synchronization. UART generally has a configuration register inside, which can configure the number of data bits (5 to 8 bits), whether there is a check bit and the type of check, the number of stop bits, etc.

2.3 Baud rate clock control

Since the baud rates of the digital interface, working mode selection, and real-time monitoring interface are all different, the UART core contains a programmable baud rate generator that can flexibly configure the baud rate. The baud rate generator provides the reference clock for sending and receiving data to the sending module and the receiving module. The clock mclkx16 generated by the baud rate generator is 16 times the serial data baud rate. It divides the system clock n, n = system clock / baud rate × 16. Setting the corresponding value for different baud rates can get the desired baud rate clock. [page]

2.4 Sending module design

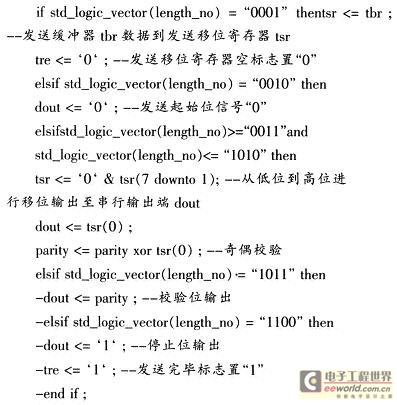

The transmission module is divided into three modes: idle, loading data, and shifting. As shown in Figure 3. When the parallel 8-bit data is written from the bus to the transmission module, the transmission module loads the parallel data into the latch thr, and then shifts the data in the shift register tsr to generate a complete transmission sequence (including start bit, data bit, parity bit and stop bit), which is sent from tx at the corresponding baud rate. The input clock mclkx16 of the transmission module is 16 times the baud rate of the serial data. The module divides it by 16 to get the baud rate clock txclk.

The VHDL program of the sending module is as follows:

2.5 Receiving module design

The receiving module is also divided into three modes: idle, start bit detection, and shift. As shown in Figure 4. First, the start bit is captured, and the start bit of the data input from the rx end is continuously detected under the mclkx16 clock. When the start bit is detected, the receiving module switches from the idle mode to the shift mode, and the 16-divided mclkx16 generates the rxclk baud rate clock. At this time, the rising edge of the rxclk clock is in the middle of each bit of the serial data, so that the following data is sampled at the midpoint of each bit. Then the rxclk controls the data bit to be written into the rsr[7] bit of the shift register rgr at the rising edge, and the rsr is shifted right by 1 bit, and all 8 bits of data are written to the rsr in sequence, and the generation of the rxclk baud rate clock is stopped. After judging that the parity check, frame structure and overflow flag are correct, the data in the rsr register is written into the rhr data latch register, and finally the converted data is output by the 8-bit data bus.

The VHDL program of the receiving module is as follows:

[page]

[page]

3 Hardware Circuit Design

After the UART IP core design is completed, it needs to be embedded in the FPGA system to run. The system uses Xilinx's Spartan-IIE XC2S50 FPGA and its matching EPROM XC18V01, as shown in Figure 5. The system has realized the functions required by the design and realized the verification of the IP core.

4 Results Analysis

After the program is verified by simulation, the IP core must be synthesized and embedded in the FPGA. The Xilinx ISE tool of Xilinx is used to synthesize the UART module. The FPGA uses the Spartan-IIE XC2S50 of Xilinx and the system clock is 40 MHz. After Xil-inx ISE, the resource usage results are shown in Table 1. It shows that the UART core can be generated by using a small number of FPGA slices and LUT units, saving resources. The UART core can be flexibly divided into two parts, receiving and sending, and can be used as needed. Save system resources; some control flag words can also be deleted and expanded as needed. Finally, the FPGA data acquisition system integrated with the UART core is used for asynchronous serial communication experiments with the test bench. The detection of communication data shows that the data transmission using the UART core is stable and reliable.

5 Conclusion

Data acquisition systems often use UART asynchronous serial communication interfaces as short-distance serial communication for the system. Compared with traditional UART devices, integrating IP cores with UART functions into FPGAs is more conducive to improving the reliability and stability of data acquisition systems and reducing circuit board area. The UART IP core designed in this system has been verified by simulation, and after synthesis, compilation, and embedding into FPGA, the system communication has been successfully realized.

Previous article:Multi-core processor SoC design for embedded system applications

Next article:Reducing CPLD Power Consumption in Embedded Design

Recommended ReadingLatest update time:2024-11-17 01:48

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- Rambus Launches Industry's First HBM 4 Controller IP: What Are the Technical Details Behind It?

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- [Open Source] GPIO Experiment Tutorial - Crazy Shell ARM Dual Processor Development Board Series

- Does the embedded industry strictly restrict college education?

- BAW filters help 5G achieve high-quality communications and higher efficiency

- [RISC-V MCU CH32V103 Review] Hardware IIC drive OLED (finally)

- 2 mistakes in the RSL10 official getting started guide

- ADC10 multi-channel input of msp430g2553

- 【TI Recommended Course】#Texas Instruments Field Transmitter Output Interface/Fieldbus Solution#

- 【CH579M-R1】+Love for CH579M

- Module Design and FPGA Verification of 64-bit MIPS Microprocessor

- MSP430 MCU Example 10-8-bit Digital Tube Display Clock

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号