1 System Function Requirements

The main function of the power quality monitoring terminal is to monitor and analyze the power quality of the power grid (three-phase voltage and current) in real time. The main monitoring quantities include: voltage and current effective value, active and reactive power, voltage frequency, three-phase imbalance, harmonic voltage and current content, power factor, phase shift power factor, voltage fluctuation, long-term and short-term flicker.

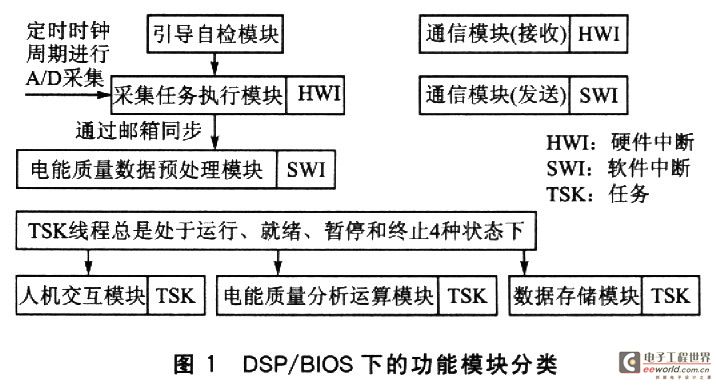

The system uses TI's high-performance DSP chip TMS320F2812 as the processing core, and its processing speed of 150 MIPS is sufficient to meet the real-time requirements of this system. According to the system requirements, this system is divided into the following functional modules: boot self-test module, acquisition task execution module, power quality data preprocessing module, power quality analysis and calculation module, data storage module, communication module, and human-computer interaction module. According to the traditional programming method, these functional modules will be organized together in a sequential structure, and the calls and switches between modules are completed by the code of each module itself, so that the modules of the application are in a coupled state. If you want to add a new functional module or modify an existing functional module, not only do you need to modify the call code of the related module, but the new module will also significantly affect the time response characteristics of the original system, making it quite troublesome to upgrade and maintain. The emergence of DSP/ BIOS provides another mechanism for organizing the functional modules of the application. It regards each functional module as a task thread, and through configurable kernel services, each task thread can time-share CPU resources according to the priority level under the arrangement of the system scheduler, and coordinate between each task thread through synchronization, communication, data exchange, etc. This mechanism improves the maintainability of the application and provides more convenient and advanced debugging methods.According to the above characteristics, this system uses DSP/BIOS as the real-time kernel and designs the entire system based on it.

Figure 1 shows the functional module classification of the system under DSP/BIOS.

2 Software Design Based on DSP/BIOS

2.1 Execution Thread Planning

During the real-time operation of the system, some functional functions are driven by external control signals or run at a predetermined cycle. Therefore, the driving method and execution cycle of the function are very important for the real-time system. DSP/BIOS supports multi-threaded applications, and threads can be defined as different priorities. High-priority threads can interrupt low-priority threads, and different threads can interact with each other, such as blocking, communication, and synchronization. Threads are divided into the following four types (priority from high to low): hardware interrupt (HWI), software interrupt (SWI), task (TSK), background thread (IDL). According to the functional requirements of the power quality monitoring terminal system, the sub-functional modules of the system are divided into the above four types of threads.

First, arrange the hardware interrupt thread (HWI). In general, the main program code of the system is placed in the software interrupt or task; however, the program code of the functional module that is closely related to the external device and has high real-time requirements must be placed in the hardware interrupt. According to the above requirements, this system sets the following sub-functional modules as hardware interrupt threads: A/D acquisition task module and communication module (receiving). A/D acquisition is an important foundation of this system and is closely connected with the underlying hardware of the system, so it is set as a hardware interrupt thread (HWI). Its main process is: the A/D chip collects real-time data of the power grid at a certain frequency, and then communicates with the McPSP port of the DSP. The DSP receives the data collected by the A/D chip and stores it in a specific area of the on-chip RAM to prepare for the operation of other threads. The communication module uses RS485 to communicate with the host computer, which is closely related to the underlying hardware of the system, and the SCI interface of the DSP itself has only a maximum FIFO of 16 words. If the received data is not processed in time, data loss will occur.

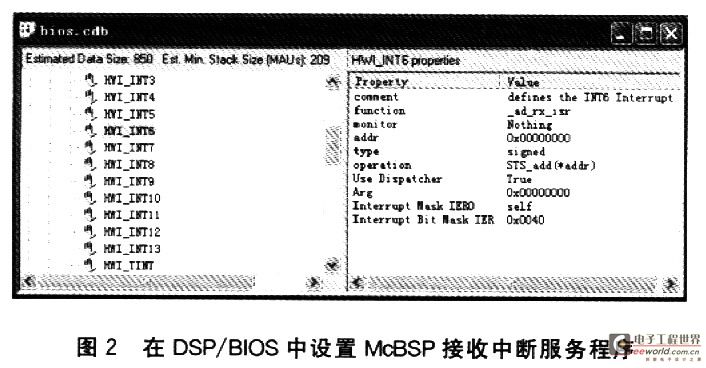

The following describes the parameter settings of the HWI module in DSP/BIOS. The receive interrupt of the McBSP serial port is placed at the HWI_INT6 position of the HWI module, and the ISR function ad_rx_isr() of the receive interrupt is filled in the function call item of the HWI_INT6 interrupt; at the same time, the HWI scheduling function of DSP/RI-OS is selected to use. When responding to the McBSP serial port receive interrupt, the system will automatically call the ad_rx_isr() function. The McBSP serial port receive interrupt setting is shown in Figure 2. Similar to the McBSP serial port receive interrupt setting, the SCIA receive interrupt is set as a communication receive interrupt, and its ISR function scia_rx_isr() is filled in the function call item of the HWI_INT9 interrupt. When responding to the receive interrupt, the system calls the scia_rx_isr() function for processing. The CLK thread is also one of the HWI hardware interrupt threads. It provides a time base for the operation of the entire system, provides a method for users to call functions periodically, and provides a time reference for some code evaluation tools. The CLK module is completely dependent on the DSP's timer interrupt. TMS320C2812 provides two timers for DSP/BIOS.

Secondly, arrange the software interrupt thread (SWI). All software interrupts are started through the API call of the DSP/BIOS kernel. For the convenience of control, the system sets a 16-bit mailbox for each SWI object. The value of this mailbox can be used to conditionally start the corresponding software interrupt. Sub-function modules that are more important and occur more frequently than ordinary tasks can be arranged in the software interrupt thread (SWI). Its sub-function modules include: power quality data preprocessing module and communication module (sending). The power quality data preprocessing module mainly completes the subsequent processing of the A/D conversion results. It is necessary to preprocess the A/D conversion results. Because the A/D chip uses a fixed frequency for acquisition, but the frequency fo of the power grid is fluctuating, directly performing FFT operation on the acquired data will produce spectrum leakage. Therefore, the acquired data must be preprocessed. For example, a 1024-point FFT operation is performed on 4 cycles with 256 points per cycle, a total of 1024 data. Assuming that the average frequency of the four cycles is f, the frequency resolution is f/4, and the FFT operation results are f/4, 2f/4, 3f/4, f, 5f/4... frequency intensity. Therefore, when the grid frequency fo changes, the grid data frequency f for FFT operation must also change accordingly, so that the grid data frequency f before FFT operation is always consistent with the current grid frequency fo. The specific operation of the power quality data preprocessing module is to interpolate the data after A/D conversion, and the interpolation algorithm adopts linear interpolation. After verification, the error of FFT operation caused by the linear interpolation algorithm is within 0.1‰ under rated voltage. In addition, the module also has a function to calculate the effective value of voltage within a cycle. This is necessary data for calculating voltage fluctuations and long-term and short-term flickers. The communication module (transmission) is responsible for sending data to the upper computer. Although its real-time requirements are not high, it is closely related to the hardware bottom layer, so it is set as a software interrupt thread. When the serial port receive interrupt occurs, the scia_rx_isr() function is called to process the receive data command and send the corresponding power quality data according to the relevant command. DSP/BIOS provides software interrupt objects with priorities ranging from 0 to 14. According to the importance of the above threads, the priority of the acquisition data processing thread is set to 14, the host communication thread is set to 8, and other priorities are reserved for future software upgrades.

It should be noted that interrupt threads (including hardware interrupts and software interrupts) all run on the same stack. When a high-priority interrupt occurs and causes the system to switch tasks, the high-priority interrupt thread will interrupt the low-priority interrupt thread; before running the high-priority interrupt thread, the contents of the relevant registers of the low-priority interrupt thread will be saved. After the high-priority interrupt thread ends, the registers will be restored to their original contents and continue to complete the original low-priority thread. Therefore, if too many hardware interrupts or software interrupt threads are set, the stack will overflow. For this reason, most task modules must be placed in the task thread. Next, arrange the task thread (TSK). Like most real-time systems, the task thread is the main component of the entire system. The functions in the task thread can run independently or in parallel. The DSP/BIOS task management module arranges the operation according to the priority of the task thread and completes the conversion from one task to another through the switching function. Each task has four execution states: run, ready, blocked, and terminated. Once a task is created, it is always in one of the four states. DSP/BIOS provides each task object with a priority of -1 to 15. Tasks will be executed in strict priority order, and tasks of the same priority will be arranged in the order of execution according to the principle of "first come, first served". It should be noted that when a task thread is created, a dedicated stack belonging to the task needs to be established at the same time. The stack is used to store local variables or further function call nesting.

We set the power quality analysis operation module, data storage module, and human-computer interaction module in the task thread (TSK). The power quality analysis operation module can be divided into three parts: harmonic calculation task thread, voltage fluctuation calculation task thread, and flicker calculation task thread. The harmonic calculation task thread is mainly responsible for performing FFT operation on the results of power quality data preprocessing. FFT operation mainly includes five parts: bit conversion operation, windowing operation, butterfly operation based on 2, split base operation, and square sum operation. The voltage fluctuation calculation task thread is responsible for recording the fluctuation of grid voltage within 3 minutes. The power quality data preprocessing module has obtained the effective value of voltage for each cycle. In this way, it is only necessary to record the maximum and minimum effective values of voltage within 3 minutes, and the difference between the two is the voltage fluctuation. The flicker calculation task thread includes calculating short-term flicker and long-term flicker. At present, the IEC flicker meter design method is generally adopted. The input adaptation self-test signal is finally obtained through four processes: square demodulator, bandpass weighted filter, square first-order low-pass filter, and online statistical evaluation; but this method is complex and time-consuming. By simplifying the algorithm, a simple and feasible calculation method is obtained: FFT calculation is performed on the voltage effective value of 256 consecutive cycles, and the result can be obtained after a series of weighted calculations to obtain the flicker value of 12.8s. The flicker value within 10min can be obtained through related calculations to obtain short-term flicker, and 12 consecutive short-term flickers (within 2 hours) can be calculated to obtain long-term flicker. After verification, this algorithm is within 1‰ compared with the IEC flicker meter algorithm.

The data storage module is also placed in the task thread, and its process is to store the power quality analysis results, voltage fluctuations and flicker values in FIash. The human-computer interaction module includes two parts: keyboard detection task and LCD display task. The keyboard detection task thread can be completed through the periodic function PRD. PRD can determine the function running time based on the real-time clock. Here, the keyboard detection task is set to run once every 100ms to detect the key press. According to the key press situation, the LCD display task displays the current latest power quality data.

Finally, there is the background thread (IDL). The background thread (IDL) has the lowest priority. Generally, the real-time analysis module (TRA) is placed in it to run, which can interact and diagnose the DSP application in real time during the execution of the application. CCS has real-time analysis tools such as CPU load diagram, execution diagram, host channel control, information recording, statistical observation, real-time control board and kernel/object observation. This series of functional modules can be placed in the IDL thread. Through these tools, the operation status of the entire DSP system will be clear at a glance.

2.2 Communication and synchronization between threads

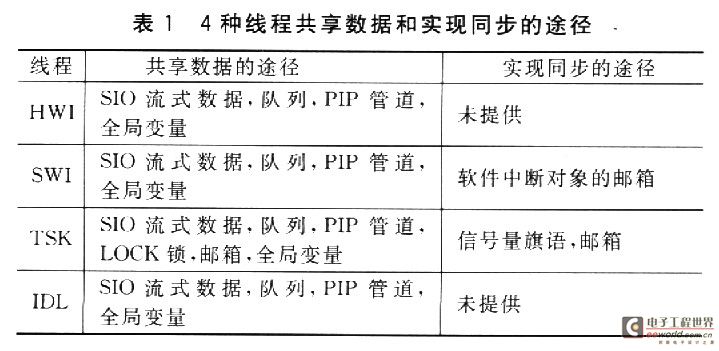

In this multi-threaded system, access to shared resources requires mutual coordination between threads.

There are three communication modes in the DSP/BIOS environment, namely, communication based on pipe (PIPE), communication based on stream (SIO) channel, and communication based on host (HST) channel.

Table 1 shows four ways for threads to share data and achieve synchronization.

In this system, data pipes are used to manage data exchange between threads because they are suitable for high-speed real-time or large-volume data exchange. Each data pipe object retains a cache and divides the cache into fixed-length frames of certain data. All I/O operations through the data pipe process one frame at a time. The synchronization between multiple threads mainly uses the mailbox method.

3 System real-time analysis and debugging

The overhead of the DSP/BIOS kernel itself will affect the real-time performance of the system program, so the DSP/BIOS kernel needs to be optimized. The DSP/BIOS analysis tool provided in CCS can be used to determine the overhead of DSP/BIOS and the amount of computation of the entire application system. For example, the CPU load graph in the real-time analysis tool provided by DSP/BIOS is one of the commonly used tools.

In the final integration stage, due to real-time interaction and other reasons, some errors or untimely responses often occur. Generally speaking, these phenomena are difficult to find and track because they are non-periodic and occur very infrequently. However, since the RTA module in DSP/BIOS is embedded in its kernel, combined with the customized detection vectors provided by the developer, it provides unique visibility into the root cause of the error. This visualization function greatly helps isolate and correct errors, which is not available in general embedded development systems.

The execution performance of applications in the entire system can be improved from the following four aspects: carefully select the type of thread for different program functions; place the system stack in on-chip memory; reduce the frequency of clock interrupts; and increase the size of the streaming input and output buffers.

4 Conclusion

DSP/BIOS is a set of tools provided by CCS. It only occupies very little CPU resources, but provides very high performance, which speeds up the development progress. Using DSP/BIOS as the real-time operating system of the power quality monitoring terminal makes it easy to control hardware resources and flexibly coordinate various software modules when writing DSP programs, which greatly speeds up the development and debugging of software. The final experiment proves that the whole system has good real-time performance and stable and reliable operation.

Previous article:Application of DSP/BIOS in Power Quality Monitoring Terminal

Next article:Design of Software Radio Platform System Based on High-Performance DSP

- Popular Resources

- Popular amplifiers

- "Cross-chip" quantum entanglement helps build more powerful quantum computing capabilities

- Why is the vehicle operating system (Vehicle OS) becoming more and more important?

- Car Sensors - A detailed explanation of LiDAR

- Simple differences between automotive (ultrasonic, millimeter wave, laser) radars

- Comprehensive knowledge about automobile circuits

- Introduction of domestic automotive-grade bipolar latch Hall chip CHA44X

- Infineon Technologies and Magneti Marelli to Drive Regional Control Unit Innovation with AURIX™ TC4x MCU Family

- Power of E-band millimeter-wave radar

- Hardware design of power supply system for automobile controller

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Intel promotes AI with multi-dimensional efforts in technology, application, and ecology

- ChinaJoy Qualcomm Snapdragon Theme Pavilion takes you to experience the new changes in digital entertainment in the 5G era

- Infineon's latest generation IGBT technology platform enables precise control of speed and position

- Two test methods for LED lighting life

- Don't Let Lightning Induced Surges Scare You

- Application of brushless motor controller ML4425/4426

- Easy identification of LED power supply quality

- World's first integrated photovoltaic solar system completed in Israel

- Sliding window mean filter for avr microcontroller AD conversion

- What does call mean in the detailed explanation of ABB robot programming instructions?

- STMicroelectronics discloses its 2027-2028 financial model and path to achieve its 2030 goals

- 2024 China Automotive Charging and Battery Swapping Ecosystem Conference held in Taiyuan

- State-owned enterprises team up to invest in solid-state battery giant

- The evolution of electronic and electrical architecture is accelerating

- The first! National Automotive Chip Quality Inspection Center established

- BYD releases self-developed automotive chip using 4nm process, with a running score of up to 1.15 million

- GEODNET launches GEO-PULSE, a car GPS navigation device

- Should Chinese car companies develop their own high-computing chips?

- Infineon and Siemens combine embedded automotive software platform with microcontrollers to provide the necessary functions for next-generation SDVs

- Continental launches invisible biometric sensor display to monitor passengers' vital signs

- Experience in using TI DSP/BIOS and CCS

- Please tell me the output voltage of the bidirectional thyristor circuit

- The role of microcontrollers and local interconnect networks in body control modules

- I encountered many problems in my study as shown in the figure (I am a hardware developer and just learned C)

- How to consider and design ESD of RF modules?

- Verilog module content

- How to manage lithium battery charging using TPS40060 and MCU?

- Share interactive Q&A with TI experts | Design and optimization of buck-boost charging chip compatible with USB-PD protocol

- KiCad open source component library collection

- Does anyone know how to make the circuit boards in cars waterproof?

MCP6001RT-E/OT

MCP6001RT-E/OT

京公网安备 11010802033920号

京公网安备 11010802033920号