DSP chips are microprocessors with special structures designed specifically for implementing various digital signal processing algorithms. Their excellent performance, rising cost-effectiveness, and increasingly improved development methods have made them more and more widely used. Introducing computer network technology into embedded systems with DSP as the core, making them electronic products that combine digitalization and networking and integrate communication, computer and audio-visual functions, must greatly enhance the application value and market prospects of DSP systems. Combining DSP technology with network technology requires solving two key problems: one is to realize the hardware interface technology between DSP and network card, and the other is the network communication program design based on DSP. The reference [1] on the hardware interface technology between DSP and network card has a relatively detailed discussion. The following mainly discusses the network communication program design based on DSP.

1 Development of communication protocol

Protocols are regulations used to manage communications and are the basis for realizing network system functions. Since DSP can directly operate the network card, corresponding to the OSI network model, the network card contains all the contents of the physical layer and the data link layer. Therefore, by specifying the data frame encapsulation format on the data link layer, it is possible to provide specific specifications for the communication between any stations in the DSP-based local area network. Because Ethernet is one of the most popular local area networks today, in Ethernet, the network card is used to implement the 802.3 protocol, and its typical representatives are Novell's NE2000 and 3COM's 3C503 network cards. Therefore, the specific experimental platform in the research work is an Ethernet local area network composed of DSP as the core, mainly used for real-time voice communication, and the network card used is Novell's NE2000 network card. The basic composition of the NE2000 network card can be found in reference [2]. Its core component is the network interface controller (NIC) DP8390. The device has three functions: the first is the IEEE802.3MAC (media access control) sublayer protocol logic, which implements the encapsulation and decapsulation of data frames, CSMA/CA (carrier sense multiple access with collision detection) protocol and CRC check and other functions; the second is the register stack, and the user's control of the NE2000 network card communication process is mainly achieved by programming various command registers in these register stacks; the third is the read and write control logic of the buffer RAM on the network card. DP8390 sends and receives using the standard IEEE802.3 frame format. IEEE802.3 refers to the Ethernet protocol and technical specifications, but modifies the basic structure of the data packet, mainly the type field becomes the length field. Therefore, the basic format of the communication data packet in the LAN with DSP as the core is shown in Figure 1.

DSP reads out data packets and packs them starting from the destination address. The destination address is used to indicate the destination node address of a data frame to be transmitted in the network. NE2000 supports three types of destination addresses: single address, group address and broadcast address. A single address means that only one node can receive the frame information; a group address means that up to 64 bytes can receive the same frame information; and a broadcast address means that it can be received by all nodes in the same network. The source address is the physical address of the node sending the frame, which can only be a single address. The destination address and source address refer to the hardware address of the network card, also known as the physical address. The 2 bytes after the source address indicate the data length of the frame, which only indicates the length of the data part and is filled in by the user. The data field consists of 46 to 1500 bytes. Data greater than 1500 bytes should be divided into multiple frames for transmission; when less than 46 bytes, it must be padded to 46 bytes. There are two reasons: one is to ensure that the shortest frame length from the destination address field to the frame check field is 64 bytes, so as to distinguish valid frames from useless information in the channel; the other is to prevent a station from sending a short frame and completing the frame transmission before the first bit reaches the farthest end of the bus, so that the conflict signal cannot be detected when a collision may occur. NE2000 considers all frames received with less than 64 bytes after the destination address field as "fragments" and deletes them. In the data field, according to the specific functional requirements of the system, the user can reserve several bytes to specify the corresponding protocol so that the communicating parties can implement different functions based on the information contained in these bytes.

2 Network Communication Program Design Based on DSP

If based on a network operating system, users can easily write excellent network communication programs by using some software to support the network operating system, but these programs must be dependent on the network operating system. In the DSP environment, however, it is necessary to have a deep understanding of the working principle of the network interface controller (NIC) [2], and to achieve communication between any stations in the LAN by directly programming the network, completely abandoning the network operating system. The DSP's control of the communication process of the network card is to program and control the various registers in the DP8390 by the DSP to complete the correct transmission and reception of data packets. All internal registers of the DP8390 are 8 bits and mapped to 4 pages. Each page has 16 register addresses that can be read and written (RA=00H~0fH). The page selection is controlled by the command register CA. Page 0 registers are used for the transmission and reception process, page 1 registers are mainly used for the initialization of the DP8390, and page 2 registers are used for loop diagnosis. The DSP's operation on the register is to use the register as a port device of the DSP, and its actual physical port address (PPA) is the sum of the network card basic I/O port address (BIOA) and the register address (RA) (i.e. PPA=BIOA+RA). It should be noted that there is no one-to-one correspondence between PPA and registers. The read and write operations of PPA are not necessarily performed on the same register. This situation is particularly obvious on page 0. The interaction between the DSP and the network card is realized through the data port of the network card. The data packet can be read in or sent to the RAM buffer of the network card by DMA or PIO. In this system, the DSP uses DMA to read and write data to the network card. The data port address (NDPA) of the network card is the basic I/O address (BIOA) of the network card plus the offset address 10H (that is, NDPA=BIOA+10H). The control of the network card communication process can be divided into network card initialization, receiving control and sending control. They are discussed below.

2.1 Network card initialization

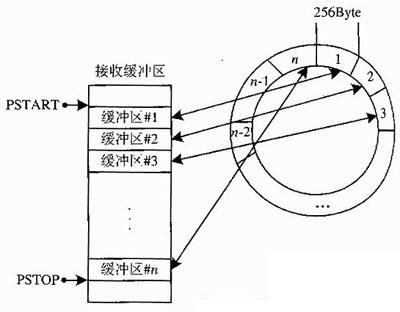

The main task of network card initialization is to set the required register state, determine the sending and receiving conditions, and divide the network card buffer RAM to establish the receiving and sending buffer rings. For the specific process, please refer to reference [2]. It should be noted that each network card is assigned a physical address for the identification of the communication site. This physical address is stored in the six units of the network card's PROM (storage address is 0000~0005H). When the network card is initialized, it is read into the DSP memory through remote DMA and sent to the network card physical address register. The significance of this step is: on the one hand, if the physical address of the network card can be read correctly, it means that there is basically no problem with the network card hardware, and the power-on reset of the network card and the initialization of the network card by the DSP are successfully passed; on the other hand, this physical address can be used for services such as roll call, packet filtering and discarding in the DSP network system. That is, at the link layer, the source address and destination address carried by the data frame determine where the datagram comes from and whether it is received or discarded. Another important task when the network card is initialized is the setting of the receiving buffer ring. In order to effectively use the buffer, the NIC forms a ring buffer structure with the receiving buffer RAM, as shown in Figure 2.

The receive buffer RAM is divided into multiple 256-byte buffers, and N (N is up to 256) such buffers are linked into a logical buffer ring through pointer control. The start page address of the buffer ring is stored in the PSTART register, and the end address of the ring page is stored in the PSTOP register. PSTART and PSTOP determine the size and boundary of the receive buffer ring. To facilitate the read and write operations of the buffer ring, two pointers are required: the current page pointer CURR and the boundary pointer BNRY. CURR determines where the next packet is placed and plays the role of the buffer ring write page pointer; BNRY points to the start page of the earliest data packet that has not been taken away and processed by the DSP. The newly received data packet cannot overwrite it and plays the role of the buffer ring read page pointer. In other words, CURR can tell the user where the data packet received by the network card is currently placed, while BNRY is used to determine where the DSP read buffer ring has reached. Since the receive buffer is a ring structure, when BNRY and CURR are equal, the ring buffer may be full or empty. In order to enable the NIC to distinguish between these two states, it is stipulated that the ring buffer is full only when BNRY is equal to CURR; when the buffer is empty, CURR is 1 greater than the BNRY pointer value. Therefore, during initialization, it is set: BNRY=PSTART, CURR=PSTART+1. At this time, the read and write pointers are inconsistent. In order to ensure correct read and write operations, a software pointer NEXTPK is introduced to indicate the start page of the next packet. Obviously, NEXTPK=CURR during initialization. At this time, the read pointer of the buffer ring is NEXTPK, and BNRY only stores the start page boundary indication of the packet buffer, and its value is NEXTPK-1.

2.2 Receiving control process

After DSP completes the initialization of DP8390, the network card is in the receiving state. Once a packet is received, it automatically executes local DMA, sends the FIFO data in the NIC to the receiving buffer ring, and then applies for the "data packet received" interrupt request to the host. If DSP responds to the interrupt, it starts the network card remote DMA read, reads the data packet in the network card buffer into the student computer storage area, and then modifies the content of the receiving buffer ring CURR, NEXTPK, BNRY pointers so that the network card can correctly receive subsequent packets from the Internet. After DSP responds to the network card receiving interrupt, the receiving control process is as follows: ① Set the starting address of remote DMA; RSAR0=00H, RSAR1=Nextpk. ② Set the number of bytes of remote DMA operation. This length is within the range of 46 to 1500 bytes and is determined by yourself according to specific requirements. ③ 0AH is sent to the command register CR to start remote DMA read. ④ Read data packets from the network card data port in sequence. Note that the first 4 bytes read in are not data packet content. The first byte is the receiving status, the second byte is the next packet page address pointer, and the third and fourth bytes are the number of received bytes. The second byte content should be sent to Nextpk, and the other bytes are processed according to user requirements. ⑤ Modify the boundary pointer BNRY = Nextpk-1. ⑥ Clear the remote DMA byte count registers RBCR0 and RBCR1.

2.3 Sending control process

DSP first executes remote DMA write operation, transfers the data packets in memory to the network card send buffer, and then starts the send command to send the data packets. The sending control process is as follows: ① Set the starting address of remote DMA to the starting address of the network card send buffer; ② Set the number of bytes of remote DMA operation; ③ 12H sends command register CR to start remote DMA write; ④ Send data packets to the network card send buffer in sequence; ⑤ Clear the remote DMA byte number register; ⑥ Set the send byte number registers TBCR0 and TBCR1; ⑦ 12H sends command register CR to start data packet sending.

3. Control of the sending frequency by the sender

Correct control of the sender's sending frequency mainly protects two points: one is that there is a minimum sending time interval, otherwise the system will be paralyzed because the receiver cannot receive it in time; the other is that the sending frequency can meet the specific function implementation requirements. For example, in real-time voice communication, the sending frequency depends on the sampling frequency of the sound card. At a sampling frequency of 8kHz, the sound card samples 8000 bytes per second, and it takes 128ms to use 1024 bytes. If the communication protocol stipulates that 1024 bytes of valid data are sent once, it must be sent once every 128ms to ensure that there is new data to be sent in the buffer and that the receiver has new data to play. 128ms is a theoretical calculation value. In actual operation, the sampling speed and the sending frequency are always not completely matched, and the size of the buffer for storing data is limited. If there is no good control technique to achieve correct sending, it will cause sound jitter and delay. The solution is double buffering technology and double pointer control, and according to the matching between the sampling speed and the sending frequency, it is sent to different sending communications for processing and then sent. Correct transmission has two meanings: one is that new data is sent each time, and the other is that it can meet the receiver's need to always play new data.

4. Receiver prevents packet loss

Since the DSP determines whether a data packet has arrived through an interrupt request, if the interrupt is busy and the arrival time of two data packets is very short, the DSP may only respond to the interrupt once, resulting in packet loss. Analyzing the process of the network card receiving data, when the network card receives a data packet, it first executes local DMA, sends the FIFO data in the NIC to the receiving buffer ring, and stores the starting address of the local DMA operation in the current page register (CURR) and the current local DMA register (CLDA0, CLDA1). The DSP reads data from the network card receiving buffer ring to the memory, which is called remote DMA operation, and uses the software pointer Nextpk to indicate the starting page of the remote DMA. Therefore, by comparing the current addresses of the network card local DMA and the remote DMA, that is, comparing the CURR and Nextpk pointers in the interrupt service subroutine, or comparing the CLDA0, CLDA1 and Nextpk pointers, it can ensure that the current data packet is read out where it is placed, thereby preventing packet loss.

5 Conclusion

DSP's implementation of network card communication process control solves the problem of accurate, high-speed real-time communication between any sites in the DSP network and between the DSP network and PC. It is the key to applying network technology to the DSP digital system, thus ultimately realizing the integration of digitalization and networking of the processing system with DSP as the core.

Previous article:Hardware Design of Frequency Conversion Speed Regulation System Based on DSP and IPM

Next article:Design and implementation of a USB and DSP fingerprint recognition system

Recommended ReadingLatest update time:2024-11-17 16:36

- Popular Resources

- Popular amplifiers

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- New breakthrough! Ultra-fast memory accelerates Intel Xeon 6-core processors

- New breakthrough! Ultra-fast memory accelerates Intel Xeon 6-core processors

- Consolidating vRAN sites onto a single server helps operators reduce total cost of ownership

- Consolidating vRAN sites onto a single server helps operators reduce total cost of ownership

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- A UART Circuit Design Based on FPGA

- [RVB2601 Creative Application Development] Flower Watering Indicator

- Understanding the alarm performance in arc fault detectors (fault arcs with 14 or more half cycles occurring within 1 second)

- How to transfer the 3.5mm recording jack output to the stereo speaker circuit

- November 19 live broadcast review: New requirements for connectors in 5G multi-scenario terminal applications and Molex's 5G connection solutions (including video)...

- DP83822I Industrial Ethernet PHY auto-negotiation function and its strap resistor configuration

- I would like to share with you the SDK for secret rooms developed based on STC microcontrollers.

- Desktop power supply interference problem

- EEWORLD University ---- Zigbee series tutorials

- Analog IC Design and Simulation

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication

京公网安备 11010802033920号

京公网安备 11010802033920号