With the development of information technology and chip technology, DSP technology has been widely used in aviation, communication, medical and consumer electronic devices. With the continuous increase of main frequency and multi-core parallel work, the computing power of DSP chips has increased rapidly. It has become more important to use DSP chips to quickly design software for multi-channel parallel processing of multiple types of signals. To meet the needs, this paper proposes a software architecture based on DSP/BIOS, which can improve the maintainability and reusability of the software, facilitate the reduction and addition of algorithms and the cross-platform transplantation of programs, and realize the rapid development and design of software for multi-channel parallel processing of multiple types of signals.

1 Introduction to DSP/BIOS

DSP/BIOS is a real-time operating system launched by TI, which is integrated into the CCS (Code Composer Studio) development environment. DSP/BIOS adopts a static configuration strategy. By removing the running code, it can minimize the storage space of the target program, optimize the internal data structure, and detect errors earlier by confirming the ownership of the object before the program is executed. It can meet the debugging and performance analysis of DSP runtime. Using DSP/BIOS can quickly write efficient programs and greatly simplify the development and debugging of DSP applications. DSP/BIOS is a set of system module application program interface APIs that can be repeatedly called, divided into system module System, auxiliary module Instrumentation, scheduling module Scheduling, synchronization module Synchronization, communication module Input/Output and configuration module CSL. The system module mainly completes chip model confirmation, endian mode configuration, main frequency configuration, chip cashe space division and memory space allocation. The auxiliary module Instrumentation is mainly responsible for message printing, event log and information tracking. The scheduling module is the core function of DSP/BIOS, which can be subdivided into timing management CLK, periodic interrupt management PRD, hard interrupt management HWI, soft interrupt management SWI, task management TSK and idle task management IDL. CLK controls the 32-bit real-time logic clock in the chip and is responsible for setting the PRD cycle. PRD manages cycle objects and triggers the cycle execution of the application. It is a special SWI. HWI manages hardware interrupts and is mainly responsible for the data interaction between DSP and peripherals. The interrupt service program should be as short and precise as possible. SWI is a non-blocking preemptive type. SWI tasks can only be pre-defined when the program is compiled. TSK is a blocking preemptive type and supports dynamic generation of tasks. IDL manages the sleep function. The sleep function is started when the target system program has no higher priority function running. It is a special TSK. The synchronization module is responsible for the exchange and transmission of information between various scheduling modules to ensure synchronization and mutual exclusion between scheduling modules. The communication module allows the application to exchange data between the target system and the host. The configuration module is responsible for the configuration of the underlying hardware of the chip. In addition, DSP/BIOS also has plug-ins to support real-time analysis, program tracking and performance monitoring.

2 DSP Software Architecture

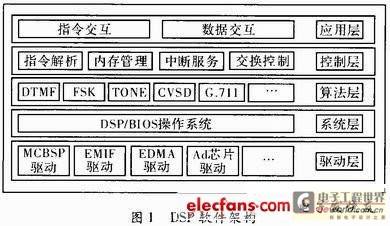

The software architecture adopts a layered design concept and is divided into five layers: driver layer, system layer, algorithm layer, control layer and application layer. The driver layer completes the chip hardware interface and peripheral chip driver. The system layer runs the DSP/BIOS operating system and completes the hardware interrupt, cycle control and task scheduling functions. The algorithm layer provides algorithm APIs for various business needs. The control layer is responsible for software instruction parsing, memory management, interrupt service and exchange control. The application layer provides instruction interaction and data interaction interfaces for the CPU to call and control the DSP.

3 Sublayer Design

3.1 Driver layer

Use the graphical interface of DSP/BIOS to call the chip support library module CSL, quickly set the DSP underlying hardware interface, and complete the development of the chip's MCBSP driver, EMIF driver, and EDMA driver. For the driver of peripheral chips, such as the A/D chip driver, first complete the connection between the DSP chip and the A/D chip in hardware, and then complete the configuration of the A/D chip according to the frame format of the configuration instruction.

3.2 System Layer

The system layer design is the key point of software architecture design, making full use of the scheduling module and synchronization module provided by DSP/BIOS. The instruction parsing, exchange control and exchange table update modules in the control layer are bound to PRD, and new instructions are checked periodically. The exchange table is updated according to the instruction parsing. The scheduling cycle is controlled by a 32-bit real-time logic clock. The exchange control and data exchange modules in the control layer are bound to TSK, and data format conversion is performed according to the semaphore SEM or mailbox information MBX received from other modules to complete the transparent transmission of data in different formats between different channels. The interrupt service is bound to HWI to complete the real-time data transmission and reception. The mailbox mechanism MBX and the semaphore SEM mechanism in the synchronization module Synchronization are used to complete the message transmission between HWI, PRD and TSK. The scheduling algorithm of the operating system is used to complete the scheduling between multiple tasks, control data transmission and reception, and data processing.

3.3 Algorithm layer

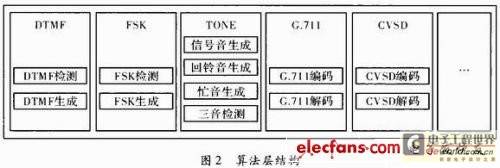

List all kinds of algorithms as a single layer, gather multiple types of signal algorithms, adopt loose coupling and reentrant design methods, facilitate algorithm transplantation, maintenance and multi-channel parallel work design, and facilitate algorithm tailoring and expansion according to application requirements. All kinds of algorithms are strictly independent and provided in the form of separate libraries and header files. The structure of the algorithm layer is shown in Figure 2.

3.4 Commonly used communication algorithms

DTMF: Dual-tone multi-frequency signal, each number is obtained by adding two audio signals, widely used in telephone dialing and caller ID, its generation and detection algorithm.

FSK: Utilizes 1 200 Hz and 2 200 Hz sinusoidal signals and adopts 2FSK modulation and demodulation method, which is widely used in caller ID. Its generation and detection algorithm.

TONE: Three-tone generation and detection algorithm, including signal tone, busy tone, and ringback tone generation and three-tone detection, widely used in telephone exchange systems.

G. 711: A speech codec standard with a rate of 64 khit·s-1, widely used in telephone switching systems.

CVSD: Continuously Variable Slope Codec, a speech codec standard with a rate of 16 khit·s-1, used in low-rate communication systems, and its codec algorithm.

3.5 Control Layer

The control layer design is the second key point of software architecture design, which plays a bridging role between the application layer and the system layer and algorithm layer. It consists of four modules: instruction parsing, memory management, interrupt service and exchange control. Instruction parsing is called by the operating system PRD, and periodically determines whether there are new instructions. If there are new instructions, the new instructions are first put into the instruction FIFO memory, and then the instruction space is cleared to avoid making wrong judgments when the instruction parsing function is called next time. Finally, the instruction parsing module will parse the contents in the instruction FIFO and update the exchange table in the exchange control module according to the parsing results. Memory management allocates a sending buffer area Tx Buffer and a receiving buffer area Rx Buffer for each service channel, and equips each Tx Butter and Rx Buffer with a management pointer to indicate the storage location and free location of the data in the Buffer, and thus calculates the number of data and free space size of each Buffer, and completes the processing of abnormal operations such as Buffer overflow generated during the write operation or Buffer empty generated during the read operation. When a hardware interrupt occurs, the interrupt service is called by the BIOS system HWI to complete real-time data transmission and reception. Interrupt services need to ensure real-time performance, not perform excessive control and calculation, minimize the number of executed instructions, and use short-cycle instructions. If necessary, use the optimized Intrinsics functions provided by CCS to optimize the program or use assembly instructions to write. HWI cannot be blocked. In interrupt services, functions that may cause blocking cannot be called. Information exchange with other tasks in the system can be interacted through the mailbox mechanism MBX or the signal light mechanism SEM in the assistance module. The exchange control module realizes the exchange of data between different channels, and is accompanied by the conversion of different data formats. Exchange control includes exchange table management and data exchange, and has a variety of exchange capabilities. Exchange table management has the function of deleting and adding exchange table entries. The data exchange module completes the conversion of source channel data to destination channel data format according to the exchange table, and then places the converted data in the send buffer of the destination channel, waiting for data to be sent, with multi-channel parallel working capabilities. The data interaction between modules within the control layer is shown in Figure 3.

3.6 Application Layer

The application layer design adopts a memory sharing mechanism to realize the instruction interaction and data interaction between DSP and CPU. To ensure the integrity and correctness of each read and write data, an effective communication mechanism needs to be established between the two processors to ensure that the same address will not be operated at the same time. Instruction interaction is responsible for receiving CPU instructions and returning results to the CPU. The instruction parsing module periodically reads instructions and parses them to control the operation of each service channel of DSP. If it is a DTMF detection, FSK detection or TONE detection instruction, DSP will feed back the parsed results to CPU. If it is a DTMF generation, FSK generation or TONE generation instruction, DSP will send the DTMF signal, FSK signal or dial tone, busy tone, ringback tone or hang-up tone corresponding to the number to the specified service channel; if it is a two-channel voice format conversion instruction, DSP will receive data from the source channel, complete the format conversion, and send it to the destination channel. Data interaction, DSP and CPU can also exchange data through shared memory, and the storage status of data will be controlled by the memory management module.

4 Conclusion

The software architecture introduced in this paper has been verified in practical applications. In TMS320VC5416, 32-channel multi-signal processing (DTMF, FSK, TONE, CVSD, G. 711) can be completed simultaneously. In TMS320C6418, 128-channel multi-signal processing (DTMF, FSK, TONE, CVSD, G. 711) can be completed simultaneously. In addition, multi-channel G. 729 processing can be added. This software architecture can ensure the separate development and reuse of different algorithms. When porting across platforms, according to different hardware interfaces, only the driver layer needs to be reconfigured, and the codes of the remaining layers can be directly ported, which accelerates the development and design of multi-signal parallel processing software.

Previous article:Embedded digital camera nighttime visibility measurement system based on DSP

Next article:Take you to understand TI's DSP entry chip TMS320F28335

Recommended ReadingLatest update time:2024-11-16 17:29

- Popular Resources

- Popular amplifiers

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Use MOS tube or triode?

- Award-winning live broadcast | Power supply, motor, electronic control, new energy vehicle power design technology is coming

- Why is this TVS designed like this?

- I called Knowles today and it was hilarious.

- Is there any sensor that can detect whether there is someone in front through the tinted glass?

- Should the filter capacitor and bleeder resistor in the circuit be placed before or after the anti-reverse polarity diode?

- Which teacher can explain this circuit?

- [2022 Digi-Key Innovation Design Competition] 1. STM32F7508-DK Unboxing

- Some predictions about the national competition questions - about power supply questions

- RFID low frequency and high frequency antenna technology

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication

京公网安备 11010802033920号

京公网安备 11010802033920号