Abstract: Based on the recommendations of the Advanced On-Orbit System (AOS) of the Consultative Committee on Space Data Systems (CCSDS), a two-level multiplexing scheme was proposed, and a high-speed real-time/playback hierarchical multiplexer with payload data storage function was designed. The scheme uses FPGA technology and uses a two-level fully asynchronous multiplexing strategy for data storage and virtual channel scheduling for the data output by the onboard payload. The experimental results show that the multiplexer has achieved a good integration of payload data storage and multiplexing functions, and has flexible functions and low hardware resource utilization.

1. Introduction

With the rapid development of satellite communication systems, the data transmission rate provided by space links is getting higher and higher, allowing various satellite platforms to apply payloads that generate a large amount of high-speed real-time data. Due to the different working modes, data volumes, data formats, rates and real-time requirements of each payload, the data transmission interaction time between space and ground is short and easily interrupted, and the onboard data processing system should have large-capacity storage and high-speed processing capabilities, and be able to store, multiplex and other preparations for the data before it is downlinked to the ground.

High-speed multiplexers are responsible for multiplexing and downlinking various data generated by payloads in space data transmission. New data transmission requirements have also put forward new requirements for the performance and flexibility of high-speed multiplexers. Traditional onboard data processing systems usually process payload data multiplexing and large-capacity storage separately. However, for some small satellites, the amount of data to be stored (such as scientific experiment data, image observation data, etc.) is not particularly large, and the real-time requirements are not high. If traditional processing methods are used, more onboard resources will be occupied, and the design, implementation and collaboration of high-speed multiplexers and large-capacity storage will also be more complicated. In response to this demand, this paper proposes the concept of two-level multiplexing, adds data storage function to high-speed multiplexers, and refers to the CCSDS AOS recommendations. A two-level multiplexing scheme that unifies real-time transmission and non-real-time playback of data is proposed. Based on FPGA technology, the hardware implementation and technical solution of a small and flexible high-speed real-time/playback hierarchical multiplexer are designed and explored to realize the integration of multiplexing, storage and playback functions of payload data on board.

2. Research on AOS high-speed real-time/playback hierarchical multiplexing

2.1 Advanced Orbital System (AOS) and Virtual Channel Multiplexing In order to meet new space requirements, the International Consultative Committee for Space Data Systems (CCSDS) proposed the AOS recommendation in 1986, providing more diverse and flexible data processing services than conventional recommendations to meet the needs of complex systems such as advanced orbital systems and the International Space Station. A key feature of the CCSDS protocol provided to the AOS space link subnet is the concept of virtual channels. A physical channel is divided into multiple logical channels, each logical channel is individually identified and transmits a data stream, and each data stream can use different services. A logical channel is a virtual channel. Virtual channels enable a physical space channel to be shared by multiple high-level data streams in a time-division multiplexing manner, making it possible to transmit multiple different types of data on a physical channel, thus laying the theoretical foundation for multiplexing.

2.2 Proposal of two-level multiplexing method

Virtual channels time-division multiplex physical channels and dynamically manage physical channels according to a certain multiplexing method. Since high-speed real-time/playback hierarchical multiplexers need to complete both storage and multiplexing tasks, it is difficult to fully meet their needs using only one-level asynchronous multiplexing. Therefore, this paper rationally tailors the CCSDS advanced on-orbit protocol and proposes the idea of two-level multiplexing. A level of storage is added before the original virtual channel multiplexing, and both levels of virtual channel multiplexing adopt a fully asynchronous multiplexing method. In the first level of multiplexing, AOS transmission frames are generated according to channel priority, and valid data frames are stored in the storage unit as historical data. In the second level of multiplexing, asynchronous multiplexing is used again, and channels are selected according to channel priority. Each channel of real-time data and one channel of historical data are mixed and multiplexed downlink in the format of AOS transmission frames according to a certain channel scheduling algorithm.

3. Technical solution for high-speed real-time/playback hierarchical multiplexer

3.1 FPGA chip selection

This design uses the 1.5 million gate XILINX SPARTAN-XC3S1500 chip with 90nm process technology. Since the multiplexer requires a high data input and output rate, the I/O speed requirement for the FPGA chip is relatively high. Each I/O port of the SPARTAN-XC3S1500 chip supports a data transmission rate of 622Mb/s, which can meet the design requirements. Its arithmetic processing function can also meet relatively complex calculation requirements. This chip can not only meet more complex timing functions, but also solve technical requirements such as fast speed, low power consumption, high integration, and flexible design.

3.2 Overall technical solution of the system

In order to save on-board resources and improve the flexibility of payload data processing, this paper proposes the concept of two-level multiplexing and designs an AOS high-speed real-time/playback hierarchical multiplexer working in the space data link layer based on FPGA technology. The overall functional block diagram is shown in Figure 1.

Figure 1 Functional block diagram of CCSDS AOS high-speed real-time/playback hierarchical multiplexer [page]

3.3 Storage and Scheduling Algorithm Design

The design of AOS high-speed real-time/playback hierarchical multiplexer focuses on the algorithm of virtual channel scheduling. The design of high-speed and high-channel utilization virtual channel scheduling strategy is one of the key technologies in the design of hierarchical multiplexer. The reasonable design of scheduling strategy algorithm will ensure that AOS high-speed real-time/playback hierarchical multiplexer can complete the functional tasks of storage and multiplexing transmission efficiently and orderly. The block diagram of the virtual channel scheduling algorithm of this design is shown in Figure 2.

Under each level of working state, the priority of each virtual channel is first determined by the source rate. Then the multiplexer determines the virtual channel to be connected according to the storage space and fullness of each data source buffer and storage unit.

In the first-level multiplexing state, the virtual channel service data unit selected for access will be stored in the storage unit in the standard frame format of CCSDS AOS. The write enable of the storage unit is only turned on when a valid data frame is accessed, ensuring that only valid data frames can enter the storage unit to save storage space. After entering the second-level multiplexing state, the historical data in the storage unit is multiplexed downlink with other real-time data. Each asynchronous data cache sends a transmission request to the virtual channel scheduling module based on the existing storage status. The virtual channel scheduling module selects the asynchronous channel to access based on the priority strategy. If there is no valid asynchronous data, the padding data is sent according to the padding mechanism.

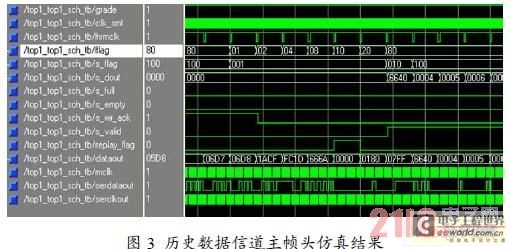

For the AOS high-speed real-time/playback hierarchical multiplexer, the design of the virtual channel identifier, virtual channel frame count and playback mark in the main frame header of the transmission frame is the key identifier for storage and virtual channel scheduling. The virtual channel identifier distinguishes the data of each channel of the access channel, the playback mark distinguishes the real-time data from the historical data, and the virtual channel frame count records the order of each frame data of each channel. In order to ensure that the historical data can be restored completely, accurately and conveniently after the ground receives the payload data, a unified virtual channel frame count and virtual channel identifier are used in the two-level multiplexing framing. In this way, the downlink data after two multiplexing at the sending end can be restored by only one deframing at the ground receiving end. Therefore, using this flexible design, there is no need to change the existing ground receiving equipment, making the AOS high-speed real-time/playback hierarchical multiplexer highly portable. The simulation results of the main frame header of the historical data channel after two-level multiplexing are shown in Figure 3.

3.4 Hardware Verification Demonstration System and Test Results

A verification demonstration system as shown in Figure 4 was built to verify the function of the AOS high-speed real-time/playback hierarchical multiplexer. At the sending end of the demonstration system, the image data is converted into a code stream, and together with the scientific experiment data, it is used as the signal source of the high-speed hierarchical multiplexer and enters the buffer area prepared by the multiplexer for the signal source. After being multiplexed downstream by the high-speed hierarchical multiplexer, it becomes a serial output. The receiving end sends the received serial code stream to the receiving and branching processing device for virtual channel branching after frame synchronization, and extracts the business data unit of each virtual channel, and finally sends it to the computer terminal, where the complete scientific experiment data and image data can be seen respectively.

The test results show that the AOS high-speed real-time/playback hierarchical multiplexer can perform storage and multiplexing tasks well, the data of each virtual channel remains smooth without loss, and the serial output rate is 50Mbps.

4. Conclusion

This paper introduces the multiplexing mode of the CCSDS protocol advanced on-orbit system and the AOS transmission frame structure, proposes the concept of two-level multiplexing, and discusses the hardware implementation and technical solution of the AOS real-time/playback hierarchical multiplexer. Due to the use of FPGA large-scale logic devices and the reasonable tailoring of the AOS protocol, the design is small in size, flexible in performance and easy to transplant. The research of this topic will provide ideas for the integration of key data processing equipment in aerospace application engineering, and will have guiding significance for the further development of light, flexible, efficient and applicable satellite-borne data management equipment.

The author's innovations are as follows: First, the author proposed the concept of two-level multiplexing, making full use of the flexible and efficient characteristics of fully asynchronous multiplexing, and through reasonable tailoring of the CCSDS AOS protocol, the two-level multiplexing cooperates with each other to complete the tasks of storage, multiplexing and playback. Second, the author provides a complete design scheme of the AOS real-time/playback hierarchical multiplexer based on FPGA. The design concept is flexible. After two multiplexings at the sending end, the downlink data can be restored by deframing once at the ground receiving end, without changing the original ground receiving equipment, and has strong portability.

Previous article:Design of high-precision time-to-digital conversion circuit based on FPGA

Next article:FPGA Implementation of a Precise Symbol Timing Algorithm for OFDM Systems

Recommended ReadingLatest update time:2024-11-16 17:47

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Direct Memory Access (DMA) Controller - TMS320VC5509A

- A must-read for beginners! Experts explain the PCB return path for high-speed circuits

- Two major power outages in five days! The Taiwan authorities have asked TSMC to relocate or suspend some production lines

- PADS PCB 3D component library

- Frequency division of analog signals

- C2000-GNAG Operation and Use

- [ESK32-360 Review] 6. Hello! Hello! Hello! Hello!

- [NXP Rapid IoT Review] NXP Rapid IOT Experience

- Is there any teacher who can help me write a program for Mitsubishi FX3U to output pulses?

- RTL8762, an excellent domestic BLE low-power solution

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号