Introduction

With the application and development of electronic technology, digital signal processing content is becoming increasingly complex. At the same time, in many cases, the entire system is required to have low power consumption. In order to meet this requirement, DSP chip design technology is also developing in the direction of low power consumption and high performance. From the perspective of processing speed, the computing power of TMS320VC5502 has reached 600MMACS, that is, it can complete 600 million multiplication and addition operations per second. From the perspective of power consumption, the core voltage of TMS320VC5502 is only 1.26V, and the power consumption of the entire chip is also greatly reduced. This article introduces a low-power multi-channel data processing system based on TMS320VC5502 and CPLD XC95144.

The input of the analog signal passes through a 50Hz notch circuit (to filter out power frequency interference) and a signal pre-selection circuit. The preprocessed analog signal is used as the analog input of the ADC for A/D conversion, and finally the DSP implements filtering of the digital signal. Combining CPLD and DSP technology and using the flexibility of CPLD programming to control the start and stop of 6-channel ADCs simplifies the design of the entire hardware circuit and achieves the purpose of dynamically selecting sampling channels. At the same time, the data processed by DSP is sent to the PC, and tools such as MATLAB and VC are used on the PC to perform back-end analysis on the processed data. This article mainly introduces the front-end data acquisition and processing system based on low-power TMS320VC5502 and CPLD.

Introduction to ADS7805

ADS7805 is an A/D conversion chip with 16-bit quantization accuracy. Its basic structure includes a 16-bit precision capacitor network-based successive approximation ADC, sample and hold circuit, clock, interface to microprocessor and three-state output. The maximum sampling rate of ADS7805 is 100kHz, the analog signal input range is -10V~+10V, it is powered by a 5V single power supply, and the maximum power dissipation is 100mW.

The ADS7805 is powered by a 5V single power supply. When the output data bit is '1', the level value is 5V. The I/O voltage of the DSP chip uses a 3.3V logic level. Therefore, it is also necessary to connect the data output terminal of the ADS7805. In addition to the level conversion chip, 74ALVC164245 was selected in the design, which can convert the 5V level to 3.3V and 3.3V to 5V.

Hardware interface circuit design

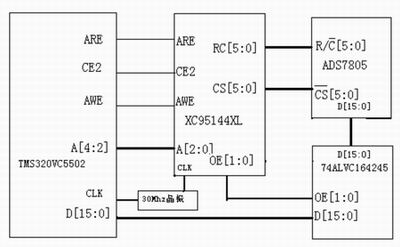

From a hardware perspective, DSP completes the core work of filtering operations, and the control core of the entire system is CPLD. The DSP's operation of 6-channel A/D sampling is generated by the CPLD, which controls the sampling trigger of the ADS7805. Signal, multiplexing and demultiplexing of 6 ADCs, and gating of 5V to 3.3V voltage conversion chip 74ALVC164245, etc. The clock inputs of CPLD and DSP use 30MHz active crystal oscillator. The interface circuit between CPLD, DSP, ADC and level conversion chip is shown in Figure 1.

Figure 1 DSP, CPLD and ADC interface circuit diagram

The DSP uses the chip select signal, address signal, and read and write enable signals to send instructions to the CPLD. The CPLD sends control signals to the six ADS7805s according to the instructions of the DSP, starts the chip for sampling, and controls the DSP to complete the reading of the data. Since the data output by the ADS7805 must pass through the level conversion chip, the CPLD also needs to control the gating and conversion of the 74ALVC164245 chip, which is the OE[1:0] signal in Figure 1. Therefore, the control signals that the DSP must provide to the CPLD include the CE2 chip select signal, the ARE read enable signal and the AWE write enable signal. When the DSP reads the A/D conversion data, it strobes 74ALVC164245 for level conversion. When the ADC When performing A/D conversion on analog signals, disable the 164245 chip to avoid data bus conflicts caused by multi-channel data. Since there are 6 ADS7805s, at least 3 address line signals need to be allocated (generally selected as the lowest 3-bit address line pins) to distinguish these 6 ADS7805s, but the 3 address line signals can actually be used to represent 8 addresses, and the remaining The two addresses can also be used. For example, a read operation on one of the remaining two addresses can be regarded as a command issued by the DSP to start the ADS7805, so that the connection of the AWE signal between the DSP and the CPLD can be omitted. . The signals that the CPLD needs to provide to the ADS7805 include the chip select signal CS[5:0] and the data read/start conversion signal RC[5:0]. In addition, the CPLD also needs to provide the chip select signal of the level conversion chip and needs to be connected. Enter a clock signal to provide a synchronous clock signal for sequential logic to the CPLD.

CPLD programming:

Based on the working principle of ADS7805 and the reading and writing characteristics of DSP, CPLD is programmed to realize the time-sharing reading operation of six ADS7805s by DSP and to start the conversion of ADS7805.

The entire program is designed using Verilog HDL language. In order to facilitate testing, a FLAG flag signal is added. When FLAG is low, it means that the DSP is reading the data converted by ADS7805. When FLAG is high, it means that ADS7805 is undergoing a new round of conversion. The focus of the program design is to start a new round of sampling of the ADS7805, and the ADS7805 starting sampling requires CS and RC to be low at the same time and remain for 40ns. When the DSP has finished reading the data of the 6 ADCs, it will start a new round of sampling. When the read operation of the sixth ADS7805 is completed, the FLAG flag is pulled high and the counter is used for timing. The input clock frequency is 30MHz. Therefore, it is necessary to keep the RC[5:0] and CS[5:0] output signals low for at least 2 clock cycles to successfully start the next A/D conversion. According to the requirements of the system, the CPLD program is mainly divided into 3 always blocks.

The first module uses the DSP's CE2 address space selection signal, address line A[4:2], ARE read signal and the defined 3-bit counter cnt[2:0] as the trigger signal. When both CE2 and ARE are low, one of the six is selected for reading based on A[4:2] of the DSP, and the other five are disabled. At this time, RC[5:0] should all be high. If A[4:2]=000, then CS[5:0]=111110, start reading the first ADS7805 data to the DSP. In order to prevent data loss, when reading data, RC[5:0] should always remain high, because if the same bit in the CS[5:0] and RC[5:0] signals remains low for more than 40ns, it will Starting a new sampling will cause the ADS7805 that has not been read to generate a new sampling and discard the previously converted data, which will have a great impact on the results of the entire system. After reading the sixth ADC, the FLAG flag is pulled high on the rising edge of ARE. At this time, the counter starts counting. According to the value of the counter, when 2

Based on the above design ideas, the sampling and reading control of 6-channel signals were successfully achieved, achieving the expected results. The simulation waveform is shown in Figure 2.

Figure 2 CPLD simulation waveform diagram

DSP software design

Before DSP program design, first use MATLAB's FDATOOL tool to design a digital filter, export the filter coefficients to MATLAB in the form of .h file, and define an array in CCS to store the filter coefficients. You can successfully import the filter coefficients into CCS.

This article mainly introduces the software design scheme for DSP to read and process multi-channel signals. Figure 3 is a flow chart of the entire program. First, the DSP chip should be initialized, which mainly includes initializing the PLL register of TMS320VC5502, initializing the system interrupt vector table, initializing EMIF and initializing the timer. The DSP reads the conversion data of the peripheral ADC through the EMIF interface. The entire data reading and digital filtering work is performed in the timer interrupt program. The timer module is mainly used to determine the sampling period, that is, every time a timer interrupt occurs, the signal is sampled and the real-time processing operation of the signal is completed. Therefore, the interrupt period of the timer is also the sampling period. At the same time, it also stipulates the upper limit of the time it takes for the DSP to perform a signal processing operation, that is, the calculations and operations required for a processing must be completed between two adjacent clock interrupts. . Then initialize the EMIF module. This part is more important because the data converted by the ADC is sent to the DSP chip through the EMIF interface. The ADC chip is memory-based in this system. That is to say, from the perspective of the DSP chip, there is no difference between reading and writing the ADC chip and reading and writing the asynchronous SRAM. Therefore, the ADC chip must also be allocated to the off-chip storage space. The method adopted by the system is to allocate the ADC chip to six consecutive addresses of 0x400000~0x400005 in the CE2 space, and use the asynchronous 16-bit SRAM configuration method to configure the control register of the CE2 space. When there is an interrupt request, the DSP enters the timer interrupt with a frequency of 40KHz to perform reading and filtering work.

Figure 3 DSP program flow chart

The system power consumption

is estimated by consulting the chip manual. The 1.26V core voltage power supply capability required by TMS320VC5502 is 250mA, the 3.3V I/O voltage and phase-locked loop I/O voltage power supply capability are 50mA, and the power consumption of the DSP chip is 480mW. The typical power consumption of the ADS7805 chip is 100mW, with 6 chips totaling 600mW. The typical current consumption of the 3.3V power supply of CPLD is 100mA, which is 330mW. In this way, the power consumption of the entire system is approximately 1.5W. This power consumption is also acceptable when using battery power. For example, using a 12V output, 50Ah battery can ideally power the system for 400 hours. Even considering the energy loss during voltage conversion, it is feasible to use the battery with the above specifications to power the system for 40 hours.

Conclusion

: This article introduces a low-power multi-channel data acquisition system based on DSP and CPLD. CPLD simplifies hardware design, can easily program the system online, and has high flexibility. This system has been used in military and other fields with low power consumption and high performance requirements.

Previous article:FPGA implementation of WCDMA rate adaptation algorithm

Next article:Design of low-power multi-channel data processing system based on DSP and CPLD

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- [GD32L233C-START Review] 1. GD32L233C-START with obvious advantages and disadvantages (unboxing)

- LTC2325-16 Sampling Issues

- Design considerations for single-chip microcomputer key scanning program

- How to change the library file in the schematic diagram in orcad?

- Free application: Domestic FPGA Gaoyunjia Little Bee Family GW1N Series Development Board

- Taking stock of the college entrance examination experience of Internet tycoons! How many points did you get in the exam?

- Without American EDA software, we can’t make chips?

- 【Share】Flash management tools: FAL (Flash Abstraction Layer) library

- Good morning my love——One Xiao and One Jian

- [Awards awarded] Grab the post! Download the TWS headset white paper, write a wonderful review, and win a JD card!

A Practical Tutorial on ASIC Design (Compiled by Yu Xiqing)

A Practical Tutorial on ASIC Design (Compiled by Yu Xiqing)

京公网安备 11010802033920号

京公网安备 11010802033920号