1 Introduction

There are generally three hardware solutions for image processing systems that complete a specific task: using general-purpose computers, using ASICs, and using DSPs. The advantages of using general-purpose computers are that the development cycle is short, the cost is low, and the product is easy to maintain and upgrade; the disadvantage is that the computing speed is limited, and it is difficult to meet the real-time requirements for applications with high algorithm computing volume and complexity. This solution has two application scenarios: the early and middle stages of algorithm development and some fields with low real-time requirements. In the solution using ASIC, all operations are implemented by hardware, so the real-time performance will be very good, but the hardware design is a major difficulty, and once the system is finalized, it is not convenient to upgrade it. The use of high-speed DSP can be said to be a compromise between the two solutions. On the one hand, in terms of hardware implementation, it is only necessary to design the DSP peripheral interface circuit according to the needs. On the other

hand, with the rapid development of DSP technology and the continuous introduction of high-performance chips, its computing power can also meet the requirements of general image processing. Moreover, the system functions are implemented by algorithm software, which is also convenient for system maintenance and upgrades.

This paper uses TI's multimedia DSP chip TMS320 DM642 [4] (DM642 for short) to implement an application platform with basic image processing system functions, including video input, video output, and serial communication functions.

2. System hardware design

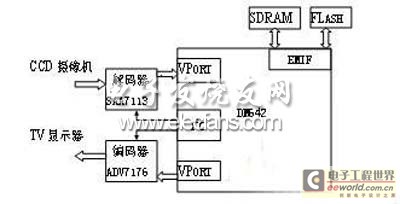

The hardware composition of the system is shown in Figure 1. With DM642 as the core, the external memory SDRAM and Flash are expanded for program running and program storage respectively; the video acquisition and output are completed by controlling the video codec; and the UART is realized through the McBSP interface to facilitate the communication between the visual system and the outside world.

Figure 1 DSP vision system hardware structure diagram

In the system, the extended external memory includes ROM and SDRAM. Among them, ROM uses Atmel's Flash, model AT49BV1614, with a capacity of 16MBits, and is used as Boot ROM when the system starts; SDRAM is composed of two chips with specifications of 4Banks×512K×32Bits, model HY57V643220CT, which is used to store programs, data and videos. The video ADC uses Phillips' SAA7113, with a conversion accuracy of 9Bits, 4 analog input channels, and can input 4 analog video signals. There is one output interface (VP0), which supports the three main analog video formats of PAL, NTSC, and SECAM. The video output DAC chip uses the ADV7176 video encoder launched by Analog Devices, with a conversion accuracy of 10Bits and a maximum signal-to-noise ratio of 80dB. It reads data from DM642 under the control of DM642's line and field synchronization signals and its own clock, and outputs it to the TV monitor for display after D/A conversion. The communication interface uses the existing synchronous serial port McBSP and EDMA of DM642 to realize the UART method. A MAX3323E is added to the hardware to realize the conversion between CMOS logic level and RS-232 logic level to meet the requirements of serial communication with the control computer.

3. System software design

In order to provide software development support for its DSP products, TI launched DSP/BIOS (Basic Input Output System), a preemptive, customizable real-time multitasking operating system that is integrated with the CCS (Code Composer Studio) compilation environment. Using DSP/BIOS allows for efficient application development. The software development of the image system in this article is based on the DSP/BIOS environment. 3.1 Software Design Process

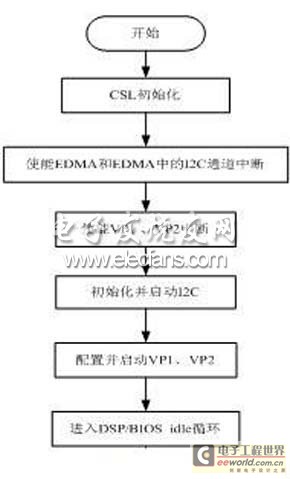

The software flow of the image processing system in this paper is shown in Figure 2. The main application program needs to complete the initialization of the CSL (Chip Support Library) library first, so that the relevant chip-level support library functions can be called in the program. Subsequently, the EDMA interrupt is turned on, and the interrupt of the I2C channel in the EDMA is enabled; the VP1 and VP2 port interrupts are turned on; the I2C data transmission is initialized and started, and the parameter initialization number configuration of the registers of the video decoding chip SAA7113 and the video encoding chip ADV7176 is completed; the VP1 and VP2 video ports are configured and started; and finally the idle waiting loop is entered. The video acquisition is carried out in an interrupt manner. When a frame of image is acquired, the VP1 interrupt is triggered, and the system calls the corresponding interrupt subroutine to process and calculate the image data, calculate the parameters such as position and posture, and finally transmit the parameters to the control computer through UART.

Figure 2 Main program flow

The EDMA controller of DM642 is responsible for data transmission between the on-chip L2 memory and other devices. It can provide an external bandwidth of more than 2Gb/s and has 64 channels. Each channel has an event associated with it, and these events trigger the transmission of the corresponding channel. In the above process, the parameter transmission of A/D and D/A chip initialization and the acquisition of video data are all realized through EDMA.

3.2 Initialization of A/D and D/A Chips

The initialization process of A/D and D/A chips is realized through the I2C channel in EDMA. The data parameters to be transmitted are configured in the parameter RAM table of EDMA, which mainly includes the source data starting address, destination address, address modification method, data format and size to be transmitted. The initialization data parameters of the two chips are configured in two different RAM tables respectively. After the first EDMA data transmission of the I2C channel is completed, the EDMA controller sends an interrupt to the CPU, and the interrupt handler loads the RAM parameter table of the second I2C transmission to start the second transmission process. Thus, the initialization process of the two chips is completed.

3.3 Video Capture and Output

Corresponding to the YUV 4:2:2 format video data acquisition, there are three channels in EDMA for VP1 data transmission. The system configures the video port VP1 as a continuous frame acquisition mode, that is, after starting the acquisition of the first frame, the acquisition of the following frames is continuous without the need for additional frame synchronization signals.

In interlaced scanning mode, each frame is divided into two fields, which are separated in the time domain. Field synthesis can be automatically realized through the EDMA linked list without taking up additional CPU time. The parameter RAM of EDMA stores the relevant transmission parameters, which are used to generate the addresses required for EDMA read and write operations. When using the EDMA channel to transmit odd and even fields, different EDMA parameter RAMs are used respectively. The destination addresses of the two sets of parameter RAMs point to the first addresses of the first and second rows of pixels in the stored image respectively, and the two sets of parameter RAMs are connected cyclically through the linking address (Linking Address), and the source address transmission mode is set to 1-dimensional and the target address mode is set to 2-dimensional. In the transmission of the EDMA channel, the end of the odd field transmission task will automatically load the parameter RAM for transmitting the even field according to the linking address of the current parameter RAM, and transmit the even field. By setting the frame index (Frame Index) value, the odd and even field data can be stored in the frame buffer in an interlaced manner, so that field synthesis can be realized without taking up additional CPU time. In addition, since the two sets of parameter RAM are connected through the link address loop, the data transmission of odd fields and even fields is continuously and alternately carried out, which forms a continuous frame data collection. After each frame of data is transferred to SDRAM through EDMA, VP1 will send an interrupt to the CPU, and the corresponding interrupt program will process the collected image data.

The transmission of large quantities of image data and the processing of complex algorithms have always been the speed bottleneck of high-speed digital image processors. From the above data transmission process, it can be seen that the EDMA function of DM642 can complete the movement of image data without interrupting the DSP algorithm processing work. While effectively solving the speed bottleneck of large-scale image data transmission, it can also allow the DSP processor core to specialize in algorithm processing, greatly improving the parallel performance of the system.

The video output function is mainly used for debugging in the early development stage in this system. In actual applications, the intermediate processed image result data can be directly written into the video FIFO through the VP2 channel in the EDMA as needed.

3.4 Implementation of communication interface functions

In the system, the UART function is realized by using the existing McBSP and EDMA through software methods without increasing the complexity of the hardware.

Synchronous serial ports rely on three separate signal lines (data, frame synchronization, and clock) to achieve data transmission, while asynchronous communication is performed on only one signal line. To achieve asynchronous transmission using a synchronous serial port, it is necessary to add start and stop bits at the beginning and end of the data so that the receiver knows when data transmission starts and stops. To implement UART functions using McBSP, in addition to correctly setting up the McBSP, it is also necessary to correctly set up EDMA and perform software processing on McBSP data transmission and reception. EDMA implements efficient data movement between memory and McBSP, and the data processing software encodes the data to be sent and decodes the received data. For details on the settings of McBSP and EDMA and the design of the encoding and decoding program, see reference [5].

4. Conclusion

The design and implementation of an image processing application platform based on DM642 is studied. The basic functions implemented include video input and output, UART interface communication with the outside world, etc. Since the software adopts modular design, specific applications can be realized by configuring different client programs according to specific functional requirements, so the system has good application prospects.

Previous article:Designing GPS System Using CoolRunner-II CPLD

Next article:Digital Voice Compression System Based on TMS320C6711

Recommended ReadingLatest update time:2024-11-16 18:00

- Popular Resources

- Popular amplifiers

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Does using a high switching frequency converter affect efficiency at higher loads?

- The use of three brackets in C language in keil: (); []; {}

- Share CCS7.3 installation steps

- MSP430 MCU Development Record (4)

- [Project source code] Mount the FAT32 file system partition of the mirrored SD card to Linux

- The STC manual is really confusing.

- A low-cost, high-precision temperature measurement solution? Come to the special live broadcast of "TI's new generation of low-power Bluetooth controllers" to learn more

- [GD32E231 Review] 1. Unboxing experience and development environment setup

- STM32H750 Part 2 (QSPI Memory Map)

- Post consultation

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication

京公网安备 11010802033920号

京公网安备 11010802033920号