摘要:为了降低超声波流量检测过程中噪声对检测精度的影响,采用FPGA器件构建了FIR滤波器,并提出一种新颖的查表法替代滤波器中的乘法运算。试验结果表明,该滤波器设计方法显著降低了FPGA的片内硬件开销,提高了滤波器的运算速度,并具有良好的降噪效果。

关键词:超声波;信号;FPGA;FIR滤波器

0 引言

在超声流量检测过程中,由于环境噪声使得流量检测的精度收到了严重的影响。目前多采用软件滤波的方法,对采集回来的声波信号进行数字处理,以提高检测的精度。此类方法对硬件处理器的运算能力要求较高,而且会影响检测的实时性。随着微电子技术的不断进步,FPGA的容量和处理速度已有了飞跃性的提高。特别是在数字信号处理方面,其性能已经超过了某些专用的信号处理芯片。本文在的超声波流量检测信号采样处理电路中,采用FPGA实现了声波信号的高速缓存和FIR滤波器,不仅达到了预期的消噪效果,而且提高了系统运行速度和集成度。下面将介绍FIR滤波器的具体实现过程。

1 数字滤波原理与设计

FIR数字滤波器的特性可以用它的系统转移函数或差分方程来描述。一般地,线性是不变离散系统的差分方程,可表示为:

式中:zr,pk分别为H(z)的M个零点和N个极点,它们由系统的形式和各系统参数ak,br所决定。FIR滤波器都是非递归形式的滤波器。

此系统的输出只与输入x(n),x(n-1),…有关,而与系统过去的输出y(n-1),y(n-2),…无关,此即非递归滤波器。

滤波器设计采用Matlab中的FDA Tool计算带通滤波器系数。滤波器采用Kaiser窗函数设计,采样频率为40 MHz,窗上下截止频率分别为3 MHz和7 MHz。由此得到的滤波器系数为:

2 FIR滤波器的FPGA实现

由式(4)可知,FIR滤波器的数学表达式就是卷积运算,也就是做乘加运算。例如,一个M阶的FIR滤波器的输出是输入样本的M个依次值的加权和,加权系数就是此滤波器的单位冲激响应值。对于上节设计的10阶线性FIR滤波器,可以得到:

这样,10阶FIR滤波器的结构可以描述为:输入样本x(n)经过10阶移位寄存器延迟后得到10个具有不同延迟的抽头,将对称的抽头值相加后再与相应的权系数相乘,5个乘积相加就得到滤波器的输出值。滤波器结构如图1所示。

[page]

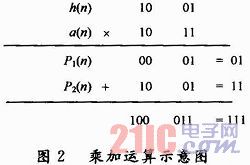

There is a multiplication operation between the filter tap and the weight coefficient. In hardware implementation, the multiplication operation is a very complex operation. It not only takes up a lot of hardware resources, but also has a slow operation speed. In order to improve the operation speed, the lookup table in the FPGA logic unit (LE) is used to implement the lookup operation instead of the multiplication operation. For the convenience of explanation, the 4th order filter is taken as an example, and the data is a 2-bit binary integer. Assume a(1)=01, a(2)=11, h(1)=10, h(2)=01, and the multiplication and addition operation between the weight coefficient and the tap is shown in Figure 2.

In Figure 2, P1(n) is the product of the low bit of the tap and the weight coefficient, and P2(n) is the product of the high bit of the tap and the weight coefficient, which is referred to as the unit product. The conventional calculation order is to first shift and add the corresponding items of P1(n) and P2(n) in the vertical direction, and then add the results in the horizontal direction. However, it can be seen from the figure that the results are the same when P1(n) and P2(n) are first added in the horizontal direction and then shifted and added in the vertical direction. In the second order, P1(n) and P2(n) are the product of a certain bit of h(n) and a(n), and for the designed FIR filter h(n) is fixed, so that P1(n) or P2(n) can be found by looking up a table through a certain bit combination of a(n), and summing can be achieved in the horizontal direction. As shown in Table 1, a1(n) represents the low bit combination of a(n), and the unit product P1 represents the corresponding sum of weight coefficients.

For the high-order combination of a(n), the unit product P2 can establish the same combination table. Shift and add P1 and P2 to get the output result of the filter. In this example, 2-bit binary weight coefficients and input samples are used. For high-precision weight coefficients and input samples, it is just a matter of adding more unit products P3, P4, etc.

In actual operation, the FIR filter based on FPGA is completed in three steps. The first step is to shift and delay the input signal x(n) to form an n-order tap, and then add the mutually symmetrical taps to get the filter tap; the second step is to construct a ROM in the FPGA and perform a table lookup operation according to the filter tap generated in the previous step; finally, shift and add the table lookup operation results of all bits to get the filter output y(n).

3 Experimental results analysis

Altera's FPGA device EPF10K30 is used to implement a 10th-order bandpass FIR filter for testing. The A/D sampling frequency is 40 MHz, the accuracy is 12 bits, and the sound wave center frequency is 5M-Hz. The original sound wave signal obtained by A/D sampling is shown in Figure 3. The sound wave signal after being processed by the FIR filter is shown in FIG4 .

The experimental results show that the FIR filter implemented by FPGA effectively weakens the noise interference and provides reliable data for later processing on the basis of ensuring real-time performance.

4 Conclusions

The FIR filter based on FPGA is used to improve the integration of hardware circuits and achieve good noise reduction effect for the noise in ultrasonic signals. In the process of hardware implementation, the table lookup method is used to replace the multiplication operation in the filtering process, which saves the occupied on-chip resources and improves the processing speed. At the same time, due to the use of parallel hardware algorithms, its processing speed is much higher than the program processing speed on CPU or DSP.

Previous article:Design of synchronous digital multiplexing of PCM3032-channel system signals based on FPGA

Next article:Low power controller and high DC voltage interface connection solution

Recommended ReadingLatest update time:2024-11-16 15:43

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- EEWORLD University ---- Yunlong 51 MCU video tutorial

- Several LM386 audio amplifier circuits shared

- MSP430G2553 button interrupt configuration

- Thank you for being my confidant

- Suspicious signal from outer space

- Download gift: USB Type C related development and test materials, read it when you have nothing to do, and you will become a master by accident

- Qorvo explains WIFI and 5G clearly

- SPIN3201 (STSPIN32F0) three-resistance control board: FOC motor drive schematic/code/debugging documents and other detailed information...

- Should segment display screens be backlit? How to add it?

- Installation and setup of CCS StarterWare, successfully compiling a project with CCS7.3

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号