USB 3.0 has a transmission rate of up to 5Gbit/s, and the power bus has a maximum output current of up to 900 mA. Therefore, the prevention of circuit electrical transients and overcurrent faults is extremely important. Designers must carefully select appropriate thermistors (PTCs) and electrostatic discharge (ESD) solutions to ensure signal integrity and reduce the risk of system failure.

Since the Universal Serial Bus (USB) specification was released in 1996, more than 3.5 billion USB-connected devices for computer peripherals have been shipped as of 2012. In 2010, when the first batch of devices supporting the USB 3.0 specification were launched, sales reached about one million units, and in 2012 it increased to about five million units, showing that the market is growing rapidly.

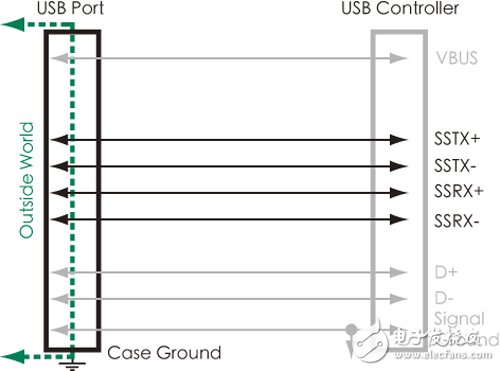

Compared to USB 2.0, USB 3.0 has four additional data channels with a transfer rate of up to 5 Gbit/s (Figure 1), and the power bus has a maximum output current of up to 900 milliamperes (mA). These new specifications, coupled with the continuous reduction in chip size, make the problem of preventing circuit electrical transients and overcurrent faults more important and complex, because at high-speed transmission, even a small electrostatic discharge (ESD) and short circuit accident will cause serious damage to the system.

Figure 1 USB 3.0 adds dual differential data pairs to achieve a high-speed transfer rate of 5Gbit/s.

Since chip sensitivity, signal integrity and system reliability are all of great concern to system designers, parasitic capacitance, low clamping voltage and low resistance on USB 3.0 systems have become key indicators for circuit protection component selection. Since USB 3.0 power lines can allow for greater current flow, current protectors can have lower resistance and are also critical in ensuring low voltage drops. The key to a successful design is to master protection technologies such as thermistors (PTCs), varistors and ESD solutions. This article will explain in detail the design factors that must be considered.

USB 3.0 is faster than ever, and circuit protection is more challenging

The most important physical change from USB 2.0 to USB 3.0 is the introduction of two differential data, SSRX+/SSRX and SSTx+/SSTx, and maintaining the parallel operation mode with the existing D-/D+ data bus, which allows full-duplex data transmission at the same time, improving the problem that the USB 2.0 bus can only transmit in single duplex mode. In addition, USB 3.0 also increases the current on the power bus from 500 mA to 900 mA, expanding the options for powering external devices and no longer requiring additional power supply solutions.

As USB 3.0 introduces additional differential data, it triggers more ESD protection needs. The previous method of protecting each individual data line with separate components is no longer sufficient to protect its circuit. The challenge facing engineers is to find a better ESD and voltage transient protection solution so that sensitive data lines can be protected without adding signal distortion capacitors. At present, the industry mostly adopts new semiconductor array ESD protection devices placed directly in the data pair to protect traditional USB 2.0 data lines and additional USB 3.0 data lines at the same time.

At the same time, the USB 3.0 specification 11.4.1.1.1 stipulates that for safety reasons, the host and all self-powered hubs must implement overcurrent protection. The hub must detect overcurrent conditions and report them to the USB control software. The overcurrent limiting mechanism must reset itself without user intervention. Polymer PTCs and solid-state switches can be used as one of the methods for overcurrent limiting.

According to the UL60950-1 standard, USB 3.0 may also require additional overcurrent protection functions. Although the USB bus transceiver chip or power management chip already provides some current limiting functions, when the chip does not include current limiting or additional protection functions, circuit designers must design a current limiting PTC for the power bus.

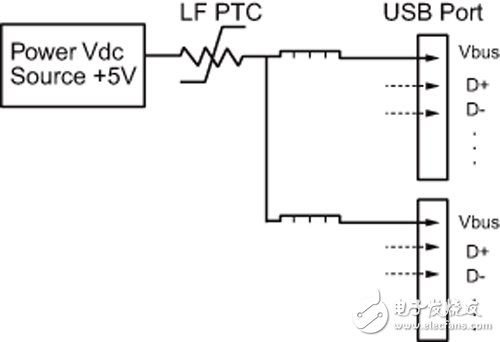

Installing a polymer PTC on the power busbar can limit the current in the event of a short circuit and prevent overcurrent damage caused by a sudden short circuit. It can also help achieve the requirements of Section 2.5 (Limited Power Source, Table 2B) of the UL60950-1 standard, limiting the short-circuit current to less than 8 amps within 5 seconds.

The overcurrent protection specification for USB hub applications and USB 3.0 states in clause 11.4.1.1.1 that if the total current of the downstream ports exceeds a predetermined value, the overcurrent protection circuit can eliminate or reduce the power of the affected downstream ports. The default value cannot exceed 5 amps and must be sufficiently greater than the maximum allowed port current or the transient current of the time delay (such as during startup, dynamic connection or reconfiguration) to achieve overcurrent protection.

PTC is responsible for protecting USB 3.0 ports. There is a lot of knowledge in selecting specifications

Figure 2 shows a PTC solution for a multi-port hub configuration, while Table 1 shows the recommended PTC components for single-port and dual-port ganged configurations and lists the required PTC solutions for the new USB Battery Charging Specification Version 1.2.

Figure 2: USB 3.0 multi-port hub configuration architecture

When selecting a PTC for USB port protection, several key parameters must be considered, including the maximum current that must support 900 mA, the operating temperature of the PTC location, the trigger speed, and the DC resistance. All PTCs in Table 1 can protect USB 3.0 ports with a maximum current of 900 mA and will not trip even if the maximum operating temperature reaches 60°C.

Since rapid temperature changes may reduce the trigger rate of the PTC, this is also an important aspect in the PTC selection process. Designers should consider incompatible USB 3.0 devices and load currents of 900 mA when selecting PTCs, so that the PTC has a maximum available current of more than 900 mA at the highest operating temperature. Otherwise, the PTC may trigger incorrectly.

Each PTC must also trip for a short circuit fault at 8 amps in less than 5 seconds, so it is important to comply with the UL60950-1 limited power source specification and the USB 3.0 specification current limit of 5 amps.

The final critical parameter for selecting the most appropriate PTC is DC resistance. As USB 3.0 now provides a maximum current of 900 mA, the power dissipation in the circuit must be further reduced. In addition, the voltage drop across the components of the power bus must also be reduced, especially when the circuit resistance budget is very tight.

In general, the main goal of selecting a PTC is to ensure that the current device can withstand at least 900 mA at the highest temperature. For example, if 60°C is set as the worst design temperature, a single-port application should choose a solution with the smallest size and the maximum required current of 0.95 amps, such as the first solution in Table 1. If a PTC is used to protect two USB 3.0 ports, the third solution in Table 1 is a good choice because it can maintain a current of 2.19 amps at 60°C, meeting all safety considerations.

Enhanced USB 3.0 circuit protection requires external ESD components

The additional data lines in USB 3.0 provide more possible entry channels for electrical transients and will also be subject to greater ESD threats. Although modern chips often have a certain degree of ESD self-protection function (usually in the range of 500~2kV), it is still insufficient for USB 3.0 circuits, so additional ESD protection components must be introduced.

The level of electrostatic protection is graded according to the MIL-STD HBM model with a 1,500 ohm (Ω) discharge resistor. In the MIL-STD model, a 2kV pulse is equivalent to a 330 ohm discharge resistor and a voltage of 500 volts based on the IEC 61000-4-2 model (Figure 3). The current human body discharge model (HBM) available pulse is one-fourth of the IEC model available at the same transient voltage. When an electrostatic discharge incident occurs, the voltage is often as high as 15kV or even higher, which will cause software failure, potential damage to the circuit or catastrophic failure. Therefore, additional ESD protection is a necessary condition to improve the survivability of modern interface ports.

Figure 3 IEC 61000-4-2 ESD current waveform

To determine the external ESD accident prevention system, the industry has developed several test standards, among which IEC 61000-4-2 is the most widely recognized. This standard defines the test specifications for ESD in different environments and installation conditions. Under this specification, today's USB 3.0 ports must withstand at least 8kV contact discharge, meeting the requirements of the fourth level of IEC 61000-4-2.

USB 3.0 has a higher data rate, so it is particularly important to pay attention to the current capacity of the components to protect the circuit. System designers must also pay attention to many important parameters when selecting ESD protection components, including dynamic resistance, clamping voltage, breakdown voltage, parasitic capacitance, maximum ESD capability, multi-pulse capability, package shape, impedance or leakage current in the off state, device circuit configuration and layout flexibility, etc.

At present, there are several different ESD suppression technologies on the market, such as multilayer ceramic varistors (MLV), polymer ESD suppressors and semiconductor ESD suppression technologies. Whether the right components are selected will determine the design reliability of the USB 3.0 port. Since the capacitance, clamping voltage and dynamic resistance of ESD protection components are the most important, some protection component manufacturers have realized products that improve signal integrity with minimum parasitic capacitance, while some products also maximize the clamping performance, but at the cost of high capacitance.

For example, transient voltage suppression (TVS) diodes and diode arrays have low dynamic resistance, provide excellent clamping performance, and maintain very low parasitic package capacitance. Figure 4 shows the clamping performance of silicon solutions compared to MLV ESD protection technology, with the silicon-based solution having a lower clamping voltage.

Figure 4 Comparison of clamping performance between silicon resistors and varistors

TVS diode arrays provide multi-channel ESD protection solutions (Figure 5), becoming the best choice for USB 3.0 protection. This type of component can absorb transient currents and discharge currents, while clamping voltage levels through avalanche or Zener diodes. Figure 6 shows the architecture of the USB 3.0 electrostatic protection solution.

Figure 5 Schematic diagram of TVS diode array protecting USB 3.0 circuit

Figure 6 shows the architecture of the USB 3.0 electrostatic protection solution;

USB 3.0 circuit protection components are also very important to maintain data integrity. Any additional capacitance can cause signal distortion and reduce signal reliability. The main method to test the effect of the parasitic capacitance of the ESD suppressor on signal integrity is to perform an eye diagram test. This test requires repeated sampling of the digital signal and displaying the eye diagram on an oscilloscope to define acceptable signal quality and compliance.

Previous article:High Input IP3 Mixer Enables Rugged VHF Receiver

Next article:IC Troubleshooting and Failure Analysis: Find the Facts and Avoid Guesswork

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Ultra-wideband technology: the nemesis of shadows and blind spots in wireless technology

- Qorvo Online Design Conference-The new Wi-Fi 6 standard is changing the connectivity environment

- BLDC back EMF is a bit weird

- EEWORLD University Hall----Boost and Buck-Boost DCDC Converters Help Wireless Charging Design

- How do I set the impedance of the differential line in ALTIUM19?

- EEWORLD University Hall----Live Replay: Introduction to Keysight's New Optical Communication Test Solution

- A complete list of filter circuits, save it for future use!

- How to choose FPGA development board

- Let’s discuss: When you make PPT, do you make the template yourself or download it from the Internet?

- TI points exchanged for E coins, but not received

Raspberry Pi Development in Action (2nd Edition) ([UK] Simon Monk)

Raspberry Pi Development in Action (2nd Edition) ([UK] Simon Monk)

京公网安备 11010802033920号

京公网安备 11010802033920号