Comprehensive understanding of the principles and applications of ESD protection structures in cmos circuits

Source: InternetPublisher:无人共我 Keywords: esd protection analog circuit cmos circuit Updated: 2021/06/25

ESD (electrostatic discharge) is one of the most serious failure mechanisms in CMOS circuits. In severe cases, it can cause the circuit to burn itself out. This paper discusses the necessity of ESD protection for CMOS integrated circuits, studies the design principles of ESD protection structures in CMOS circuits, analyzes the layout requirements of this structure, and focuses on the design requirements of ESD protection structures in I/O circuits.

1 Introduction

Electrostatic discharge can bring destructive consequences to electronic devices and is one of the main causes of integrated circuit failure. With the continuous development of integrated circuit technology, the characteristic size of CMOS circuits continues to shrink, the gate oxide thickness of the tube is getting thinner and thinner, the area scale of the chip is getting larger and larger, and the current and voltage that the MOS tube can withstand are getting smaller and smaller. The peripheral usage environment has not changed. Therefore, in order to further optimize the anti-ESD performance of the circuit, how to make the effective area of the whole chip as small as possible and meet the ESD performance reliability requirements without adding additional process steps has become a major consideration for IC designers. .

2 ESD protection principles

The design purpose of the ESD protection circuit is to prevent the working circuit from becoming a discharge path of ESD and being damaged, and to ensure that if ESD occurs between any two chip pins, there will be a suitable low-resistance bypass to introduce the ESD current into the power line. This low-resistance bypass must not only absorb ESD current, but also clamp the voltage of the working circuit to prevent damage to the working circuit due to voltage overload. When the circuit is working normally, the anti-static structure does not work. This requires the ESD protection circuit to have good working stability and be able to respond quickly when ESD occurs. While protecting the circuit, the anti-static structure itself cannot be damaged. , the negative effects of the antistatic structure (such as input delay) must be within acceptable limits and prevent latch-up of the antistatic structure.

3 Design of ESD protection structure for CMOS circuits

Most of the ESD current comes from outside the circuit, so the ESD protection circuit is generally designed next to the PAD and inside the I/O circuit. A typical I/O circuit consists of an output driver and an input receiver. ESD is introduced into the chip through the PAD, so all devices in the I/O that are directly connected to the PAD need to establish a parallel ESD low-resistance bypass to introduce the ESD current into the voltage line, and then distribute it to each pin of the chip through the voltage line. Reduce the impact of ESD. Specific to the I/O circuit, it is the output driver and input receiver connected to the PAD. It must ensure that when ESD occurs, a low-resistance path parallel to the protection circuit is formed to bypass the ESD current and can immediately and effectively clamp the protection circuit. Voltage. When these two parts are working normally, they do not affect the normal operation of the circuit.

Commonly used ESD protection devices include resistors, diodes, bipolar transistors, MOS tubes, thyristors, etc. Since MOS tubes have good compatibility with CMOS processes, MOS tubes are often used to construct protection circuits.

The NMOS transistor under CMOS process conditions has a lateral parasitic npn (source-p-type substrate-drain) transistor. This parasitic transistor can absorb a large amount of current when it is turned on. This phenomenon can be used to design a protection circuit with a higher ESD withstand voltage value in a smaller area. The most typical device structure is gate-grounded NMOS (GGNMOS, GateGroundedNMOS).

Under normal operating conditions, the NMOS lateral transistor does not conduct. When ESD occurs, an avalanche occurs in the depletion region of the drain and substrate, accompanied by the generation of electron-hole pairs. A portion of the generated holes is absorbed by the source, and the remainder flows through the substrate. Due to the existence of substrate resistance Rsub, the substrate voltage increases. When the PN junction between the substrate and source is forward biased, electrons are emitted from the source into the substrate. These electrons are accelerated under the action of the electric field between the source and drain, resulting in collision ionization of electrons and holes, thereby forming more electron-hole pairs, which increases the current flowing through the npn transistor, and ultimately causes the NMOS transistor to undergo secondary ionization. Once the breakdown occurs, the breakdown at this time is no longer reversible, and the NMOS tube is damaged.

In order to further reduce the voltage at both ends of the NMOS on the output driver during ESD, a resistor can be added between the ESD protection device and GGNMOS. This resistor cannot affect the working signal, so it cannot be too large. Polycrystalline silicon (poly) resistors are usually used when drawing layouts.

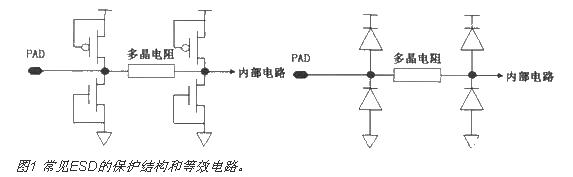

Only using level one ESD protection, the tubes inside the circuit may still be broken down when the ESD current is large. When GGNMOS is turned on, due to the large ESD current, the resistance on the substrate and the metal connection cannot be ignored. At this time, GGNMOS cannot clamp the input receiving terminal gate voltage because the voltage of the input receiving terminal gate silicon oxide layer reaches the threshold. The breakdown voltage is the IR voltage drop between the GGNMOS and the input receiver substrate. To avoid this situation, a small size GGNMOS can be added near the input receiving end for secondary ESD protection and used to clamp the input receiving end gate voltage, as shown in Figure 1.

When drawing the layout, attention must be paid to placing the secondary ESD protection circuit close to the input receiving end to reduce the resistance of the substrate and its connections between the input receiving end and the secondary ESD protection circuit. In order to draw a large-sized NMOS tube in a smaller area, it is often drawn in the shape of a finger in the layout. The design rules of I/OESD should be strictly followed when drawing the layout.

If the PAD is only used as an output, there is no need for a protective resistor and an NMOS gate shorted to ground. The large-sized PMOS and NMOS devices in the output stage themselves can be used as ESD protection devices. Generally, the output stage has double protection rings, so that Prevent latch-up from occurring.

When designing the ESD structure of the full chip, pay attention to the following principles:

(1) The peripheral VDD and VSS traces should be as wide as possible to reduce the resistance on the traces;

(2) Design a voltage clamping structure between VDD-VSS and provide a direct low-impedance current discharge channel from VDD-VSS when ESD occurs. For circuits with a larger area, it is best to place one such structure around the chip. If possible, placing multiple VDD and VSS PADs around the chip can also enhance the ESD resistance of the overall circuit;

(3) The power and ground traces of the peripheral protection structure should be separated from the internal traces as much as possible, and the peripheral ESD protection structure should be designed as uniformly as possible to avoid ESD weak links in the layout design;

(4) The design of the ESD protection structure must take into account the circuit's ESD performance, chip area, and the impact of the protection structure on circuit characteristics such as input signal integrity, circuit speed, output drive capability, etc. The design also needs to consider process tolerances. , to optimize the circuit design;

(5) In some circuits actually designed, sometimes there is no direct VDD-VSS voltage clamping protection structure. At this time, the voltage clamping and ESD current discharging between VDD-VSS mainly utilize the well and the entire circuit of the whole chip. The contact space of the substrate. Therefore, in the peripheral circuit, it is necessary to increase the contact between the well and the substrate as much as possible, and the N+P+ spacing should be consistent. If there is space, it is best to add a VDD-VSS voltage clamp protection structure next to and around the PAD of VDD and VSS. This not only enhances the ESD resistance in VDD-VSS mode, but also enhances the I/O I/O mode. anti-ESD capability.

Generally speaking, as long as the above general principles are followed and the chip area is compromised, the anti-ESD voltage of sub-micron CMOS circuits can reach more than 2500V, which can already meet the ESD reliability requirements of commercial and civilian circuit designs.

For the ESD structure design of deep sub-micron ultra-large-scale CMOS IC, conventional ESD protection structures are usually no longer used. Usually, most Foundry production lines with deep sub-micron processes have their own peripheral standard ESD structures, and have strict standard ESD structures. Design rules, etc., the designer only needs to call its structure, which allows the chip designer to focus more on the design of the function and performance of the circuit itself.

4 Conclusion

ESD protection design is becoming more and more difficult with the improvement of CMOS technology level. ESD protection is no longer just an ESD protection design issue for the input pin or output pin, but an electrostatic protection issue for the entire chip.

Each I/O circuit in the chip needs to establish a corresponding ESD protection circuit. In addition, the entire chip must be considered holistically. Using a whole-chip protection structure is a good choice and can also save I/OPAD costs. The area of the ESD component.

- This article will tell you the hard requirements of operational amplifiers

- How to calculate the value of capacitors in parallel?

- Share an interesting LED decoration project

- Share a Motorola amplifier circuit

- How to build a triangle wave generator using an op amp and discrete components

- Tutorial on building a NOT gate using BJT transistors

- LED Night Light

- Circuit diagram of an example of differential and integral circuits

- A practical automatic electronic welcome circuit

- Sunday Reminder

- Do you know the difference between analog circuits and digital circuits?

- How to read amplification circuit diagram

- Capacitive three-point sine wave oscillation circuit

- Transistor circuit diagram explanation

- How to judge whether the thyristor is good or bad by triggering circuit

- Power amplifier circuit diagram

- Low frequency voltage amplifier circuit diagram

- Analog circuit corrector circuit diagram

- Police car sound and light analog circuit

- School bell analog circuit

京公网安备 11010802033920号

京公网安备 11010802033920号