Analog Input

Take the analog input signal of the ADC seriously and try to keep it clean. "Useless input" usually leads to "digital useless output". The analog signal path should be kept away from any fast switching digital signal lines to prevent noise from coupling into the analog path from these digital signal lines.

Although the simplified block diagram shows single-ended analog inputs, differential analog inputs are often used on high-performance ADCs. Driving the ADC differentially provides greater common-mode noise rejection and generally achieves better ac performance due to smaller on-chip signal swings. Differential drive is typically implemented using a differential amplifier or transformer. Transformers can provide better performance than amplifiers because active amplifiers introduce additional noise sources that affect overall performance. However, if the signal being processed has a dc component, transformers with dc blocking properties cannot be used. The noise and linearity performance of the driver amplifier must be considered when designing the pre-driver circuit. It is important to note that because high-performance ADCs typically have very high input bandwidths, filtering directly at the ADC input pins can reduce the amount of broadband noise that is mixed into the baseband.

Reference input

The reference input should be treated as another analog input and must be kept as clean as possible. Any noise on the reference voltage (VREF) is indistinguishable from noise on the analog signal. The required decoupling capacitors are specified in the data sheet of the general ADC. These capacitors should be placed as close to the ADC as possible. In order to save board area, PCB designers sometimes place decoupling capacitors on the back of the PCB, which should be avoided as much as possible because the inductance of the vias will reduce the decoupling performance of the capacitors at high frequencies. VREF is usually used to set the full-scale range of the ADC, so reducing the VREF voltage value will reduce the LSB value of the ADC, making the ADC more sensitive to system noise (the LSB value of a 1V full-scale 10-bit ADC is equal to 1V/210=1mV).

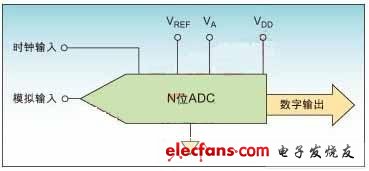

Figure 1: Typical analog-to-digital converter functional block diagram

Clock Input

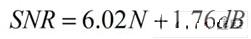

Depending on the application, the digital clock input may be as important as the analog input. There are two major sources of noise in ADCs: one is caused by the quantization of the input signal (proportional to the number of bits in the ADC), and the other is caused by clock jitter (sampling the input signal at the wrong time). According to the following formula, quantization noise will limit the maximum possible signal-to-noise ratio (SNR) value in non-oversampled ADC applications.

Where N is the number of bits of the ADC and SNR is the signal-to-noise ratio.

This makes intuitive sense: for every additional bit, the total number of ADC codes doubles, and the quantization uncertainty is reduced by half (6dB). Therefore, a 10-bit ADC can theoretically provide an SNR of 61.96dB. Any jitter on the sampling clock will further degrade the SNR according to the following equation:

where SNRj is the jitter-limited SNR, fa is the analog input frequency, and tj is the root mean square (rms) value of the clock jitter.

Digitizing a 70MHz analog signal with a sampling clock that has 8ps jitter gives a jitter-limited SNR of approximately 49dB, which is equivalent to reducing the performance of a 10-bit ADC to approximately 8 bits. The clock jitter must be less than 2ps to achieve an SNR equivalent to a 10-bit ADC. There are many second-order factors that affect SNR, but the above equation is a very good first-order approximation. Differential clocks are often used to reduce jitter.

Power Input

Most ADCs have separate power inputs, one for analog circuitry and one for digital circuitry. It is recommended to use sufficient decoupling capacitors as close to the ADC as possible. Minimize the number of PCB vias and the trace length from the ADC power pins to the decoupling capacitors to minimize the inductance between the ADC and the capacitors. Just like the reference voltage decoupling, board designers sometimes place the decoupling capacitors on the back of the PCB under the chip to save board area. For the same reason, this should also be avoided. The ADC data sheet generally provides recommended decoupling solutions. In order to achieve specific performance, power and ground are often implemented using dedicated PCB layers.

Digital Output

The ADC switching digital signal output will generate transient noise and couple back to the sensitive analog circuit part in the ADC, causing failure. Shortening the output trace length to reduce the capacitive load driven by the ADC can help reduce this effect. Placing a series resistor at the ADC output can also reduce the output current spike. The ADC data sheet usually has some design recommendations for this.

Previous article:Challenges of ADC Technology in SDR Implementation

Next article:STM32 ADC sampling period determination

Recommended ReadingLatest update time:2024-11-16 20:51

- Popular Resources

- Popular amplifiers

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- 【Warehouse temperature and humidity automatic control simulation system】2. ON Semiconductor IDE Eat (tian) melon (keng)

- What happened to Tencent?

- The communications industry was once glorious...

- nrf52832 debugging record IO pin configuration

- Add floating point operation library when CCS performs floating point operation

- Free evaluation: simulate and run AI model, and take away the Allwinner R329 AI development board worth 299 yuan

- The second part is about YOC used by RVB2601

- Adding a Raspberry Pi to a NumWorks Calculator

- Are 2G and 3G going to be phased out? Why is 3G being phased out faster than 2G?

- A strange problem occurred in a piece of code I wrote.

ESP32-S3 source code

ESP32-S3 source code 【Follow me Season 2 Episode 2】Arduion UR4 homework submission code

【Follow me Season 2 Episode 2】Arduion UR4 homework submission code MCU C language programming and Proteus simulation technology (Xu Aijun)

MCU C language programming and Proteus simulation technology (Xu Aijun)

京公网安备 11010802033920号

京公网安备 11010802033920号