Introduction

The

"

Phase-Locked Loop

" (PLL) is a basic building block of modern communication systems. PLLs are commonly used in radio receivers or transmitters, primarily to provide the "Local Oscillator" (LO) function; they can also be used for clock signal distribution and noise reduction, and are increasingly used as a clock source for high sampling rate analog-to-digital (A/D) conversion.

As the size of functional devices in integrated circuit processing shrinks, the supply voltage of devices is also decreasing, including the power supply used by PLL and other mixed-signal functions. However, the practical technical requirements of the key component of PLL, the "voltage-controlled oscillator" (VCO), have not been greatly reduced. Many high-performance VCO designs are still implemented using discrete circuits and may require a supply voltage of up to 30 V. This poses a challenge to today's PLL or RF system designers: how to interface low-voltage PLL ICs with high-voltage VCOs. Level-shifting interfaces are usually implemented using active filtering circuits, which will be discussed below. Welcome to reprint, this article comes from Electronics Fans Network (http://www.elecfans.com)

This article will explain the basic principles of PLLs, examine the current state of the art in PLL design using high-voltage VCOs, discuss the pros and cons of typical architectures, and introduce some alternatives to high-voltage VCOs .

PLL Basics

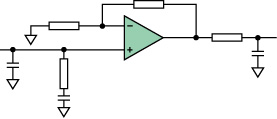

A phase-locked loop (Figure 1) is a feedback system in which a phase comparator or detector drives a VCO in a feedback loop so that the oscillator frequency (or phase) accurately tracks an applied reference frequency. Filtering circuits are usually required to integrate and flatten the positive/negative error signals and to improve loop stability. Frequency dividers are often included in the feedback path to make the output frequency (within the range of the VCO) a multiple of the reference frequency. The frequency multiple N of the frequency divider can be an integer or a fractional number, and the PLL is called an "integer-N PLL" or a "fractional-N PLL" accordingly.

Figure 1. Basic phase-locked loop.

The PLL is a negative feedback control loop, so at equilibrium the frequency error signal must be zero to produce an accurate and stable frequency, N × FREF, at the VCO output.

There are many ways to implement PLLs. Depending on the required frequency range, noise and spurious performance, and physical size, they can be all-digital, all-analog, or mixed. Currently, the common architecture for high-frequency (or RF) PLLs contains both all-digital blocks, such as feedback dividers and phase detectors, and high-precision analog circuits, such as charge pumps and VCOs. The main characteristics of mixed-signal PLLs include:

- Reference Frequency: A stable, precise reference frequency to which the RF output is phase-locked; usually derived from a crystal or temperature-controlled crystal oscillator (TCXO).

- Phase Frequency Detector (PFD): Generates a phase error signal from a reference signal and a feedback signal.

- Charge Pump: Converts the error signal into a positive/negative current pulse train proportional to the phase error.

- Loop Filter: Integrates the current pulses from the charge pump and provides a clean voltage to the VCO tuning port.

- VCO: Outputs a frequency based on the voltage (Vtune) at the tuning port. VCO has a gain of KV, expressed in MHz/V. The basic relationship between the VCO output frequency and the input control voltage is fo = fc + Kv (Vtune), where fc is the VCO offset frequency.

- N divider: Divides the output frequency by the PFD or reference frequency. This can be done simply as an integer or, increasingly, as a fractional divider (fractional-N divider). The implementation of a fractional divider is simple, just switching the divisor of the integer divider to get a fractional average (e.g., to get an average of 4.25, count to 4 three times and count to 5 once; this counts 17 pulses and generates 4 pulses, so the frequency ratio is 17/4 = 4.25). In practice, better results can be achieved using techniques used in high-resolution noise-shaping converters. Therefore, the fractional method is usually implemented in a Σ-Δ structure, which has the advantage of having fewer spurious frequencies.

A highly integrated example of current devices is shown in Figure 2, a block diagram of the ADF4350 wideband frequency synthesizer, a fractional-N PLL IC with integrated VCO, which has an output frequency range of 137.5 MHz to 4400 MHz. (The Wide Bandwidth PLL with Integrated VCO section briefly describes its functionality.)

Figure 2. ADF4350 PLL frequency synthesizer block diagram.

The main characteristics that limit PLL performance are phase noise, spurious frequencies, and lock time.

Phase noise: Equivalent to jitter in the time domain, phase noise is the manifestation of oscillator or PLL noise in the frequency domain. It is the RMS sum of the noise contributed by each device in the PLL. A charge pump-based PLL can suppress VCO noise within the loop filter bandwidth. Outside the loop bandwidth, VCO noise dominates.

Spurs: Spurious frequencies are caused by the charge pump periodically updating the VCO tuning voltage and appear at an offset frequency from the carrier by the PFD frequency. In a fractional-N PLL, the fractional divider operation also causes spurs.

Lock Time: The time required for the phase or frequency of a PLL to return to lock range when changing from one frequency to another or responding to a transient offset. It is specified as frequency or phase settling performance, and its importance as a characteristic depends on the application.

Why are VCOs still high voltage?

High-performance VCOs are one of the last electronic devices to remain unmoved by the silicon integration trend. Only a few years ago, VCOs for cell phones were fully integrated into the cell phone radio chipset. However, in cellular base stations, microwave point-to-point systems, military and aerospace products, and other high-performance applications, silicon-based VCOs are limited in their capabilities and still require discrete implementations of VCOs. Here are the reasons:

Most commercial discrete VCOs use a variable capacitance diode as the tunable element of the LC oscillator circuit. Changing the voltage across the diode changes its capacitance, thus changing the resonant frequency of the oscillator circuit.

Any voltage noise in the varactor is amplified by the VCO gain, KV (expressed in MHz/V), and converted to phase noise. To keep VCO phase noise to a minimum, KV must be as small as possible, but to achieve a reasonably wide tuning range, KV must be large. Therefore, for applications requiring both low phase noise and a wide tuning range, VCO manufacturers typically design oscillators with low gain and a large input voltage range to meet these conflicting requirements.

Narrowband VCOs typically have a voltage tuning range of 0.5 V to 4.5 V, while wideband VCOs are typically 1 V to 14 V, but can be as wide as 1 V to 28 V in some cases.

The coaxial resonator oscillator (CRO) is another special type of VCO that utilizes very low gain and a wide input tuning voltage to achieve ultra-low phase noise and is commonly used in narrowband dedicated mobile radio and land mobile radio applications.

Interfacing with a High-Voltage VCO

Most commercial PLL frequency synthesizer ICs provide a charge pump output that is capped at approximately 5.5 V; this output is insufficient to directly drive the VCO, which requires a higher tuning voltage when the loop filter uses only passive components. To achieve higher tuning voltages, an active loop filter topology must be implemented using an op amp circuit.

The simplest way to implement this structure is to add a gain stage after the passive loop filter. While easy to design, this approach has several disadvantages: the inverting op amp configuration has a low input impedance that will load the passive loop filter, changing the loop dynamics; the noninverting configuration has a high enough input impedance that it will not load the filter, but the active filter gain will amplify any noise from the op amp, which will not benefit from the filtering of the preceding passive loop filter. A better topology is to integrate the gain stage with the filter in a single active filter block. Pre-filtering is recommended to avoid overdriving the amplifier with very short current pulses from the charge pump, which could otherwise limit the input voltage rating.

Figure 3 shows two examples of suggested active filter topologies, where the prefiltering uses inverting and non-inverting gains, respectively. Note that these amplifier circuits are true time integrators, which force the PLL loop to maintain zero error at the input. Outside the loop, the topology shown may drift to the supply rails.

a. Inverting topology

b. Co-inverting topology

Figure 3. Active filter with pre-filtering

The advantage of the inverting topology is that the charge pump output can be biased at a fixed voltage, usually half the charge pump voltage (VP/2), which is the most favorable for spurious performance. Care should be taken to provide a clean bias voltage, preferably from a dedicated low-noise linear regulator such as the ADP150, and adequately decoupled as close to the op amp input pins as possible. The resistor values used in the voltage divider network should be as small as possible to reduce noise. When using an inverting topology, it is important to ensure that the PLL IC allows for PFD polarity reversal; if necessary, the op amp reversal should be offset to drive the VCO with the correct polarity. The ADF4xxx family has this feature.

The noninverting loop filter configuration does not require dedicated biasing, so this solution can be more compact. In this case, the charge pump voltage is not biased at a fixed level, but varies over its operating voltage range. Therefore, using an op amp with rail-to-rail inputs is more critical when using this type of filter. (The input voltage range requirement is described in the next section.)

Op amp selection

The choice of op amp is critical to maximizing the potential of an active filter. In addition to bandwidth, the key performance specifications to consider are:

- Noise voltage density, expressed in nV/√Hz

- Current noise, expressed in pA/√Hz

- Input bias current

- Common mode voltage range

The filter output directly affects the resulting frequency and phase; therefore, the op amp’s noise voltage density can indicate how much phase noise the active filter will add. Amplifier noise has an effect both within and outside the PLL loop bandwidth, but is most significant at the corner frequency of the loop filter, especially for amplifiers with high noise voltage density. Therefore, amplifier noise must be kept low to fulfill the mission of the amplifier and high-voltage VCO, providing low phase noise. Less than 10 nV/√Hz is a good design goal. Current noise is generally very small compared to the error current pulses, so its effect is often much smaller than that of voltage noise.

If the op amp has significant input bias current relative to the PFD output current, it may cause large spurs on the PLL output spectrum. To keep the VCO tuning voltage constant and the PLL locked, the charge pump must compensate for the bias current consumed by the op amp input during each PFD cycle. This modulates the VTUNE voltage at the PFD frequency and causes spurs around the carrier with an offset equal to the PFD frequency. The higher the input bias current, the greater the modulation of the VTUNE voltage and the higher the spur amplitude.

Common-mode voltage range or input voltage range (IVR) is another important characteristic of an op amp that is often overlooked, leading to serious problems in the end design. The IVR determines the required clearance between the maximum/minimum signal at the input pin and the positive/negative supply rails.

For early op amps operating from ±15 V supplies, the typical IVR was ±12 V. Later, the addition of slow lateral PNP input stages allowed the IVR to include the negative rail, providing single-supply capability. Although any op amp can operate from ground and positive supplies, care must be taken to ensure that the inputs are spaced from the supply rails.

For example, the popular OP27 has an IVR of ±12.3 V with ±15 V supplies. This means that the input voltage needs to be at least ±2.7 V from the positive and negative rails. This limitation at the low end of the range makes the amplifier unattractive for single-supply, wide input swing applications. If a dual-supply design is used, the choice of op amps is much wider (and input bias issues are easily addressed). If a single-supply design is a must, use an op amp with rail-to-rail input swing (but many of these amplifiers may have higher noise voltage characteristics). Therefore, for best results, the op amp needs to have low noise voltage density, low input bias current, and rail-to-rail inputs to achieve low phase noise, low spurs, and single-supply operation. Table 1 lists some of Analog Devices' op amps and their characteristics related to the above design criteria.

Table 1. Recommended operational amplifiers for use in PLL active loop filters

| Operational Amplifier |

Voltage noise,

f = 1 kHz (nV/√Hz)

|

Current noise,

f = 1 kHz (pA/√Hz)

|

Input bias current (typical) | Input voltage range, clearance to lower supply rail (V) | VSUPPLY Maximum supply voltage, single supply (V) |

| AD820 | 16 | 0.8 | 2 pA | –0.2 | 36 |

| OP184 | 3.9 | 0.4 | 60nA | 0 | 36 |

| AD8661 | 12 | 0.1 | 0.3 pA | –0.1 | 16 |

| OP27 | 3 | 0.4 | 10 nA | +2.7 | 36 |

| AD8099 | 2 | 8 | 100 nA | +1.3 | 12 |

The choice of op amp depends on the application. If the PFD spurs are far from the loop bandwidth (such as in a fractional-N frequency synthesizer), a bipolar junction transistor input (BJT) op amp such as the OP184 or OP27 can be used. The loop filter will do a good job of attenuating the PFD spurs caused by the high input bias current of the BJT, and the PLL can take advantage of the low noise voltage density of the BJT op amp.

If the application requires a smaller PFD to loop bandwidth ratio (for example, in an integer-N frequency synthesizer), the noise and spurious levels should be compromised; the AD820 and AD8661 may be better choices.

It is worth noting that while active filters tend to increase the noise of the PLL, they can act as a buffer and have performance advantages over passive filters in some specific applications. For example, if the leakage current at the VCO tuning port is high, resulting in high PFD spurs, an op amp can be used to reduce the spur level. The low impedance output of the op amp can easily compensate for the tuning port leakage current.

Design Example

Consider an example where the LO specifications are as follows:

- Octave tuning range: 1000 MHz to 2000 MHz

- Phase noise requirement: –142 dBc/Hz (1 MHz offset)

- Spurious: less than –70 dBc

- Channel spacing: 250 kHz

- Lock time: less than 2 ms

- Single power supply: 15 V or 30 V

To operate over the 1-GHz band while meeting the phase noise requirement, a high-voltage VCO and active loop filter are necessary. The phase noise and spurious characteristics, along with the single-supply limitation, will determine the choice of op amp. To meet the spurious requirement, the op amp must have low input bias current, and to achieve the best phase noise performance, the op amp must have low voltage noise. A JFET-input op amp was chosen that can balance these two requirements, such as the AD8661, which has an input bias current of 0.3 pA and a voltage noise of 12 nV/√Hz. This device can also handle the single-supply requirement. The RFMD UMS-2000-A16 VCO was chosen to meet the octave range requirement.

When starting a design, it is best to simulate using the ADIsimPLL™ tool that supports active filter topologies. Figure 3 shows two recommended filter types; ADIsimPLL also supports other configurations.

The PLL selects the ADF4150, which has both integer and fractional operating modes and provides 2/4/8/16/32 output divider options to cover continuous frequencies from 2 GHz to 31.25 MHz. The ADF4150 is similar to the ADF4350 shown in Figure 2, but the former allows the selection of an external VCO for applications that need to meet more stringent phase noise requirements. During the simulation, the PLL loop filter was set to 20 kHz in order to reduce the noise contribution of the op amp while keeping the PLL lock time less than 2 ms.

Figure 4 shows the noise (dBc) vs. frequency offset for the simulated and measured systems using the ADF4150 PLL, UMS VCO, and AD8661-based filter. Both curves show a peak noise of –90 dBc at about 20 kHz due to the noise added by the active loop filter, but the target of –142 dBc/Hz at 1 MHz offset is still achieved. To reduce the in-band noise, either use a lower noise op amp such as the OP184 or OP27, but with higher spurs, or reduce the PLL loop bandwidth to less than 20 kHz.

Figure 4. ADIsimPLL simulated vs. measured performance: AD8661 used as an op amp in a PLL active filter.

Figure 5 shows that the performance is improved by about 6 dB when using the OP27. In this case, the spurs are not significantly increased because the loop bandwidth is relatively narrow. Further reduction of the bandwidth can improve the phase noise at offsets below 100 kHz, but the PLL lock time will increase. All of these trade-offs can be tested using ADIsimPLL simulations before entering a lab design.

Figure 5. PLL measured performance comparison using the AD8661 and OP27 in an active loop filter.

Breaking News: High-Voltage PLLs

The above discussion has focused on the use of active filters to interface low-voltage PLL devices with high-voltage VCOs. However, high-voltage PLLs are now available, making active filters less necessary. For example, the ADF4113HV PLL has an integrated high-voltage charge pump and a normalized phase noise floor of –212 dBc/Hz. For this device, the PLL charge pump output can be as high as 15 V, so a simpler passive filter can be used before the VCO.

Welcome to reprint, this article comes from Electronics Fans Network (http://www.elecfans.com)

The high voltage PLL family will continue to expand and will soon include devices with a maximum voltage of 30 V, as well as fractional-N PLLs with high voltage charge pumps. For product updates and new product information, visit the PLL website.

Wide Bandwidth PLL with Integrated VCO

Alternatively, the active filter and high voltage VCO combination can be replaced with a fully integrated high performance PLL such as the ADF4350 shown in Figure 2. In this case, the VCO is integrated on-chip. The trade-off between wide tuning range and low phase noise described above can be avoided by taking a multiband VCO approach. The ADF4350 integrates three independent VCOs on-chip, each with 16 overlapping subbands for a total of 48 subbands. An automatic calibration routine is initiated each time the frequency is updated to select the appropriate VCO subband.

This really shows the advantage of moving from discrete VCO design to a silicon solution: very high integration in a very small area, which makes the design more flexible. For example, the ADF4350 also integrates a programmable output divider stage that can cover frequencies from 137.5 MHz to 4.4 GHz, which is very attractive to radio designers who want to use the same design for multiple frequencies and standards.

The ADF4350 is available in a 5 mm2 LFCSP package, compared to the 12.7 mm2 standard VCO package. Performance levels are close to discrete designs; phase noise is –114 dBc/Hz at 100 kHz offset and –134 dBc/Hz at 1 MHz offset. (Return to Figure 2)

Figure 6. Voltage vs. frequency plot for 48 different frequency bands in the ADF4350 VCO.

Previous article:Low-cost, high-precision, high-resolution multiplexing system

Next article:The 2nd and 3rd order intersection of the amplifier

- Popular Resources

- Popular amplifiers

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- Rambus Launches Industry's First HBM 4 Controller IP: What Are the Technical Details Behind It?

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- 【Repost】Thirty Practical Experiences in Switching Power Supply Design (Part 1)

- blue_nrg, how to turn off subscription function

- CC26xx product model and suffix description

- AD19, board layer, layer type, what are the uses of each? Please guide

- Melexis for you: Detailed explanation of the implementation and technical support of functional safety in semiconductor R&D. Registration for the prize-winning live broadcast is open!

- One week evaluation report~

- Six key issues when designing a universal serial bus protocol interface

- Reference book on porting from SXX32F103 to MH32F103A

- Good book recommendation! A brief review of Luo's "Basics of Power Supply Design"

- Please give me some advice, is this an amplifier impedance issue?

Introduction to the classification, application, composition and model of phase-locked loop

Introduction to the classification, application, composition and model of phase-locked loop Low-noise varactors for biasing switching regulators

Low-noise varactors for biasing switching regulators

京公网安备 11010802033920号

京公网安备 11010802033920号