1 Performance and features of MAX121 chip

The MAX121 chip is a 14-bit analog-to-digital conversion integrated circuit (ADC) with a serial interface. It contains a bottom-overflow, bottom-noise, and buried Zener voltage reference power supply with a track/hold circuit. It has fast conversion speed, low power consumption, sampling rate up to 308 ks/s, full-scale input voltage range of ±5V, and power consumption of 210 mW. Interfacing directly with the serial interfaces of most popular digital signal processors, this input can accept signal levels in TTL or CMOS with clock frequencies of 0.1-5.5MHz.

The functional block diagram of the MAX121 chip is shown in Figure 1. It has 16-pin and 20-pin modes, 16-pin is available in DIP and SO packages, and 20-pin is available in SSOP package. The characteristics are as follows:

14-bit resolution; 2.9 μS conversion time/308 ks / s throughput; 400 ns sampling time; Noise floor and low distortion: 78Db SINAD -85Db THD; ±5V bipolar input range, withstands ±15V transients voltage; 210 mW power consumption; continuous conversion mode available; 30 ppm/C, -5V internal reference source; interfaces with DSP processors; 16-pin DIP and SO packages, 20-pin SSOP packages.

Limit parameters: V DD to DGND 0.3-+6V; V SS to DGND +0.3--7V; AIN to AGND ±15V; AGND to DGND ±0.3V digital input to DGND (CS, CONVST, MODE, CLKIN, INVCLK, INVFRM); -0.3(V dd +0.3V); Digital output to DGND (SFRM, FSTRT, SCLK, SDATA) +0.3(V dd +0.3V); Continuous power consumption (TA = +70 ℃)

Strength exceeding the above limit parameters may cause permanent damage to the device. These are extreme parameters only and do not imply that the device will operate effectively under extreme parameter conditions or under any other operating conditions beyond those specified in the technical specifications. Extended operation time under extreme parameter conditions will affect the reliability of the device.

2 working circuit

MAX121 uses successive comparison technology and track/hold (T/H) circuits to convert analog signals into 14-bit serial data output codes. Its control logic interfaces easily to most microprocessors and digital signal processors (DSPs), requiring only a few passive components in most applications. The T/H circuit does not require external capacitors.

2.1 Analog input tracking and holding

Based on equivalent input circuit analysis, the sampling structure of the analog comparator of ADC is given. An internal buffer charges the holding capacitor to reduce the acquisition time required during conversion. The analog input presents a 6k input resistor and a 10pF capacitor in parallel with it.

Between conversions, the buffer input is connected to the AIN terminal through the input resistor. When conversion begins, the buffer is disconnected from the AIN terminal and the input signal is sampled. At the end of the conversion, the buffer input is connected back to AIN and the capacitor is kept tracking the input voltage. Whenever a conversion is not in progress, the T/H is in tracking mode. After the conversion begins, the holdover mode startup time is approximately 10 ns (window delay). The typical time to change in latency from one conversion to the next is 30 ps (window jitter).

2.2 Circuit clock frequency

MAX121 requires a clock compatible with TTL and CMOS levels when working, and the clock frequency ranges from 0.1-5.5 MHz. To meet the 400 ns acquisition time requirement for 2 clock cycles, the maximum clock frequency is limited to 5MHz. Due to the limitation of the internal T/H voltage drop rate, the clock frequency in all modes should not be lower than 0.1MHz.

2.3 Output data format

The conversion result is output as a 16-bit serial data stream, the first 14 bits are data bits (MSB first), and the last 2 bits are zero. The output data is in two's complement form. On the rising edge of CLKIN, data is output synchronously on the SDATA terminal.

The output data can be framed using FSTRT or SFRM output. FSTRT (normally low) goes high 1 clock cycle below MSB. The SDATA terminal outputs the MSB on the falling edge of FSTRT.

When the SFRM output (usually high when INVFRM=V dd ) becomes low, the MSB appears on the SDATA terminal. SFRM becomes high level after 16 clock cycles. The polarity of the SFRM can be reversed by connecting the input to digital ground. A minimum of 18 clock cycles per conversion is required to obtain valid SFRM output.

If there are several devices sharing the serial bus, you can refer to the data access and data retention timing in Figure 2.

3 TMS320 high-speed serial interface

3.1 Initialization after power-on

If the following conditions are met, the first conversion of MAX121 after power-on will be valid. Provides 16 clock pulses to put the T/H into tracking mode, plus a minimum time of 400 ns for data acquisition in tracking mode. Make sure the reference source has stabilized. The settling time for each 1 μF reference bypass capacitor is 0.5 ms (11ms for a 22 μF capacitor ).

3.2 Serial clock maximum rate

When interfacing with a digital signal processor, the maximum serial clock rate of the MAX121 depends on the minimum setup time required by the processor's serial data input and the maximum delay time of the ADC's clock and data. The MAX121 has two methods of reading data into the processor. CLKIN is the input clock of MAX121, and SCLK is the serial clock that shifts data into the processor, supporting asynchronous data transmission. t SU is the minimum data establishment time required by the processor's serial data input; t CD is the maximum delay time from CL KIN to SCLK of MAX121; t SC is the maximum delay time from SCLK to SDATA of MAX121. The MAX121's SCLK output drives the processor's serial interface, which removes tCD from the above agenda and allows the use of faster clock frequencies. In this case, the maximum serial clock speed is calculated by:

f CLKIN =1/2(t SU +t SC )

3.3 High-speed data serial interface

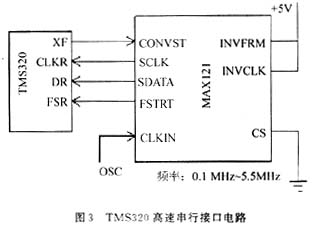

The flexibility of MAX121 allows it to be connected with various serial interfaces of Texas Instruments TMS320. The high-speed interface allows the MAX121/TM320 system to obtain the maximum data throughput rate when the MAX121 works at its fastest clock. Figure 3 shows the wiring required to complete this interface. Figure 4 is the timing diagram of the interface.

The CLKIN of MAX121 is driven by an external clock oscillator. The XF0 I/O port of TMS320 drives the MAX121 input low to start a conversion. The CLKR (receive clock) terminal of the TMS320 is configured as an input and driven by the SCLK output of the MAX121. The data at the SDATA output of the MAX 121 changes state on the rising edge of the clock, and on the falling edge of the clock, the data is latched into the DR input of the TMS320. This provides 1/2 clock cycle to meet the data setup and hold times required at the TMS320DR input. The maximum skew between the MAX121SCLK and SDATA is 65ns at +25, so 1/2 clock cycle is sufficient to meet the required setup and hold times.

The FSTRT output of the MAX121 drives the FSR input of the TMS320 to frame the data. A falling edge on the FSTRT output indicates that the MSB is ready to be latched. On the next falling clock edge, the MSB is latched in TMS320. Using this interface, TMS320 can receive 16-bit words (RLEN=01 in the TMS320 serial port overall control register), so the 14-bit data is clocked into the DSP synchronously, followed by two trailing 0s.

4 Conclusion

In recent years, with the increasing number of portable and handheld electronic products, the application of MAXIM series products has become more and more extensive. Here is a detailed introduction to the application of MAX121 chip in digital signal processing high-speed serial interface circuits. At the same time, the MAX121 integrated circuit is also widely used in fields such as language recognition and synthesis, DSP servo synthesis, and spectrum analysis.

References

1 Zheng Yuqiang, Xu Ziwen MAXIM Integrated Circuit User Manual. Beijing: People's Posts and Telecommunications Press, 1988, 1

2 Signal Processing Society of China Electronics Association (Translated). Digital Signal Processing Program Library. Beijing: Tsinghua University Press, 1988

3 Wang Jianxin. TMS320 Digital Signal Processor and Application. Nanjing: Nanjing University of Science and Technology Press, 1994, 10

Source: modern electronic technology

Previous article:

Next article:Application of MAX121 chip in high-speed serial interface circuit

- Popular Resources

- Popular amplifiers

- High signal-to-noise ratio MEMS microphone drives artificial intelligence interaction

- Advantages of using a differential-to-single-ended RF amplifier in a transmit signal chain design

- ON Semiconductor CEO Appears at Munich Electronica Show and Launches Treo Platform

- ON Semiconductor Launches Industry-Leading Analog and Mixed-Signal Platform

- Analog Devices ADAQ7767-1 μModule DAQ Solution for Rapid Development of Precision Data Acquisition Systems Now Available at Mouser

- Domestic high-precision, high-speed ADC chips are on the rise

- Microcontrollers that combine Hi-Fi, intelligence and USB multi-channel features – ushering in a new era of digital audio

- Using capacitive PGA, Naxin Micro launches high-precision multi-channel 24/16-bit Δ-Σ ADC

- Fully Differential Amplifier Provides High Voltage, Low Noise Signals for Precision Data Acquisition Signal Chain

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Motor Testing Discussion

- [RVB2601 Creative Application Development] Create an Any MP3 Player on the Internet

- Raspberry Pi Windows IoT Development (Part 1)

- Can anyone crack it? I have a network speed of tens of G and tens of kilobytes. Even if I climb over the firewall, it won't work.

- [HC32F460 Development Board Review] 03. Implementing SHELL transplantation and control based on UART function

- Detailed explanation of ADC in STM32

- The working principle of the automobile gateway system and the location of the gateway for some models

- MSP430 FRAM Microcontrollers Enable Energy Harvesting

- [RVB2601 Creative Application Development] Experience Sharing 2: Lighting in Multiple Ways, Component Learning

- E22-400TBL-01 LoRa module test version +01 unboxing

Digilent Vivado library

Digilent Vivado library Principles of Digital Communications (Gallagher)

Principles of Digital Communications (Gallagher)

京公网安备 11010802033920号

京公网安备 11010802033920号