1.1.1 ARM processor mode switching (including MRS, MSR instructions)

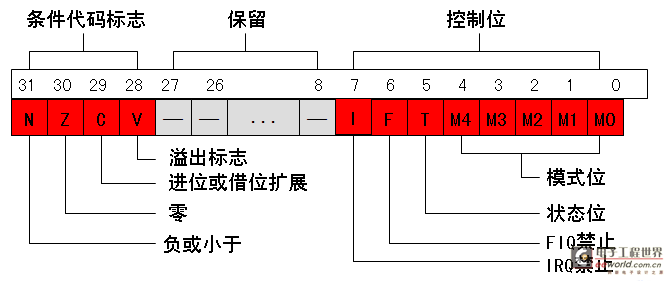

Except for user mode and system mode, all other modes have a private SPSR status register to save the execution status before switching to the mode. The reason why user mode and system mode do not have SPSR is that the CPU usually executes in user mode most of the time. When an exception or system call occurs, it will switch to other modes to save the status in user mode. When switching back to the original mode, it can directly restore the value of SPSR to CPSR. Therefore, SPSR is not required in user mode and system mode. For detailed operations, see the exception handling in the next section.The above modes are distinguished by the M[4:0] bit in CPSR, as shown in Figure 3-1:

Figure 3-1 CPSR control bit

Switch to different modes by writing corresponding data to the mode bit M[4:0]. When operating the CPSR and SPSR registers, general instructions such as mov and ldr cannot be used. Only privileged instructions msr and mrs can be used.

In ARM processors, only the MRS (Move to Register from State register) instruction can read the status registers CPSR and SPSR. The current working status of the processor can be obtained by reading CPSR. Reading the SPSR register can obtain the processor status before entering the exception (because the SPSR register is only available in exception mode).

For example:

MRS R1, CPSR; read the CPSR status register and save it in R1

MRS R2, SPSR; read the SPSR status register and save it in R2

The MRS instruction can be used to obtain the value in the status register, and then compare the value of its mode bit M[4:0] to determine the current mode. Of course, other corresponding bits can also be compared to understand the current CPU status. MRS R2, SPSR; read the SPSR status register and save it in R2

Similarly, in ARM processors, only the MSR instruction can write to the status registers CPSR and SPSR. Used in conjunction with MRS, read-modify-write operations on the CPSR or SPSR registers can be implemented, the processor mode can be switched, or IRQ/FIQ interrupts can be enabled/disabled, etc.

Since the xPSR register represents the status of the CPU, each bit has a special meaning. When writing to the xPSR status register (this usage does not exist when reading), in order to prevent misoperation and facilitate memory, the 32 bits in the xPSR are divided into four areas, each represented by a lowercase letter:

c Control domain mask psr[7..0]

x Extension domain mask psr[15..8]

s Status domain mask psr[23..16]

f Flag domain mask psr[31..24]

Note: The domain name must be lowercase letters

When writing to the corresponding area, use xPSR_x to specify the write area without affecting other bits of the status register, such as x Extension domain mask psr[15..8]

s Status domain mask psr[23..16]

f Flag domain mask psr[31..24]

Note: The domain name must be lowercase letters

enabling IRQ interrupt:

ENABLE_IRQ

MRS R0, CPSR ; Read the contents

of the CPSR register to R0 BIC R0, R0, #0x80 ; Clear the I control bit

MSR CPSR_c, R0 ; Write the modified value back to the corresponding control field of the CPSR register

MOV PC, LR ; Return to the previous function

Disable IRQ interrupts:MRS R0, CPSR ; Read the contents

of the CPSR register to R0 BIC R0, R0, #0x80 ; Clear the I control bit

MSR CPSR_c, R0 ; Write the modified value back to the corresponding control field of the CPSR register

MOV PC, LR ; Return to the previous function

DISABLE_IRQ

MRS R0 CPSR ; Read the contents of the CPSR register to R0

ORR R0, R0, #0x80 ; Set the I control bit in the CPSR

MSR CPSR_c, R0 ; Write the modified value back to the corresponding control field of the CPSR register

MOV PC, LR ; Return to the previous function

The following table lists the binary representation of different modes: MRS R0 CPSR ; Read the contents of the CPSR register to R0

ORR R0, R0, #0x80 ; Set the I control bit in the CPSR

MSR CPSR_c, R0 ; Write the modified value back to the corresponding control field of the CPSR register

MOV PC, LR ; Return to the previous function

Table 3-3 Binary representation of different working modes

| Mode Name | user | Fast interruption | Interrupt | manage | Suspension | Undefined | system |

| M[4:0] | 10000 | 10001 | 10010 | 10011 | 10111 | 11011 | 11111 |

stack_init; Stack pointer initialization function

@ undefine_stack

msr cpsr_c, #0xdb; Switch to undefined exception

ldr sp, =0x34000000; The stack pointer is the highest memory address, and the stack is a reverse stack

; The last 1M of the stack space 0x34000000~0x33f00000

@ abort_stack

msr cpsr_c, #0xd7; Switch to termination exception mode

ldr sp, =0x33f00000; The stack space is 1M, 0x33f00000~0x33e00000

@ irq_stack

msr cpsr_c, #0xd2; Switch to interrupt mode

ldr sp, =0x33e00000 ; The stack space is 1M, 0x33e00000~0x33d00000

@ sys_stack

msr cpsr_c, #0xdf ; Switch to system mode

ldr sp, =0x33d00000 ; The stack space is 1M, 0x33d00000~0x33c00000

msr cpsr_c, #0xd3 ; Switch back to management mode

mov pc, lr

Previous article:ARM processor exception handling

Next article:ARM Processor Registers

- Popular Resources

- Popular amplifiers

Recommended Content

Latest Microcontroller Articles

- Learn ARM development(16)

- Learn ARM development(17)

- Learn ARM development(18)

- Embedded system debugging simulation tool

- A small question that has been bothering me recently has finally been solved~~

- Learn ARM development (1)

- Learn ARM development (2)

- Learn ARM development (4)

- Learn ARM development (6)

He Limin Column

Microcontroller and Embedded Systems Bible

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

MoreSelected Circuit Diagrams

MorePopular Articles

- LED chemical incompatibility test to see which chemicals LEDs can be used with

- Application of ARM9 hardware coprocessor on WinCE embedded motherboard

- What are the key points for selecting rotor flowmeter?

- LM317 high power charger circuit

- A brief analysis of Embest's application and development of embedded medical devices

- Single-phase RC protection circuit

- stm32 PVD programmable voltage monitor

- Introduction and measurement of edge trigger and level trigger of 51 single chip microcomputer

- Improved design of Linux system software shell protection technology

- What to do if the ABB robot protection device stops

MoreDaily News

- Brief Analysis of Automotive Ethernet Test Content and Test Methods

- How haptic technology can enhance driving safety

- Let’s talk about the “Three Musketeers” of radar in autonomous driving

- Why software-defined vehicles transform cars from tools into living spaces

- How Lucid is overtaking Tesla with smaller motors

- Wi-Fi 8 specification is on the way: 2.4/5/6GHz triple-band operation

- Wi-Fi 8 specification is on the way: 2.4/5/6GHz triple-band operation

- Vietnam's chip packaging and testing business is growing, and supply-side fragmentation is splitting the market

- Vietnam's chip packaging and testing business is growing, and supply-side fragmentation is splitting the market

- Three steps to govern hybrid multicloud environments

Guess you like

- [New Year's Flavor Competition] + Show off your New Year's Eve dinner and see where the Coke is. If you find it, you win a prize!

- 【RPi PICO】Calculate Mandelbrot Improved Version

- How to convert PWM signal into analog signal

- Simulation design of phase-shifted resonant power supply and its synchronous rectification circuit

- A very detailed disassembly of the Joyoung soymilk maker!

- How to make a self-propelled car

- Research on WiMAX Network Application Scheme Based on IEEE 802.16e Technology

- ADI's "Basic Tutorial on Analog Electronic Devices" is available for free download!

- Asking for advice on tps65982

- What is the use of ceramic capacitors in parallel with DC motors?

5962-9553601QHA

5962-9553601QHA

京公网安备 11010802033920号

京公网安备 11010802033920号